“介紹了使用MIPS32TM4KcTM處理器作為CPU內核的高清晰度電視(HDTV)SoC平臺,著重提出了該平臺上系統總線接口(HIF)模塊的設計方案。并通過仿真和綜合實驗,驗證了該模塊能夠達到系統總體設計的要求。”

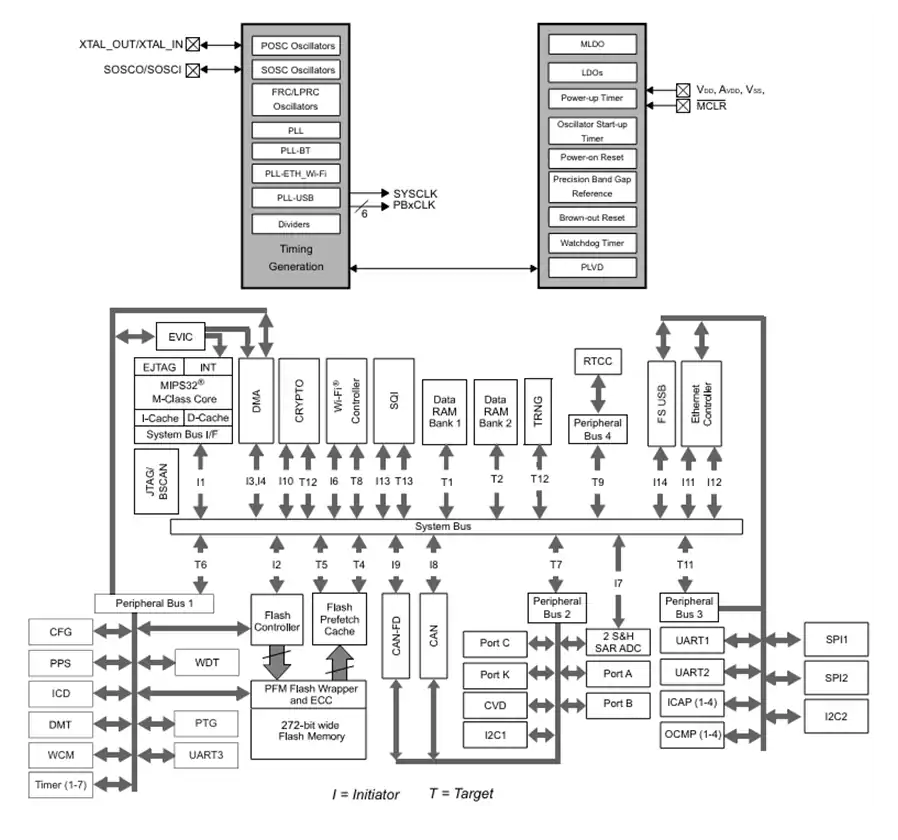

在系統級芯片(SoC)的設計當中,MIPS的RISC處理器是一種應用非常廣泛的嵌入式CPU,它具有高性能、低功耗的特點,可以很方便地集成到一個完整的片上系統之中,使開發者能夠專注于用戶IP模塊的設計。MIPS架構的處理器占據了數字機頂盒微處理器和解碼器用CPU架構市場領域的領先地位。在MIPS家族的產品當中,32位的4KcTM處理器是具有代表性的一款,它采用了MIPS32的CPU架構,支持MIPS IITM指令集。在本文介紹的SoC系統設計中,就采用了MIPS32TM4KcTM處理器作為芯片的CPU內核。

在當前的數字消費電子市場領域,基于SoC平臺的HDTV芯片是所有數字電視接收及播放設備的核心器件。SoC芯片具體到HDTV解碼系統,就是把MPEG-2解復用(DeMux)、音視頻解碼(AVD)、視頻格式轉換(VTP)、畫面后處理(OSD)以及接口I/O控制等功能模塊都集成在一塊芯片上。而要把眾多功能復雜的系統控制模塊和用戶IP模塊集成到一個芯片上并使其能夠協調工作,就必須設計好各個模塊之間的接口。本文針對高清數字電視SoC平臺的項目,提出了系統總線接口模塊(Host Bus Interface,HIF)的設計方案,并進行了仿真實驗。

HIF模塊在系統中的主要功能

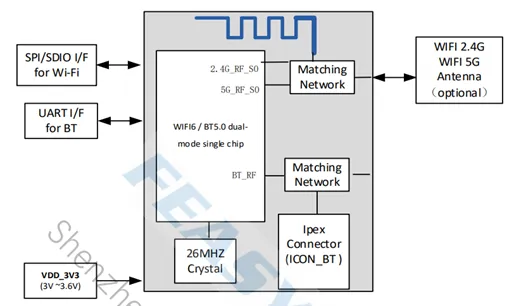

HDTV-SoC平臺是一個功能強大、結構復雜的系統,本文重點介紹了SoC架構中片上總線控制器的設計。片上總線能夠提供針對特定應用的靈活多樣的集成方法,它需要結構簡單,速度快捷,在單芯片中實現多資源互聯。HDTV-SoC系統的總線結構如圖1所示。它分為3個層次,即與MIPS處理器接口的Ec總線(EcInterface)、系統總線和外圍總線。

由圖1可見,HIF模塊在系統中所處的位置是十分關鍵的,它是系統總線(Host Bus)和各個IP模塊以及周邊I/O模塊之間的接口單元,即系統總線和外圍總線之間的橋梁,在系統中起著“承前啟后”的作用,是CPU和外部模塊之間數據交換的重要通道。具體而言,HIF模塊主要完成3大功能,分別為外部模塊W/R寄存器的設置和狀態寄存器的讀取、外部模塊雙口RAM的讀寫控制、外部模塊中斷的控制和管理。

電路功能模塊設計

由上文所述可知,HIF電路設計主要分為3個模塊:寄存器讀寫模塊,雙口RAM讀寫模塊和中斷處理模塊。

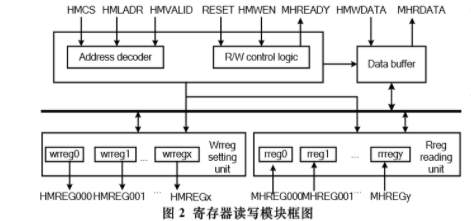

寄存器讀寫模塊

CPU和外部模塊之間進行數據交互的一個重要方式就是通過寄存器的讀寫,實現對外部模塊功能的控制和初始化。系統總線按照規定的時序讀寫HIF模塊內部的寄存器資源,這些寄存器的每個比特位以連線的方式直接與外部模塊互連。HIF模塊在接收到系統總線過來的地址和數據之后,首先進行地址譯碼,選擇相應的寄存器,再將數據寫入。圖2為該模塊的邏輯框圖。

MIPS的4Kc處理器支持猝發(burst)操作,所謂猝發操作是指在給出首地址之后,可以連續進行多個讀寫操作,而無須再給出每次操作的相應地址。在總線上,一個猝發指令與單個操作指令一樣,只占用一個時鐘周期。HIF模塊在處理猝發操作時,將一個猝發指令轉換為4個單周期指令,在轉換之后,要保證從總線上過來的寫數據與其相應的指令同步。

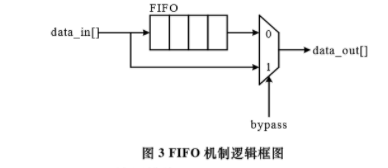

這樣在猝發操作時,從寄存器組的角度看到的寫數據與指令是同時發生的,盡管實際情況并不是這樣。而要實現這種猝發操作,就必須引入一種FIFO機制。FIFO的深度為4,這與4Kc處理器所支持的猝發長度是一致的。在系統復位之后FIFO清空,可以隨時接收總線上的猝發數據。在系統正常工作時,FIFO模塊分別通過“in”和“out”指針來指示輸入和輸出的數據,以跟蹤FIFO的使用情況。FIFO還需要用到一個“bypass”信號來確定是否旁路該模塊,這發生在單個指令操作的情況下(bypass=‘1’),這時數據是繞過FIFO而直接通向寄存器的。FIFO機制的邏輯框圖見圖3。

雙口RAM讀寫模塊

在與系統總線的接口邏輯方面,RAM讀寫模塊與寄存器讀寫模塊是類似的,這里不再贅述。不同之處在于與外部模塊的接口邏輯,寄存器讀寫模塊是采用直接連線的方式,而RAM讀寫模塊則必須滿足相應的雙口RAM的接口時序。在本設計中,選用了SMIC的0.18μm庫的雙口RAM單元作為模型。該模型的接口時序如圖4所示,包括了讀時序和寫時序兩種情況。

中斷控制模塊

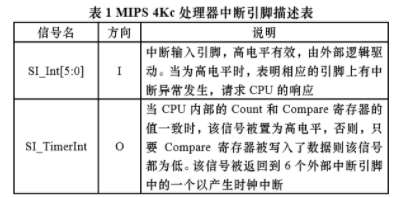

中斷控制模塊負責處理由DeMux、VD、GPIO等外部模塊的中斷源所發出的中斷,對于系統來說,如何使產生的中斷盡快得到響應是一個關鍵的問題。在圖1中可以看到MIPS4Kc處理器所提供的中斷引腳的連接情況,有關其引腳的說明如表1所示[1]。

表1 MIPS4Kc處理器中斷引腳描述表

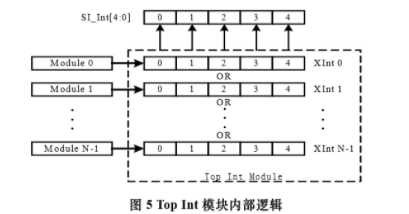

習慣將SI_TimerInt信號接到SI_Int[5]引腳,就像圖1中所顯示的那樣。這樣4Kc處理器的外部中斷引腳就剩下5根,即SI_Int[4:0]。在本設計中,將系統外部中斷分為5級,按照SI_Int[0]到SI_Int[4]的順序優先級從高到低排列。針對每個外部模塊,也將其所有的中斷源分為5級,反映到每個模塊的輸出是一個5比特的寄存器XInt[4:0],同樣,按照XInt[0]到XInt[5]的順序中斷優先級從高到低排列。假設系統有N個外部模塊,則各個模塊輸出的XInt之間相或即得到SI_Int的輸入,這些邏輯在TopInt模塊中實現,如圖5所示。

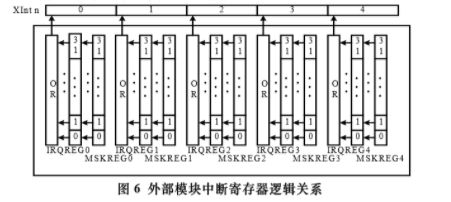

需要說明的是,TopInt模塊本身也被當作系統的一個外部模塊,系統可以對其進行與其它模塊相同的寄存器讀寫操作。這樣CPU在處理外部中斷時,就可以通過讀取XIntn寄存器的內容,追溯中斷的產生源。另外,在每一個外部模塊內部,設置5個32位的中斷請求寄存器IRQREG0~IRQREG4和5個32位的中斷屏蔽寄存器MSKREG0~MSKREG4。

當MSKREGn寄存器中的某個比特位被置“1”時,則IRQREGn寄存器中相應比特位的中斷被屏蔽。在每一個IRQREGn寄存器當中,32個比特位之間相或即得到該模塊相應XInt寄存器中的第n比特位的值。由此也可以看出,按照IRQREG0到IRQREG4的順序,中斷優先級從高到低。它們之間的邏輯關系如圖6所示。

另外,為了便于CPU的訪問,所有這些寄存器在模塊中都有編址。這樣對于任意一個中斷,最多通過兩次查詢CPU就可以獲知產生該中斷的中斷源。

仿真與綜合

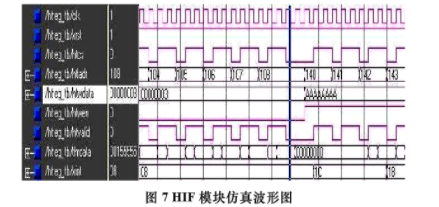

設計的仿真工作是分兩部分進行的。各模塊先單獨仿真,待波形正確后再各模塊聯調。在編制TESTBENCH時,分別在不同的文件當中處理不同的工作情況。具體到HIF模塊,仿真主要完成如下方面的驗證:寄存器的寫入和讀取、雙口RAM的寫入和讀取以及中斷的產生和獲取。在設計中,采用VHDL語言編寫代碼,以及Mentor公司的ModelSimSE5.7工具進行編譯和仿真。在仿真時,SMIC庫提供的雙口RAM模型作為外部模塊掛接在系統中,模型的接口時序與圖4中所示的完全一致。圖7為節選的HIF模塊仿真波形。

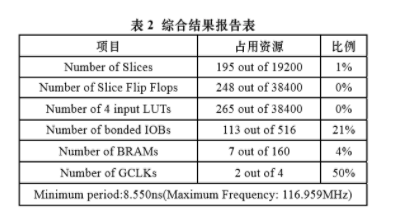

由于整個SoC系統的設計工作尚處于FPGA驗證階段,因此在綜合時選用Xilinx公司的ISE6.1軟件中自帶的XST綜合工具,FPGA器件選擇Virtex-E系列的XCV2000E。綜合后的結果報告如表2所示。

表2 綜合結果報告表

總結

由仿真和綜合的實驗結果可以看出,HIF模塊的設計可以滿足系統在功能上的要求,而且綜合后的模塊所占用的FPGA的面積和資源的比例都很小,有些甚至可以忽略不計,因而不會影響到系統中其它模塊的設計與實現。而綜合后的主工作頻率為116.959MHz,完全滿足設計要求。

編輯:jq

-

處理器

+關注

關注

68文章

20255瀏覽量

252276 -

RAM

+關注

關注

8文章

1399瀏覽量

120564 -

fifo

+關注

關注

3文章

407瀏覽量

45748 -

GPIO

+關注

關注

16文章

1328瀏覽量

56226

發布評論請先 登錄

德州儀器PTH系列DDR/QDR內存總線端接模塊解析

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】--LoongArch的SOC邏輯設計

Linux內核模塊的加載機制

fpga嵌入e203內核搭建soc如何實現通信功能?

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

蜂鳥E203 SoC的私有設備總線的簡單使用

利用蜂鳥E203搭建SoC【1】——AXI總線的配置與板級驗證

人臉識別和AES加密協同的SOC設計架構

基于hbirdv2的APB總線添加外設(一)

如何在e203 SOC中添加自定義外設

PIC32MZ W1系列Wi-Fi SoC技術解析與應用指南

解析MIPS內核的HDTV-SoC平臺總線接口模塊

解析MIPS內核的HDTV-SoC平臺總線接口模塊

評論