一、簡(jiǎn)要概述:

在芯片設(shè)計(jì)過程中,一個(gè)系統(tǒng)通常是同步電路和異步電路并存,這里經(jīng)常會(huì)遇到CDC也就是跨時(shí)鐘域處理的問題,常見的處理方法,可能大家也已經(jīng)比較熟悉了,主要有單bit跨時(shí)鐘處理、多bit跨時(shí)鐘處理兩大類,本文以一個(gè)總線全握手跨時(shí)鐘域處理為例解析,單bit和多bit跨時(shí)鐘處理。這里需要注意是多bit含義比較廣泛和總線不是一個(gè)概念,如果多個(gè)bit之間互相沒有任何關(guān)系,其實(shí),也就是位寬大于1的單bit跨時(shí)鐘處理問題,如果多個(gè)bit之間有關(guān)系,作為一個(gè)整體,那么我們就叫做總線。因此,大家常說的“多bit跨時(shí)鐘處理”也就是總線跨時(shí)鐘處理。

二、總線全握手應(yīng)用場(chǎng)景:

適用慢速總線信號(hào)跨時(shí)鐘域。慢到快,快到慢均可,只要保證源信號(hào)更新時(shí)間大于同步時(shí)間即可。同步周期為6或者8個(gè)慢時(shí)鐘周期。

三、總線全握手原理框圖:

總線全握手跨時(shí)鐘域原理圖如下所示,使用了兩個(gè)單bit同步器模塊,因?yàn)槭钦?qǐng)求和響應(yīng)都是電平信號(hào),所以這里采用單bit同步器(寄存器打2拍或者3拍)。這里反饋過來的dst_ack_sync信號(hào),經(jīng)過一定處理可以得到src_req和sync_ok信號(hào),圖中我未畫出。可以確定的是當(dāng)請(qǐng)求和響應(yīng)均為低電平時(shí),表明一次同步完成。

兩級(jí)觸發(fā)器同步原理:假設(shè)第一級(jí)觸發(fā)器的輸入不滿足其建立保持時(shí)間,它在第一個(gè)脈沖沿到來后輸出的數(shù)據(jù)就為亞穩(wěn)態(tài),那么在下一個(gè)脈沖沿到來之前,其輸出的亞穩(wěn)態(tài)數(shù)據(jù)在一段恢復(fù)時(shí)間后必須穩(wěn)定下來,而且穩(wěn)定的數(shù)據(jù)必須滿足第二級(jí)觸發(fā)器的建立時(shí)間,如果都滿足了,在下一個(gè)脈沖沿到來時(shí),第二級(jí)觸發(fā)器將不會(huì)出現(xiàn)亞穩(wěn)態(tài),因?yàn)槠漭斎攵说臄?shù)據(jù)滿足其建立保持時(shí)間。同步器有效的條件:第一級(jí)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)后的恢復(fù)時(shí)間 + 第二級(jí)觸發(fā)器的建立時(shí)間 < = 時(shí)鐘周期。

注意:在芯片設(shè)計(jì)中,單bit同步器通常不是私自直接打兩拍處理的,而是使用專用的同步器單元,這樣做的好處是方便后端(PR)可以把兩級(jí)觸發(fā)器視為一個(gè)整體,把兩級(jí)觸發(fā)器放的很近(線延時(shí)比較小)。這是因?yàn)槟芨玫臐M足第二級(jí)觸發(fā)器建立時(shí)間,有效的減少亞穩(wěn)態(tài)傳播。

四、總線全握手仿真測(cè)試 :

場(chǎng)景1:源時(shí)鐘100Mhz,目的時(shí)鐘25Mhz,2級(jí)同步器。

從上圖可以看出,同步完成需要6個(gè)目的時(shí)鐘周期,也就是說完成一次全握手需要6個(gè)目的時(shí)鐘周期的時(shí)間,這就要求源時(shí)鐘數(shù)據(jù)信號(hào)的更新時(shí)間,必須大于同步時(shí)間。如果變化太快中間的數(shù)據(jù)會(huì)漏采。

場(chǎng)景2:源時(shí)鐘25Mhz,目的時(shí)鐘100Mhz,2級(jí)同步器

從上圖可以看出,同步完成需要6個(gè)源時(shí)鐘周期,也就是說完成一次全握手需要6個(gè)源時(shí)鐘周期的時(shí)間,這就要求源時(shí)鐘數(shù)據(jù)信號(hào)的更新時(shí)間,必須大于同步時(shí)間。如果變化太快中間的數(shù)據(jù)會(huì)漏采。

場(chǎng)景3:源時(shí)鐘25Mhz,目的時(shí)鐘100Mhz,3級(jí)同步器

從上圖可以看出,同步完成需要8個(gè)源時(shí)鐘周期,也就是說使用3級(jí)同步器完成一次全握手需要6+2個(gè)源時(shí)鐘周期的時(shí)間。

結(jié)論:在使用總線全握手同步器時(shí),不管源時(shí)鐘與目的時(shí)鐘多大,同步的時(shí)間均是慢時(shí)鐘的6個(gè)時(shí)鐘周期,如果使用3級(jí)同步器則是8個(gè)慢速時(shí)鐘周期。這就要求源時(shí)鐘信號(hào)不能變化太快。

原文標(biāo)題:CDC(一) 總線全握手跨時(shí)鐘域處理

文章出處:【微信公眾號(hào):FPGA自習(xí)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

電路

+關(guān)注

關(guān)注

173文章

6075瀏覽量

178378 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134986

原文標(biāo)題:CDC(一) 總線全握手跨時(shí)鐘域處理

文章出處:【微信號(hào):FPGA_Study,微信公眾號(hào):FPGA自習(xí)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FLASHDB中KVDB 的FDB_WRITE_GRAN可以改為64bit或者128bit而TSDB為什么不行?

主板的RGB接口是16bit位(RGB-565),怎么24bit位RGB接口的 屏幕 接線 ?

PT5F2307 觸摸 A/D 型 8-Bit MCU規(guī)格書

液晶顯示屏LVDS接口JEIAD 、VESA、18bit LVDS關(guān)聯(lián)和區(qū)別

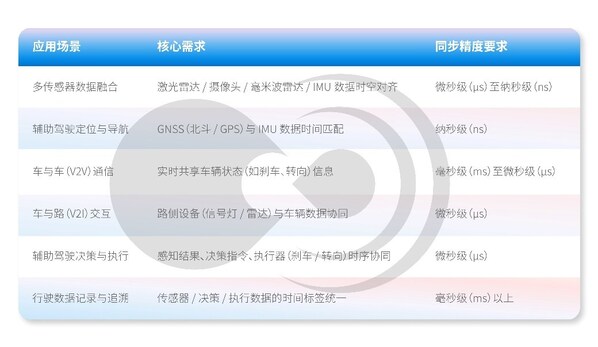

黑芝麻智能跨域時(shí)間同步技術(shù):消除多域計(jì)算單元的時(shí)鐘信任鴻溝

一款單芯片、單電源、10bit、50MSPS的模數(shù)轉(zhuǎn)換器-MS9280

STM32U5+8bit_8080 LCD 怎么配置touchgfx?

請(qǐng)問CY7C68013A可以使用8bit FIFO數(shù)據(jù)接口嗎?

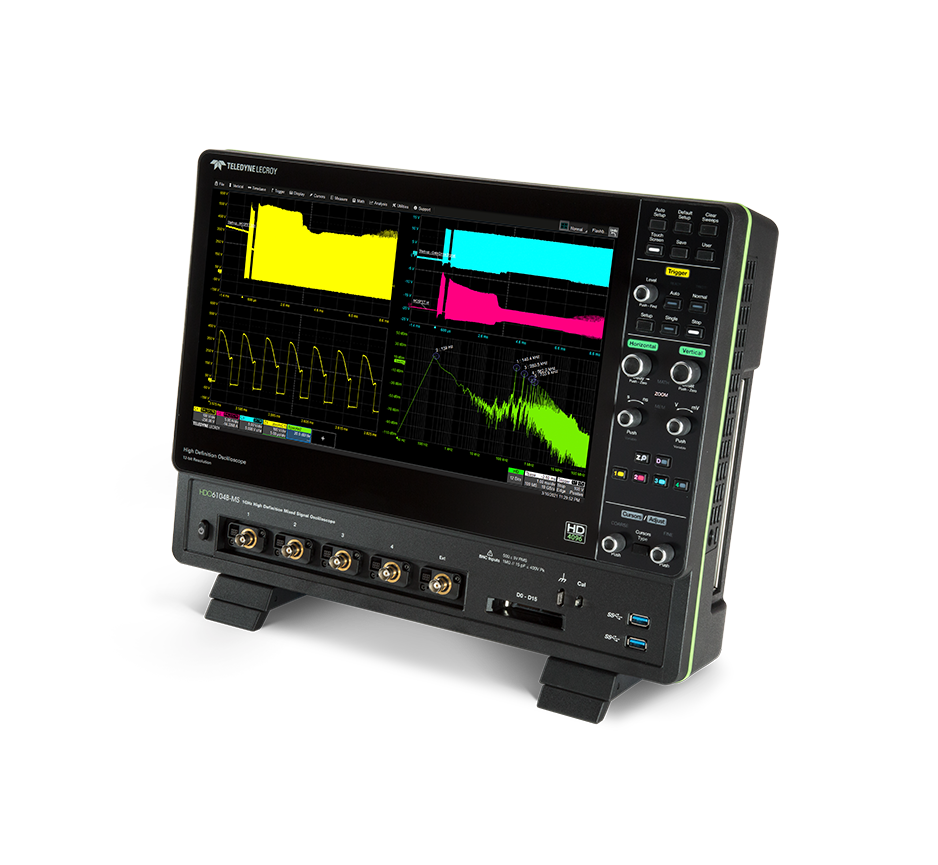

深入淺出解析:為什么高精度測(cè)量要選擇12bit示波器?

面向多電機(jī)系統(tǒng)的磁編解決方案:MT6501的12bit分辨率同步采樣

跨異步時(shí)鐘域處理方法大全

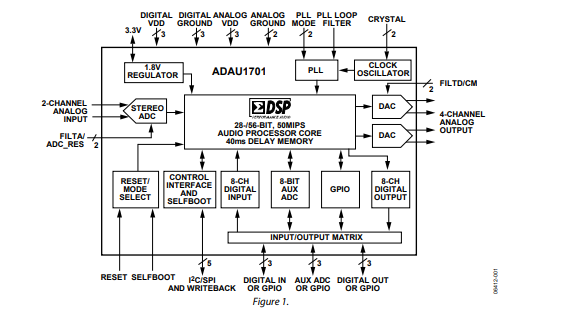

ADAU1701 SigmaDSP 28/56 Bit音頻處理器,內(nèi)置2個(gè)ADC和4個(gè)DAC技術(shù)手冊(cè)

揭秘 HDO6000B 示波器:12-bit 與 1GHz 背后硬核技術(shù)與創(chuàng)新應(yīng)用

如何解決單bit和多bit跨時(shí)鐘處理問題?

如何解決單bit和多bit跨時(shí)鐘處理問題?

評(píng)論