1 IDDR

1.1 介紹

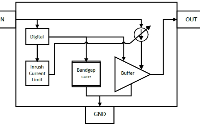

該設計元素是專用的輸入寄存器,旨在將外部雙數據速率(DDR)信號接收到Xilinx FPGA中。IDDR可用的模式可以在捕獲數據的時間和時鐘沿或在相同的時鐘沿向FPGA架構顯示數據。此功能使您可以避免其他時序復雜性和資源使用情況。

1)OPPOSITE_EDGE模式-以傳統的DDR方法恢復數據。給定分別在引腳D和C上的DDR數據和時鐘,在時鐘C的每個上升沿之后Q1發生變化,在時鐘C的每個下降沿之后Q2發生變化。

2)SAME_EDGE模式-時鐘C的相對邊沿仍然恢復數據。但是,在負邊沿數據寄存器后面放置了一個額外的寄存器。這個額外的寄存器由時鐘信號C的正時鐘沿提供時鐘。結果,現在DDR數據在相同的時鐘沿提供給FPGA架構。但是,由于此功能,數據對似乎是“分離的”。Q1和Q2不再具有對1和2。相反,出現的第一個對是對1和DONT_CARE,在下一個時鐘周期之后是對2和3。

3)SAME_EDGE_PIPELINED模式-以與SAME_EDGE模式類似的方式恢復數據。為了避免SAME_EDGE模式的“分離”效應,在上升沿數據寄存器的前面放置了一個額外的寄存器。現在,數據對同時出現在Q1和Q2引腳上。但是,使用此模式將使Q1和Q2信號更改的延遲時間增加一個額外的周期。

1.2 Verilog Instantiation Template

// IDDR: Input Double Data Rate Input Register with Set, Reset

// and Clock Enable.

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

IDDR #(

.DDR_CLK_EDGE(“OPPOSITE_EDGE”), // “OPPOSITE_EDGE”, “SAME_EDGE”

// or “SAME_EDGE_PIPELINED”

.INIT_Q1(1‘b0), // Initial value of Q1: 1’b0 or 1‘b1

.INIT_Q2(1’b0), // Initial value of Q2: 1‘b0 or 1’b1

.SRTYPE(“SYNC”) // Set/Reset type: “SYNC” or “ASYNC”

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of IDDR_inst instantiation

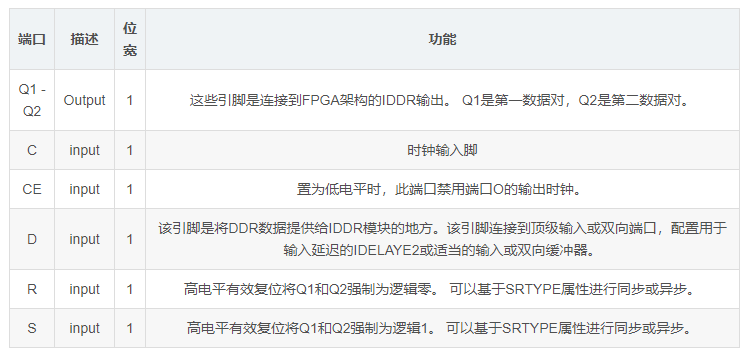

1.3端口描述

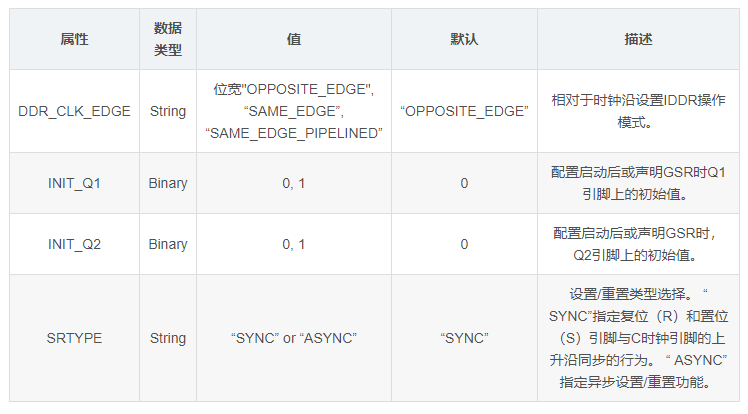

1.4 可用屬性

原文標題:xilinx源語 IDDR和ODDR

文章出處:【微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Xilinx

+關注

關注

73文章

2200瀏覽量

131139 -

IDDR

+關注

關注

0文章

3瀏覽量

9722

原文標題:xilinx源語 IDDR和ODDR

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

中科曙光解碼流行語背后的發展密碼

Xilinx FPGA串行通信協議介紹

NVIDIA助力語核科技產線質檢數字員工落地

華為內部資料—無源濾波元器件-電容的介紹和深入認識

Xilinx Shift RAM IP概述和主要功能

武漢芯源半導體CW32L010在兩輪車儀表的應用介紹

中移芯昇順利完成無源物聯網芯片回片測試

普源示波器波形噪聲解決指南

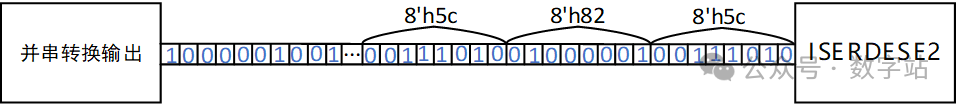

ISERDESE2原語端口及參數介紹

中科視語入選甲子光年《2025 中國AI Agent行業研究報告》

xilinx源語中IDDR和ODDR介紹

xilinx源語中IDDR和ODDR介紹

評論