CMOS的重要性自然不再需要小編再多論及,在往期CMOS文章中,小編對CMOS故障、CMOS和CCD的區(qū)別等內容有所介紹。為增進大家對CMOS的了解程度,本文將基于兩點對CMOS予以闡述:1.CMOS集成電路特點,2.CMOS和TTL的優(yōu)缺點介紹。如果你對CMOS具有興趣,不妨繼續(xù)往下閱讀哦。

一、CMOS集成電路的特點

1.CMOS集成電路功耗低

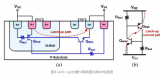

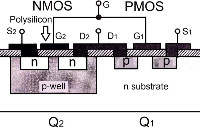

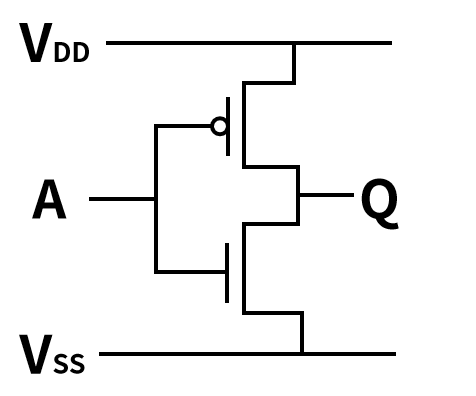

CMOS集成電路采用場效應管,且都是互補結構,工作時兩個串聯(lián)的場效應管總是處于一個管導通,另一個管截止的狀態(tài),電路靜態(tài)功耗理論上為零。實際上,由于存在漏電流,CMOS電路尚有微量靜態(tài)功耗。單個門電路的功耗典型值僅為20mW,動態(tài)功耗(在1MHz工作頻率時)也僅為幾mW。

2.CMOS集成電路工作電壓范圍寬

CMOS集成電路供電簡單,供電電源體積小,基本上不需穩(wěn)壓。國產(chǎn)CC4000系列的集成電路,可在3~18V電壓下正常工作。

3.CMOS集成電路邏輯擺幅大

CMOS集成電路的邏輯高電平“1”、邏輯低電平“0”分別接近于電源高電位VDD及電影低電位VSS。當VDD=15V,VSS=0V時,輸出邏輯擺幅近似15V。因此,CMOS集成電路的電壓電壓利用系數(shù)在各類集成電路中指標是較高的。

4.CMOS集成電路抗干擾能力強

CMOS集成電路的電壓噪聲容限的典型值為電源電壓的45%,保證值為電源電壓的30%。隨著電源電壓的增加,噪聲容限電壓的絕對值將成比例增加。對于VDD=15V的供電電壓(當VSS=0V時),電路將有7V左右的噪聲容限。

5.CMOS集成電路輸入阻抗高

CMOS集成電路的輸入端一般都是由保護二極管和串聯(lián)電阻構成的保護網(wǎng)絡,故比一般場效應管的輸入電阻稍小,但在正常工作電壓范圍內,這些保護二極管均處于反向偏置狀態(tài),直流輸入阻抗取決于這些二極管的泄露電流,通常情況下,等效輸入阻抗高達103~1011Ω,因此CMOS集成電路幾乎不消耗驅動電路的功率。

6.CMOS集成電路溫度穩(wěn)定性能好

由于CMOS集成電路的功耗很低,內部發(fā)熱量少,而且,CMOS電路線路結構和電氣參數(shù)都具有對稱性,在溫度環(huán)境發(fā)生變化時,某些參數(shù)能起到自動補償作用,因而CMOS集成電路的溫度特性非常好。一般陶瓷金屬封裝的電路,工作溫度為-55~+125℃;塑料封裝的電路工作溫度范圍為-45~+85℃。

7.CMOS集成電路扇出能力強

扇出能力是用電路輸出端所能帶動的輸入端數(shù)來表示的。由于CMOS集成電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS集成電路用來驅動同類型,如不考慮速度,一般可以驅動50個以上的輸入端。

8.CMOS集成電路抗輻射能力強

CMOS集成電路中的基本器件是MOS晶體管,屬于多數(shù)載流子導電器件。各種射線、輻射對其導電性能的影響都有限,因而特別適用于制作航天及核實驗設備。

9.CMOS集成電路可控性好

CMOS集成電路輸出波形的上升和下降時間可以控制,其輸出的上升和下降時間的典型值為電路傳輸延遲時間的125%~140%。

10.CMOS集成電路接口方便

因為CMOS集成電路的輸入阻抗高和輸出擺幅大,所以易于被其他電路所驅動,也容易驅動其他類型的電路或器件。

二、TTL與CMOS的優(yōu)缺點

第一個也是最常被談論的是功耗-TTL比CMOS消耗更多的電能。

這在某種意義上是正確的,TTL輸入只是雙極晶體管的基礎,雙極晶體管需要一些電流來打開它,輸入電流的大小取決于內部的電路。當許多TTL輸入連接到一個TTL輸出時,這就成了一個問題,而TTL輸出通常只是一個上拉電阻或一個驅動性能較差的高壓側晶體管。

另一方面,CMOS晶體管是場效應的,換句話說,柵極處的電場足以影響半導體通道的傳導。理論上,除了柵極的小漏電流(通常為皮卡或毫安量級)外,不會產(chǎn)生電流。然而,這并不是說即使在更高的速度下,同樣的低電流消耗也是正確的。CMOS芯片的輸入具有一定的電容,因此上升時間有限。為了確保在高頻下上升時間很快,需要一個大電流,在MHz或GHz頻率下可以達到幾安培。這種電流只在輸入必須改變狀態(tài)時才被消耗,而TTL的偏置電流必須與信號一起存在。

在輸出方面,CMOS和TTL各有優(yōu)缺點。TTL輸出要么是圖騰柱,要么是上拉。有了圖騰桿,輸出只能在軌道0.5V范圍內擺動。然而,其輸出電流遠高于CMOS芯片。同時,CMOS輸出可以與電壓控制電阻器相比較,根據(jù)負載情況,可以在電源軌的毫伏范圍內輸出。然而,兩個led的輸出電流往往很有限。

由于其較小的電流要求,CMOS邏輯非常適合小型化,數(shù)百萬個晶體管可以封裝到一個小區(qū)域,而不需要過高的電流。

與CMOS相比,TTL的另一個重要優(yōu)勢是其耐用性。場效應晶體管依賴于柵極和溝道之間的薄氧化硅層來提供它們之間的隔離。這種氧化層厚度為納米,擊穿電壓很小,即使在高功率fet中也很少超過20V。這使得CMOS對靜電放電和過電壓非常敏感。如果輸入是浮動的,它們會慢慢積累電荷并引起輸出狀態(tài)的假變化,這就是為什么CMOS輸入通常被上拉、下拉或接地。TTL在很大程度上不受這個問題的影響,因為輸入端是一個晶體管基極,它的作用更像一個二極管,由于它的阻抗較低,對噪聲不太敏感。

責任編輯人:CC

-

CMOS

+關注

關注

58文章

6217瀏覽量

242890 -

TTL

+關注

關注

7文章

556瀏覽量

74704 -

CMOS集成電路

+關注

關注

4文章

41瀏覽量

14670

發(fā)布評論請先 登錄

單片機TTL和CMOS電平知識

2.4 GHz CMOS WLAN 射頻前端集成電路,帶 PA、帶旁路的 LNA 以及用于 WLAN 和藍牙?信號功能的 SP3T 開關 skyworksinc

CMOS集成電路中閂鎖效應的產(chǎn)生與防護

KEC-KIC7512P模擬CMOS集成電路技術手冊

CMOS圖像傳感器的制造步驟

CMOS超大規(guī)模集成電路制造工藝流程的基礎知識

一款雙通道采用SOIC-8封裝的25MBd CMOS光耦合器-ICPL-074L

CMOS工藝流程簡介

中國集成電路大全 接口集成電路

浮思特 | CMOS技術原理與應用:從晶體管結構到反相器設計

CMOS,Bipolar,F(xiàn)ET這三種工藝的優(yōu)缺點是什么?

硬件基礎篇——TTL與CMOS電平

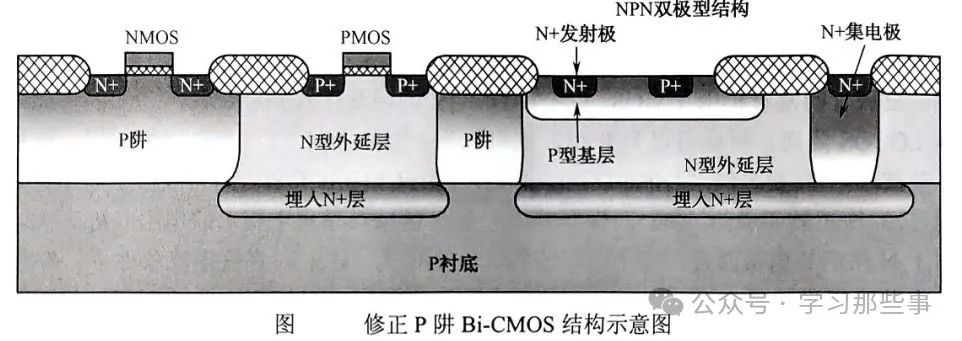

Bi-CMOS工藝解析

CMOS集成電路的基本制造工藝

CMOS集成電路的特點,TTL與CMOS的優(yōu)缺點

CMOS集成電路的特點,TTL與CMOS的優(yōu)缺點

評論