原創(chuàng)聲明:

本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處。

適用于板卡型號(hào):

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目錄為“ps_hello/vivado”

vitis工程目錄為“ps_dp/vitis”

本章介紹PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

軟件工程師工作內(nèi)容

以下為軟件工程師負(fù)責(zé)內(nèi)容。

1. 接口介紹

DisplayPort v1.2協(xié)議,支持4個(gè)5.4G的lane,但本控制器只支持兩個(gè)lane,分辨率最大支持4096*2160@30。

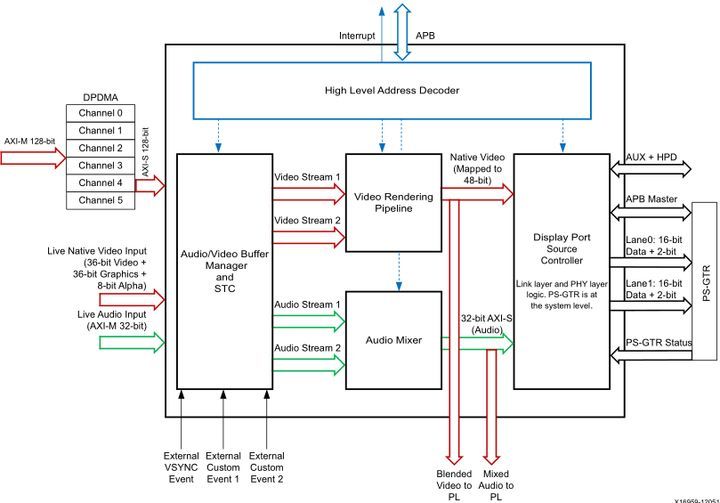

控制器數(shù)據(jù)接口如下圖:

圖中,AXI-M用于讀取內(nèi)存中的視頻和音頻數(shù)據(jù),這里叫非實(shí)時(shí)音視頻,DPDMA有六個(gè)通道,其中3路用于視頻,1路用于圖形,2路用于音頻。

2. Example工程介紹

-

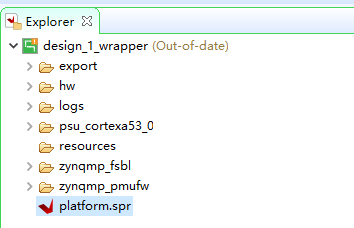

新建platform,過程不再介紹,在”PS端RTC中斷實(shí)驗(yàn)”中已經(jīng)介紹過。

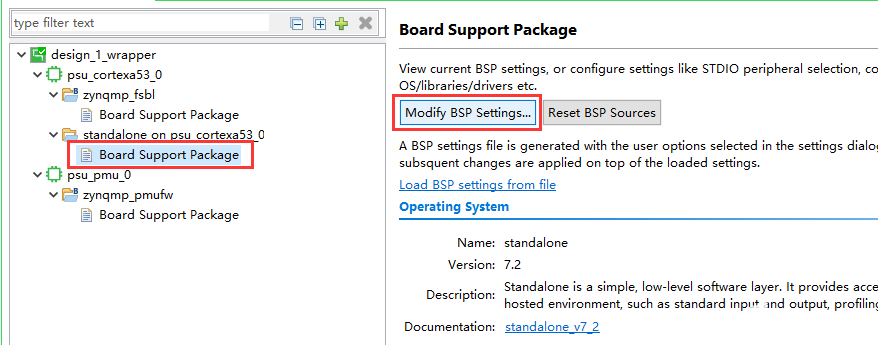

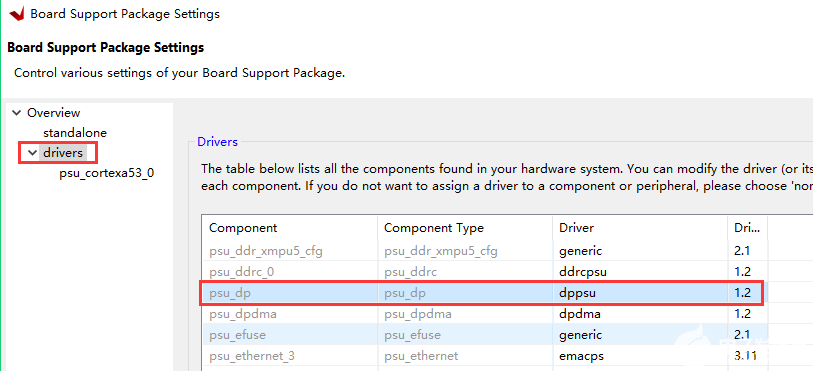

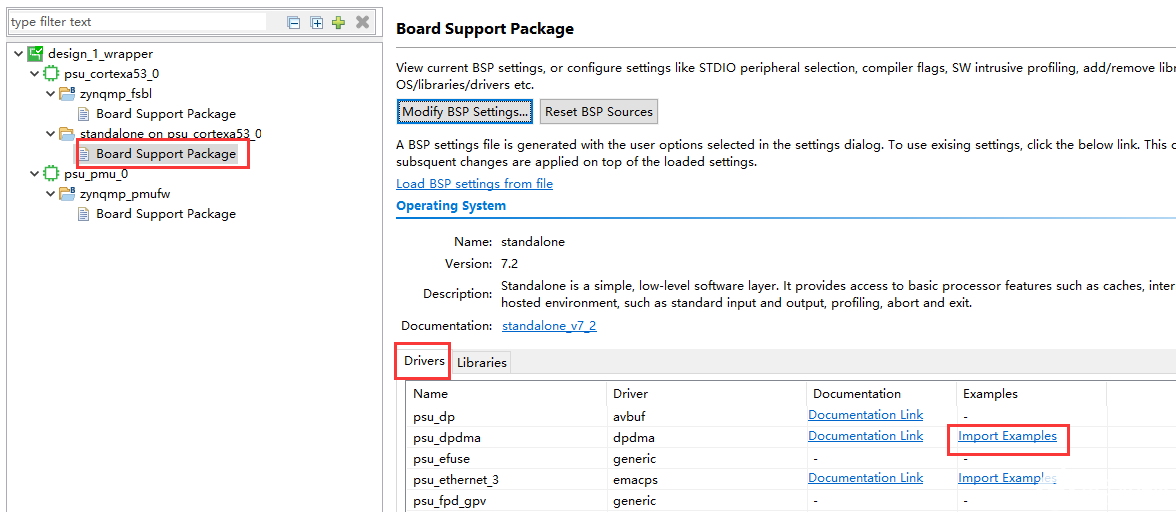

1)配置BSP

并將psu_dp驅(qū)動(dòng)改為dppsu,然后點(diǎn)擊OK

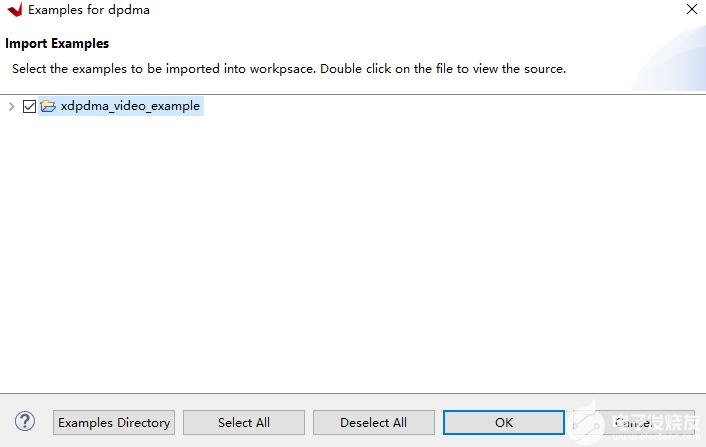

3)導(dǎo)入example工程

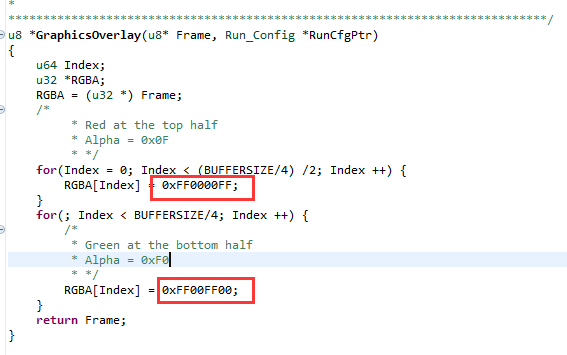

4) 例子默認(rèn)是1080P,RGBA顯示的,可以將RGBA的Alpha值都改成FF,使顯示效果更好,保存,并編譯工程。

3. 板上驗(yàn)證

連接板上的MINI DP接口

下載后,顯示效果如下

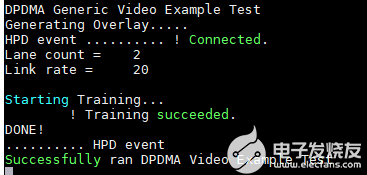

在串口工具中可以看到DP口進(jìn)行了訓(xùn)練并成功運(yùn)行。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22468瀏覽量

638044 -

音頻

+關(guān)注

關(guān)注

31文章

3212瀏覽量

85922 -

DP

+關(guān)注

關(guān)注

1文章

245瀏覽量

42488 -

Zynq

+關(guān)注

關(guān)注

10文章

631瀏覽量

49524 -

MPSoC

+關(guān)注

關(guān)注

0文章

203瀏覽量

25207

發(fā)布評(píng)論請(qǐng)先 登錄

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

第二十三講 異步計(jì)數(shù)器

模擬電路網(wǎng)絡(luò)課件 第二十三節(jié):乙類雙電源互補(bǔ)對(duì)稱功率放大電路

閑話Zynq UltraScale+ MPSoC(連載1)

2017中國(guó)西部微波射頻技術(shù)研討會(huì)暨第二十三屆國(guó)際電子測(cè)試測(cè)量研討會(huì)

Zynq UltraScale+ MPSoC的發(fā)售消息

米爾科技Zynq UltraScale+ MPSoC技術(shù)參考手冊(cè)介紹

如何調(diào)試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

【正點(diǎn)原子FPGA連載】第二十三章RGB-LCD字符和圖片顯示實(shí)驗(yàn) -摘自【正點(diǎn)原子】新起點(diǎn)之FPGA開發(fā)指南_V2.1

烽火通信光纖技術(shù)獲“第二十三屆中國(guó)專利獎(jiǎng)”銀獎(jiǎng)

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設(shè)計(jì)

Zynq UltraScale+ MPSoC的隔離設(shè)計(jì)示例

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

評(píng)論