原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

本章以AN3485模塊介紹RS485的數據傳輸。

1.實驗原理

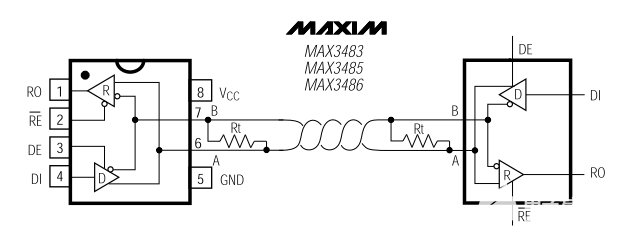

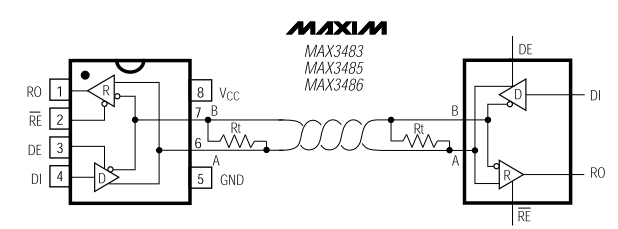

前面介紹過RS232和RS422的實驗,而RS485與RS422類似,也是采用差分信號傳輸,但RS485是半雙工傳輸,也就是說,同一時刻只能有一個方向的數據傳輸。而且接口也比RS422少,只有差分信號A和B,而與ARM或FPGA相連的信號為DE(方向選擇),DI(輸入信號TXD),RO(輸出信號RXD)。

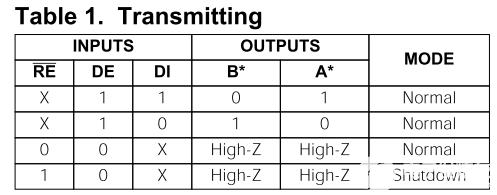

從MAX3485文檔中,發送方向,如果DE為1時,也就是輸出使能,DI值為1時,對于差分信號A和B值為1和0,否則為0和1。

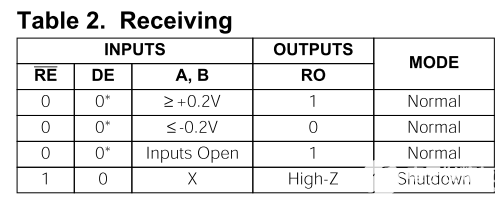

從接收來看,如果DE為0,A和B之間差值大于等于+0.2V,則RO值為1,否則為0。

2.程序設計

由于RS485是半雙工傳輸,那么我們需要制定傳輸協議進行握手,設定第一個字節為8’h55,表示一幀數據的開始,接下來是傳輸的數據長度信息,由于FIFO大小限制(256),范圍為1~255,接下來是數據。格式即為:起始8’h55+數據長度+數據。

其中uart_tx和uart_rx跟RS232實驗一樣,在這里只修改uart_test即可。我們設計的功能為初始狀態下將DE設為0,也就是輸入,等待接收上位機發來的數據,并緩存到FIFO中,FIFO大小設置為256,然后切換DE為1,也就是輸出,把接收到的數據從FIFO中讀出并發送出去。注意緩存的數據是除去起始8’h55和數量信息的。

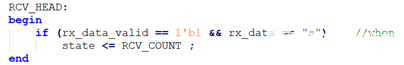

在RCV_HEAD狀態時,判斷接收到的數據是否是”S”。

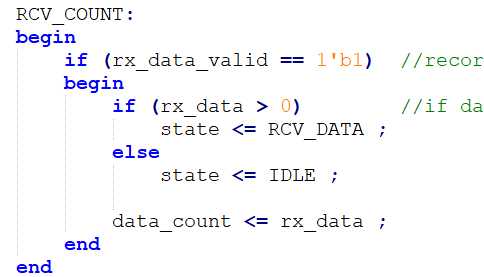

在RCV_COUNT狀態時,如果數據長度小于0,則跳轉到IDLE狀態,如果大于0,則進入接收數據狀態。

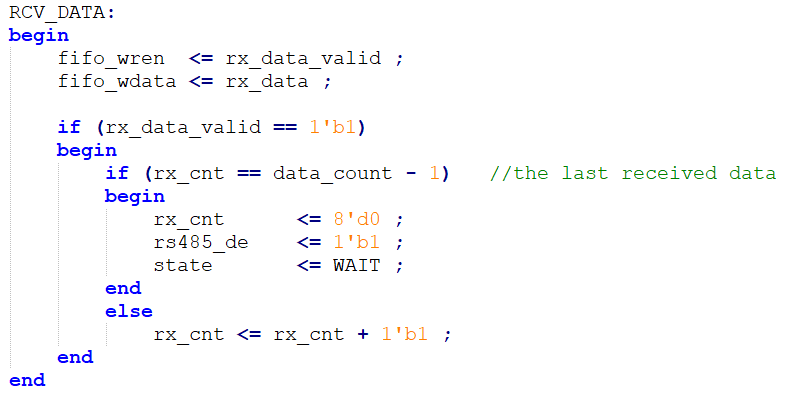

在RCV_DATA狀態下,把數據寫入FIFO,并且檢查數據長度,切換RS485的方向為輸出,并跳轉狀態。

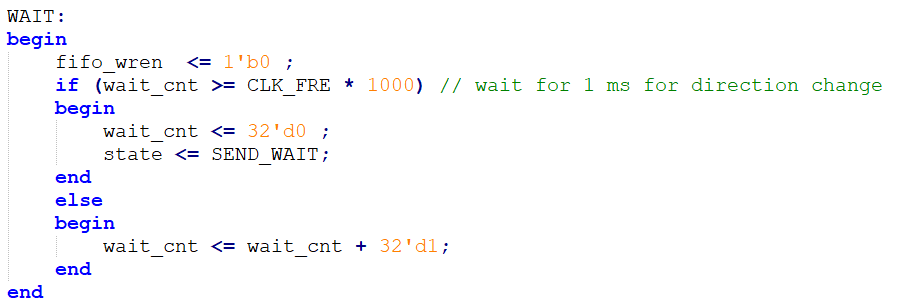

在切換總線狀態時,為了可靠工作,在WAIT狀態下,延時1ms進行方向切換。

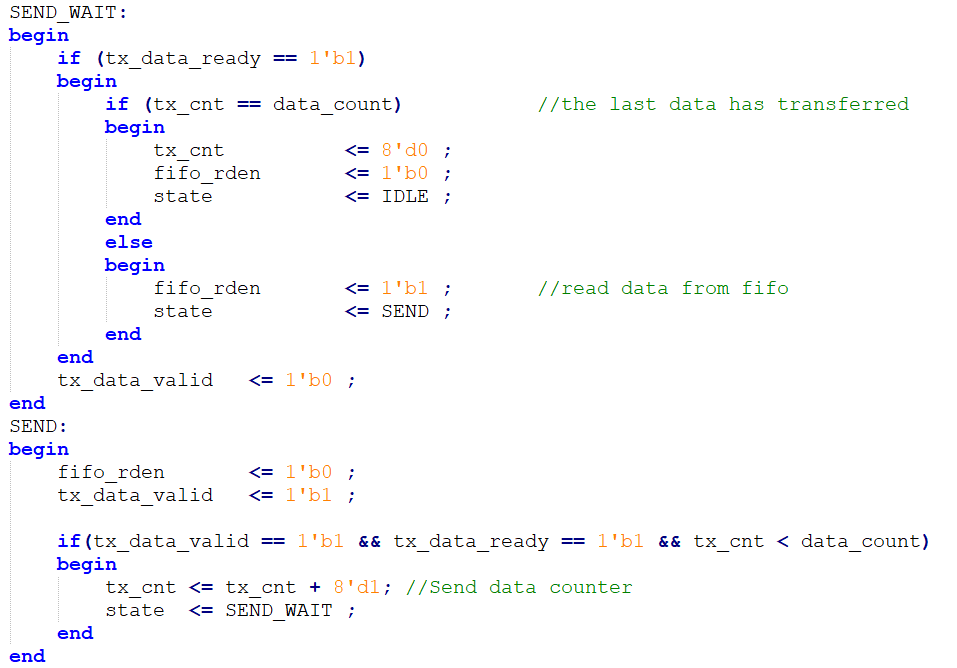

再然后是發送FIFO中的數據,SEND_WAIT狀態是控制讀使能信號fifo_rden,并且判斷數據是否發送完,發送完后進入IDLE狀態。

3. 實驗測試

我們仍然使用USB轉串口設備,通過杜邦線將RS485_1的A和B分別與設備的A和B連接。

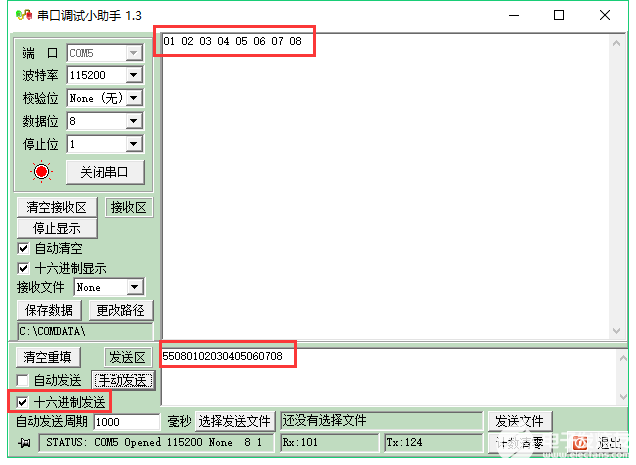

打開串口工具,設置好串口號波特率,選擇16進制發送,發送數據以8’h55開頭,點擊發送,即可在接收窗口看到返回的數據。

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638485 -

RS485

+關注

關注

40文章

1348瀏覽量

86171 -

差分信號

+關注

關注

4文章

409瀏覽量

29053 -

Zynq

+關注

關注

10文章

632瀏覽量

49542 -

MPSoC

+關注

關注

0文章

203瀏覽量

25218

發布評論請先 登錄

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Ti推出面向Zynq UltraScale+ MPSoC的電源參考設計

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ MPSoC的發售消息

米爾科技Zynq UltraScale+ MPSoC技術參考手冊介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

米爾電子zynq ultrascale+ mpsoc底板外設資源清單分享

ZYNQ Ultrascale+ MPSoC系列FPGA芯片設計

Zynq UltraScale+ MPSoC中的隔離方法

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+ MPSoC驗證數據手冊

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485實驗

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485實驗

評論