作者:碎碎思,來源:OpenFPGA微信公眾號

圖形界面操作

完成Implementation后,在Vivado IDE左側的Flow Navigator點擊Open Implemented Design,然后點擊report_utilization。

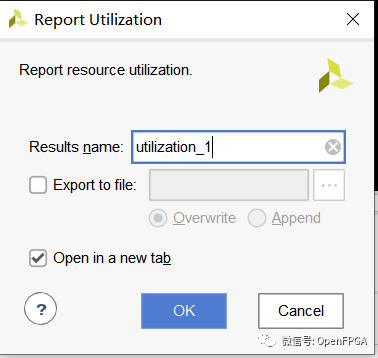

新建一個名字和選擇是否導出到文件,點擊OK。

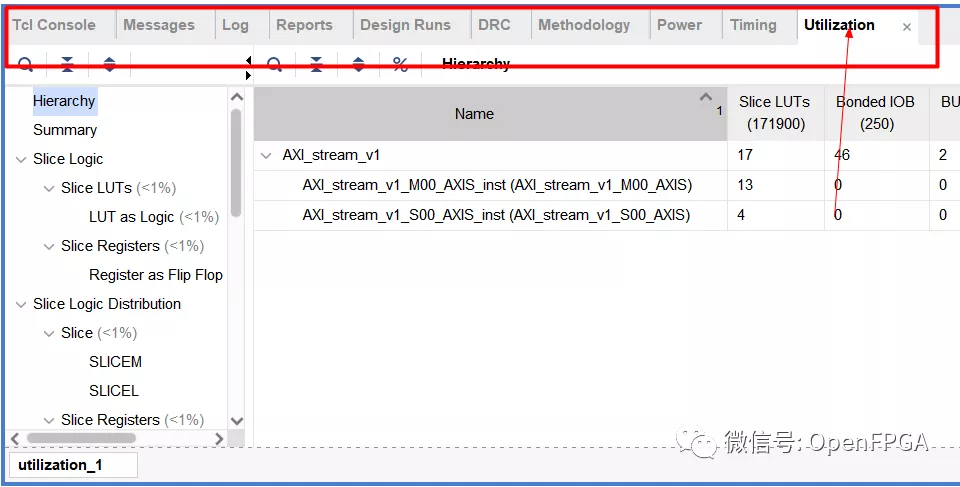

在生成的結果中選中某一類資源,會看到按模塊排列的資源占用情況。

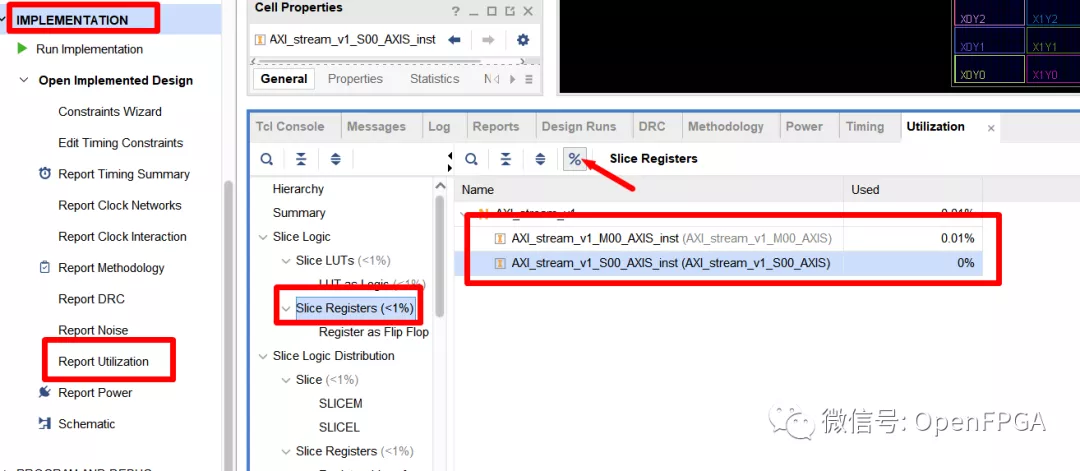

當然,點擊圖示箭頭位置可以按照%顯示資源。

TCL操作

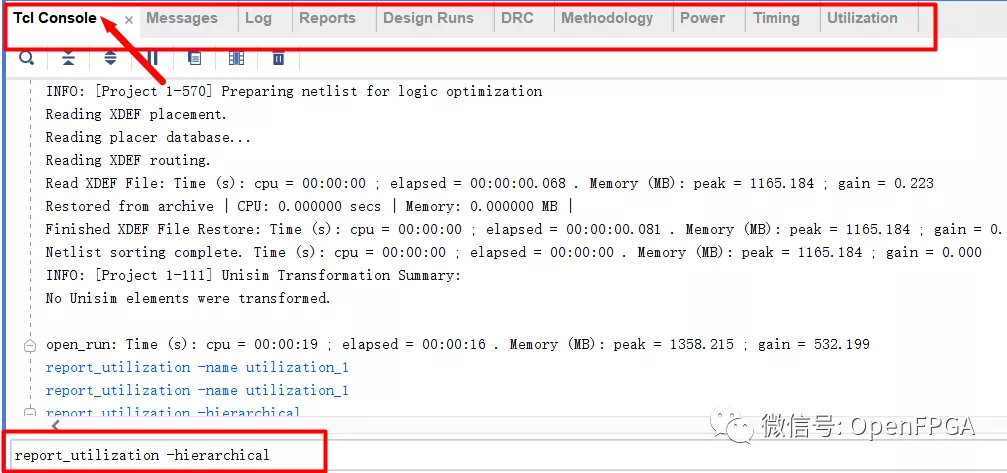

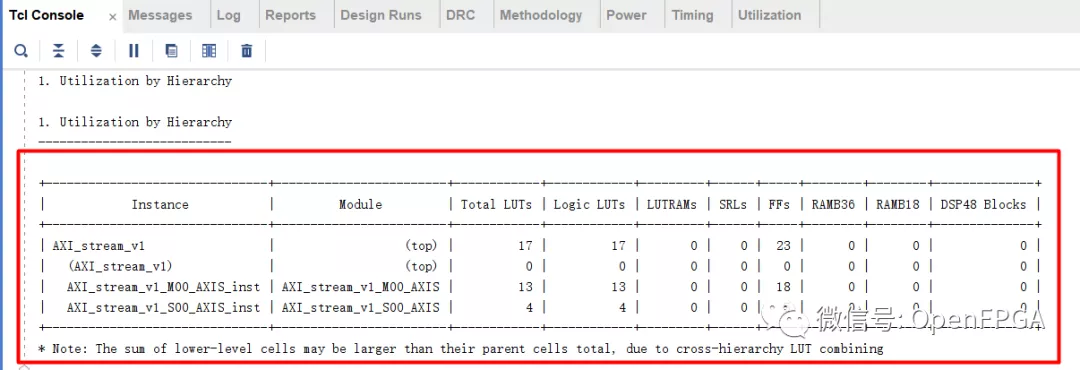

report_utilization -hierarchical

圖示箭頭窗口下面的命令行位置輸入上述命令,回車即可。

審核編輯 黃昊宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Vivado

+關注

關注

19文章

857瀏覽量

71114

發布評論請先 登錄

相關推薦

熱點推薦

激光焊接技術在焊接微電子模塊工藝中的應用

激光焊接技術作為一種高精度和高效率的加工方法,在微電子模塊的制造過程中扮演著至關重要的角色。其憑借獨特的能量控制方式和極小的熱影響區,為微電子領域提供了高質量的連接解決方案,尤其適用于對熱敏感和結構

NVMe高速傳輸之擺脫XDMA設計45:上板資源占用率分析

Block Design 設計后進行綜合與實現, NoP 邏輯加速引擎的在不同 FPGA 平臺中的資源占用率分別如表 1 和表 2 所示。 從表中可以看到, 本課題設計的 NoP邏輯加速引擎資源

發表于 11-13 08:36

vivado連接Atry A7-35T死機怎么解決?

前提條件:

1)開發板是Digilent的ARTY A7-35T開發版,也就是《手把手教你設計CPU-RISC-V處理器》中介紹的那塊板子

2)vivado安裝正常,可以啟動,跑make mcs

發表于 11-07 06:05

win10環境下使用vivado生成.bit與.mcs文件

在hbirdv2參考文檔中使用make指令生成system.bit和system.mcs文件,但是虛擬機本身會消耗計算資源,導致運行速度變慢,對于不習慣在linux下編輯代碼的人,還需要來回倒騰代碼

發表于 10-27 08:25

vcs和vivado聯合仿真

我們在做參賽課題的過程中發現,上FPGA開發板跑系統時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado ip核的soc系統進行仿真。在這種情況

發表于 10-24 07:28

在vivado上基于二進制碼對指令運行狀態進行判斷

成對應的.dasm文件,用于查看對應的匯編指令。

獲取測試指令

以helloworld為例,在生成對應的兩個文件之后,我們可以選取想要測試的指令導入vivado

我們以測試

li a0 8

addi a0

發表于 10-24 06:31

【VPX361】青翼凌云科技基于3U VPX總線架構的XCZU47DR射頻收發子模塊

VPX361是一款基于3U VPX總線架構的8路射頻收發子模塊,板卡采用1片XCZU47DR RFSOC來實現8路射頻信號的高速采集、信號生成以及處理,并進行智能目標識別。

Vivado無法選中開發板的常見原因及解決方法

對應的器件信息和約束文件(XDC),大大簡化工程初始化流程。然而,在某些情況下,我們可能會發現 Vivado 的界面中無法選中目標開發板,導致只能手動選擇器件。那么,遇到這種情況該如何處理呢?

HarmonyOS優化應用預置圖片資源加載耗時問題性能優化

CPU解壓縮生成的圖片資源會占用較多的內存空間,給內存造成更大的壓力,可能會引起卡頓掉幀。此時可以借助紋理壓縮技術,將預置圖片在構建過程中進行轉碼和壓縮,節省CPU的處理過程,減少占用內存,提升應用性

發表于 05-29 16:11

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結果(以 Vivado 2024.2 為例)。

谷歌發布混合量子模擬方法

據外媒報道,谷歌發布了一種混合量子模擬方法;論文已經在Nature正式發表,谷歌混合量子模擬器的核心在于將模擬和數字技術相結合;是全新的模擬-數字方案,可在保持速度的同時增強可控制性,這一方案顛覆了

Vivado下怎么查看各子模塊的資源占用?

Vivado下怎么查看各子模塊的資源占用?

評論