描述

DONE 變為高電平后應給 CCLK 應用多少個時鐘周期以確保我的 FPGA 器件完全工作。

解決方案

DONE 由 Startup 序列釋放,表明配置已經完成。

此狀態是使用 BitGen “-g DONE_cycle” 選項定義的。默認情況下,DONE 在周期 4 中變高。

DONE 說明配置已經完成,且所有數據都已載入,但應應用一些額外的時鐘周期,以確保啟動序列正確完成。

啟動過程是由一個 7 狀態機控制機控制的。 DONE 之后所需時鐘周期的保守為 64個周期;這能滿足大多數使用案例的需求,這里 DONE 使用理想時鐘和默認選項。

一些 BitGen 選項會延遲整個startup的過程。

這些包括:

LCK_cycle – 延遲啟動,直到所有 DCM/MMCM 都被鎖定,因此添加的時鐘周期數量是未定義的。

Match_cycle – 延遲啟動,直到 DCI 匹配,因此添加的時鐘周期數量是未定義的。

DONE_PIPE – 添加時鐘周期到 DONE_CYCLE 指定的狀態。

如果在啟動過程中不提供足夠的時鐘數量,會出現以下癥狀:

I/O 保持三態。

雙模式引腳在 LVCMOS 中工作,而不是指定的 I/O 標準。 在雙模式引腳上使用DCI時,DCI 是針對 LVCMOS 校準的,而不是針對選定的I / O校準的。 為避免這種情況,請參閱(Xilinx Answer 14887)

ICAP 接口不能從 FPGA 架構訪問,因為配置邏輯被鎖定。

除某些雙端口引腳外,還有占空比或幅度失真。 偽差分信號(例如DIFF_SSTL_15和LVDS)可能會發生這種情況。

當設備尚未到達啟動狀態機的末尾時,會發生這種情況。 在達到啟動狀態結束之前,設備可能已完全運行。 這可能會導致 ICAP 讀寫錯誤,并阻止雙模式引腳使用正確的 I / O 標準。

可以通過將 EOS 信號驅動為高電平來確認此事件。用 STARTUP 原語可在 STAT 寄存器中觀察或在 FPGA 架構中檢測到。

對訪問 ICAP 的設計方案而言,較好的設計實踐是實例化 STARTUP 原語。

該原語有一個 EOS 引腳,表示配置過程已完成,并且 ICAP 具有讀寫訪問權限。

使用 JTAG 配置時例外。 對于 JTAG,訪問配置邏輯具有最高優先級。

當 JTAG 訪問配置邏輯時,ICAP 讀取和寫入失敗。該 EOS 引腳上的值并不表示 JTAG 有訪問權限。

審核編輯:何安

-

時鐘

+關注

關注

11文章

1971瀏覽量

134986

發布評論請先 登錄

假設系統的時鐘頻率是200k,延時10個時鐘周期是什么意思呢?

時鐘周期和指令周期的區別是什么

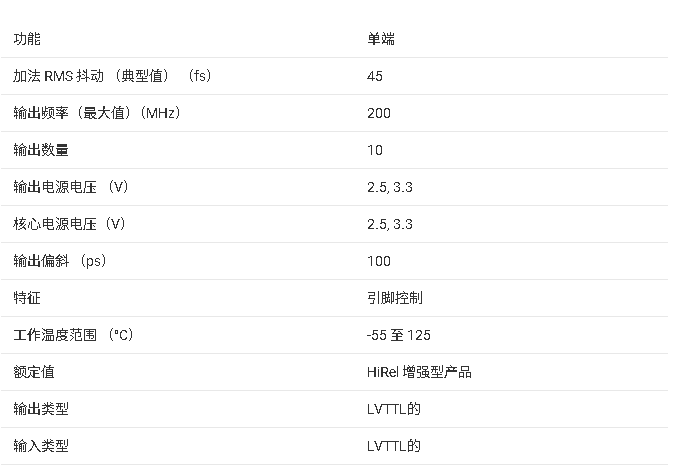

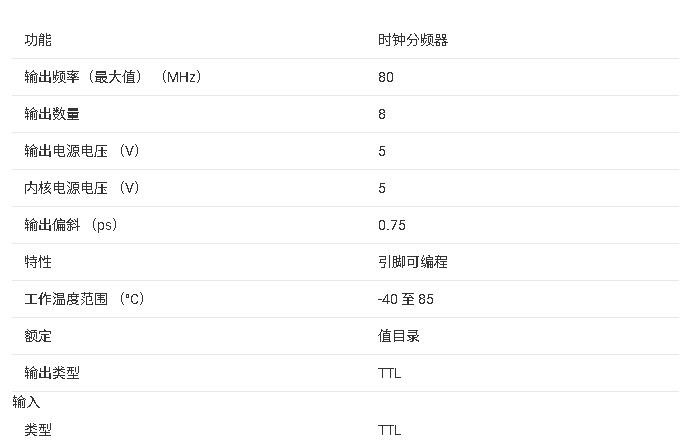

?CDCVF310 高性能時鐘緩沖器技術文檔總結

?CDCVF2310-EP 高性能時鐘緩沖器技術文檔摘要

DONE 變為高電平后我應給 CCLK 應用多少個時鐘周期

DONE 變為高電平后我應給 CCLK 應用多少個時鐘周期

評論