作者: ALINX

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

FPGA本身是SRAM架構的,斷電之后,程序就消失,那么如何利用FPGA實現一個ROM呢,我們可以利用FPGA內部的RAM資源實現ROM,但不是真正意義上的ROM,而是每次上電都會把初始化的值先寫入RAM。本實驗將為大家介紹如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作。

1.實驗原理

Xilinx在VIVADO里為我們已經提供了ROM的IP核, 我們只需通過IP核例化一個ROM,根據ROM的讀時序來讀取ROM中存儲的數據。實驗中會通過VIVADO集成的在線邏輯分析儀ila,我們可以觀察ROM的讀時序和從ROM中讀取的數據。

2. 程序設計

2.1 創建ROM初始化文件

既然是ROM,那么我們就必須提前給它準備好數據,然后在FPGA實際運行時,我們直接讀取這些ROM中預存儲好的數據就行。Xilinx FPGA的片內ROM支持初始化數據配置。如下圖所示,我們可以創建一個名為rom_init.coe的文件,注意后綴一定是“.coe”,前面的名稱當然可以隨意起。

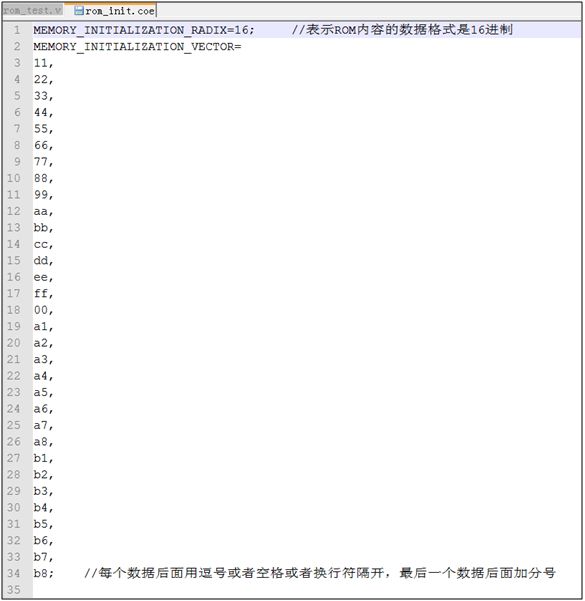

ROM初始化文件的內容格式很簡單, 如下圖所示。第一行為定義數據格式, 16代表ROM的數據格式為16進制。從第3行開始到第34行,是這個32*8bit大小ROM的初始化數據。每行數字后面用逗號,最后一行數字結束用分號。

rom_init.coe編寫完成后保存一下, 接下去我們開始設計和配置ROM IP核。

2.2 添加ROM IP核

在添加ROM IP之前先新建一個rom_test的工程, 然后在工程中添加ROM IP,方法如下:

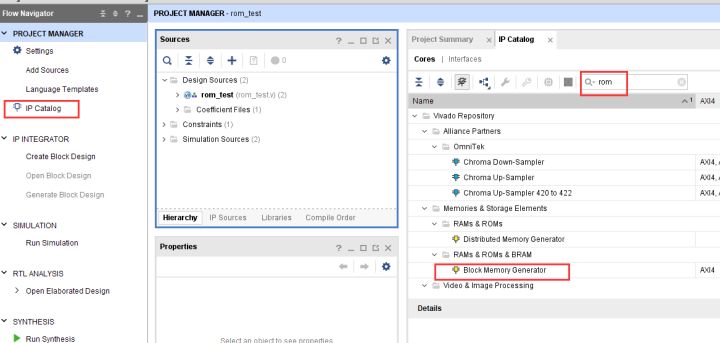

2.2.1 點擊下圖中IP Catalog,在右側彈出的界面中搜索rom,找到Block Memory Generator,雙擊打開。

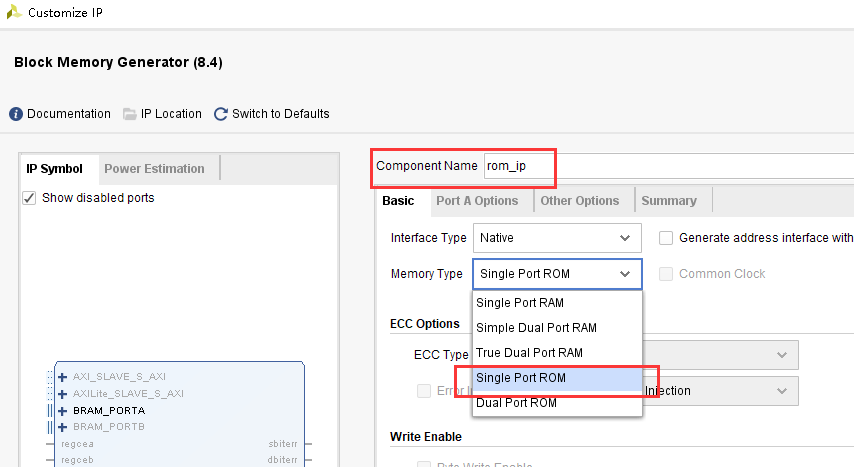

2.2.2 將Component Name改為rom_ip,在Basic欄目下,將Memory Type改為Single Prot ROM。

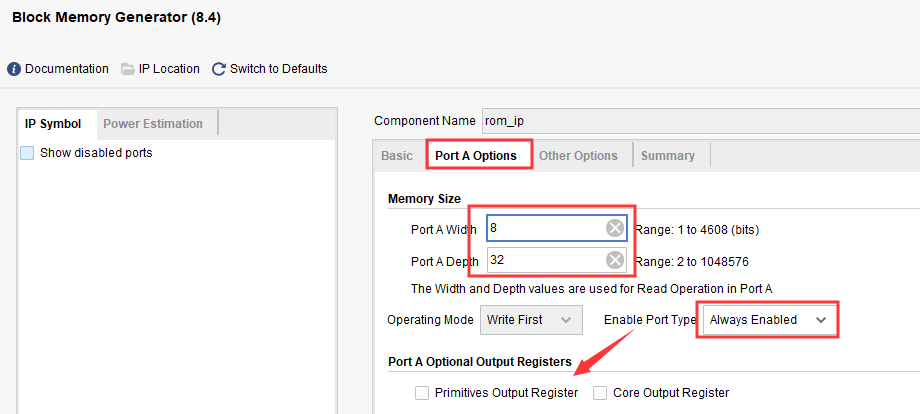

2.2.3 切換到Port A Options欄目下,將ROM位寬Port A Width改為8,將ROM深度Port A Depth改為32,使能管腳Enable Port Type改為Always,并取消Primitives Output Register

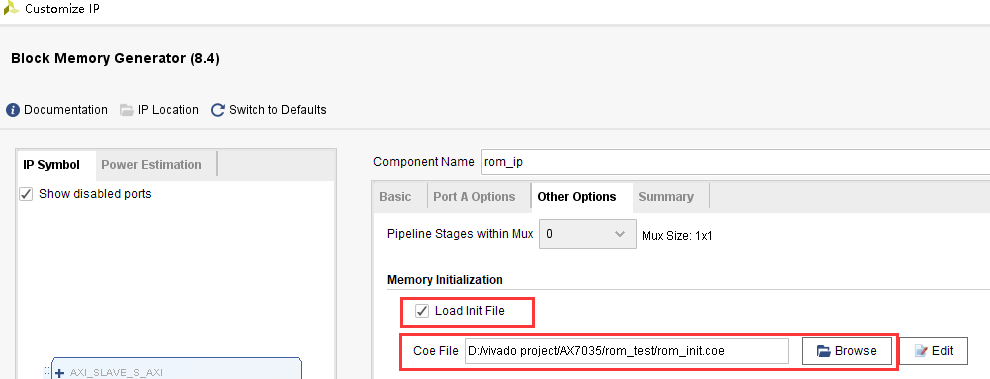

2.2.4 切換到Other Options欄目下,勾選Load Init File,點擊Browse,選中之前制作好的.coe文件。

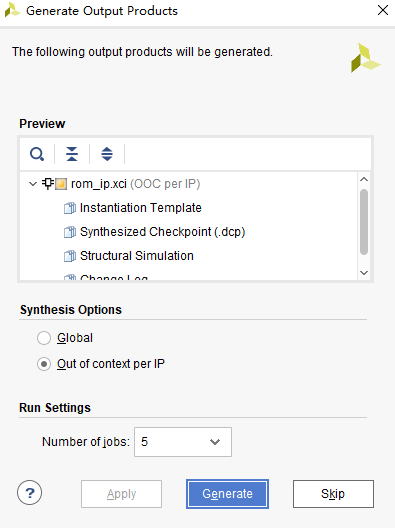

2.2.5 點擊ok,點擊Generate生成ip核。

3. ROM測試程序編寫

ROM的程序設計非常簡單, 在程序中我們只要每個時鐘改變ROM的地址, ROM就會輸出當前地址的內部存儲數據,例化ila,用于觀察地址和數據的變化。ROM IP的實例化及程序設計如下:

`timescale1ns/1ps module rom_test( input sys_clk, //25MHz時鐘 input rst_n //復位,低電平有效 ); wire[7:0] rom_data; //ROM讀出數據 reg [4:0] rom_addr;//ROM輸入地址 //產生ROM地址讀取數據 always@(posedge sys_clk ornegedge rst_n) begin if(!rst_n) rom_addr <=10'd0; else rom_addr <= rom_addr+1'b1; end //實例化ROM rom_ip rom_ip_inst ( .clka (sys_clk ),//inoput clka .addra (rom_addr ),//input [4:0] addra .douta (rom_data )//output [7:0] douta ); //實例化邏輯分析儀 ila_0 ila_m0 ( .clk (sys_clk), .probe0 (rom_addr), .probe1 (rom_data) ); endmodule

綁定引腳

##################Compress Bitstream############################

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]set_property PACKAGE_PIN AB11 [get_ports sys_clk]set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]create_clock -period 40.000 -name sys_clk -waveform {0.000 20.000} [get_ports sys_clk]set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]set_property PACKAGE_PIN W13 [get_ports {rst_n}]

4. 仿真

仿真結果如下,符合預期,與RAM的讀取數據一樣,數據也是滯后于地址一個周期。

5. 板上驗證

以地址0為觸發條件,可以看到讀取的數據與仿真一致。

審核編輯:何安

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636207

發布評論請先 登錄

詳細解釋Keil-MDK中Code、RO-data、RW-data、ZI-data的含義

單片機里的程序運行方式

中微愛芯2K FLASH ROM的AD型8位微控制器代理供應

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | ROM、RAM、FIFO 的使用

Simcenter FLOEFD BCI-ROM和Package Creator模塊

LMK03318如何使用TICS將程序燒錄進ROM?

基于FPGA搭建神經網絡的步驟解析

Simcenter Flotherm BCI-ROM技術:與邊界條件無關的降階模型可加速電子熱設計

飛凌嵌入式ElfBoard ELF 1板卡-uboot啟動流程分析之boot ROM階段

求助,關于FX3 ROM引導加載程序系統重啟問題求解

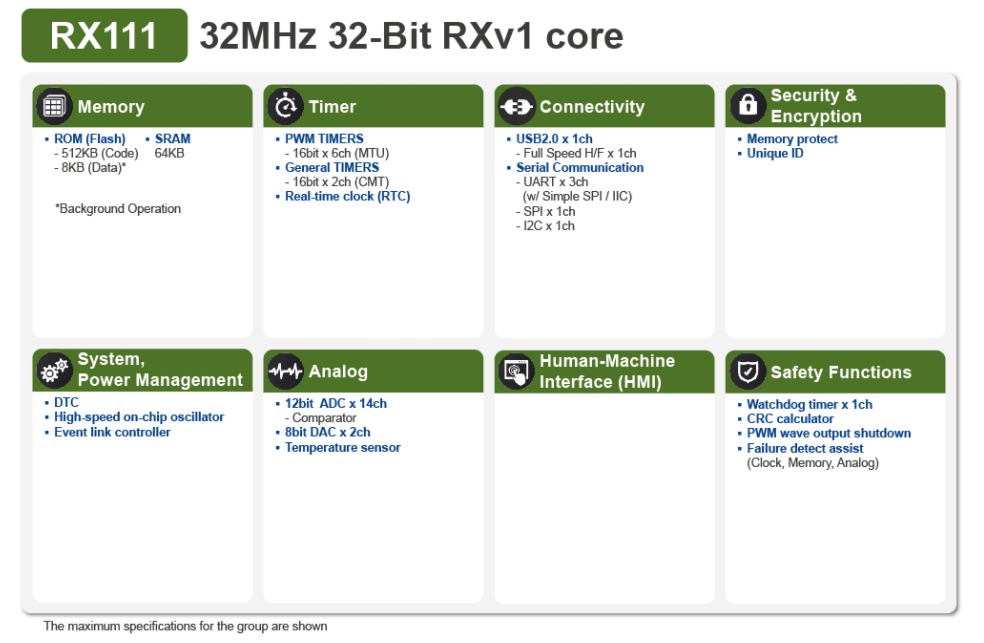

具有小容量ROM/低引腳數系列和內置USB 2.0的32位微控制器RX111系列數據手冊

如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作

如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作

評論