一、時鐘相關(guān)概念

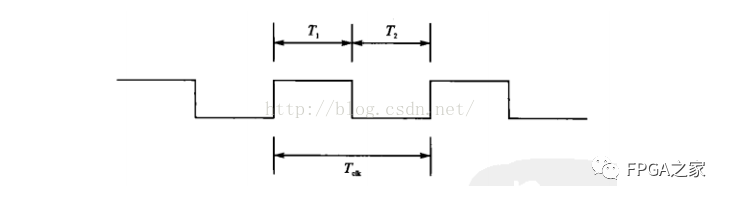

理想的時鐘模型是一個占空比為50%且周期固定的方波。Tclk為一個時鐘周期,T1為高脈沖寬度,T2為低脈沖寬度,Tclk=T1+T2。占空比定義為高脈沖寬度與周期之比,即T1/Tclk。

圖1 理想時鐘波形

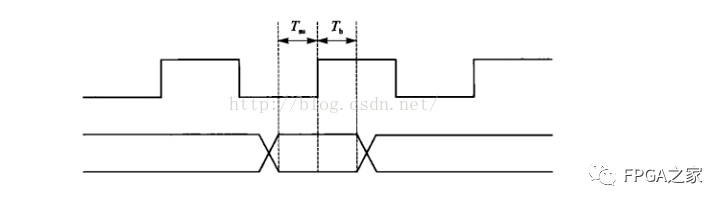

建立時間(Tsu):是指在時鐘上升沿到來之前數(shù)據(jù)必須保持穩(wěn)定的時間;

保持時間(Th):是指在時鐘上升沿到來以后數(shù)據(jù)必須保持穩(wěn)定的時間。如圖2所示。

圖2 建立和保持時間

一個數(shù)據(jù)需要在時鐘的上升沿鎖存,那么這個數(shù)據(jù)就必須在這個時鐘上升沿的建立時間和保持時間內(nèi)保持穩(wěn)定。

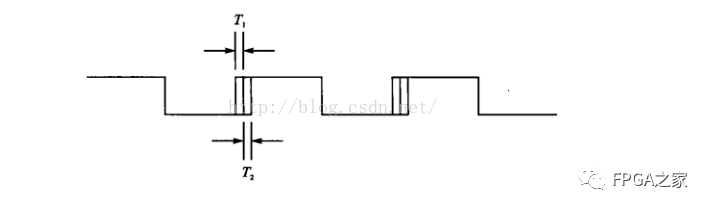

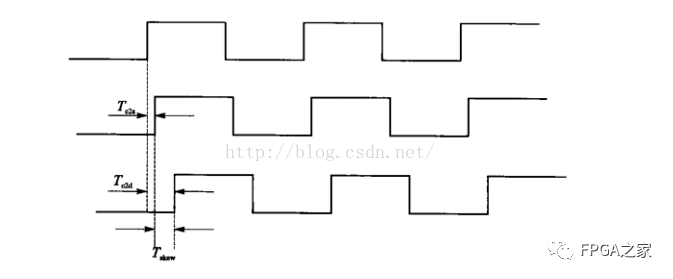

上面列舉的是一個理想的時鐘波形,而實際時鐘信號的分析要比這復(fù)雜得多。時鐘本身也具有一些不確定性,如時鐘抖動(jitter)和時鐘偏斜(sknew)等。時鐘的邊沿變化不可能總是理想的瞬變,它會有一個從高到低或者從低到高的變化過程,實際的情況抽象出來就如圖3所示,時鐘信號邊沿變化的不確定時間稱之為時鐘偏斜(clock skew)。再回到之前定義的建立時間和保持時間,嚴(yán)格的說,建立時間就應(yīng)該是Tsu+T1,而保持時間就應(yīng)該是Th+T2。

圖3 時鐘抖動模型

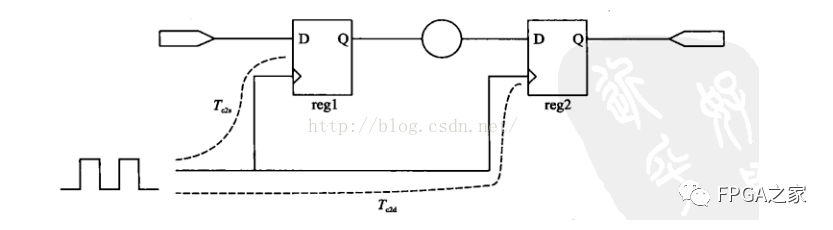

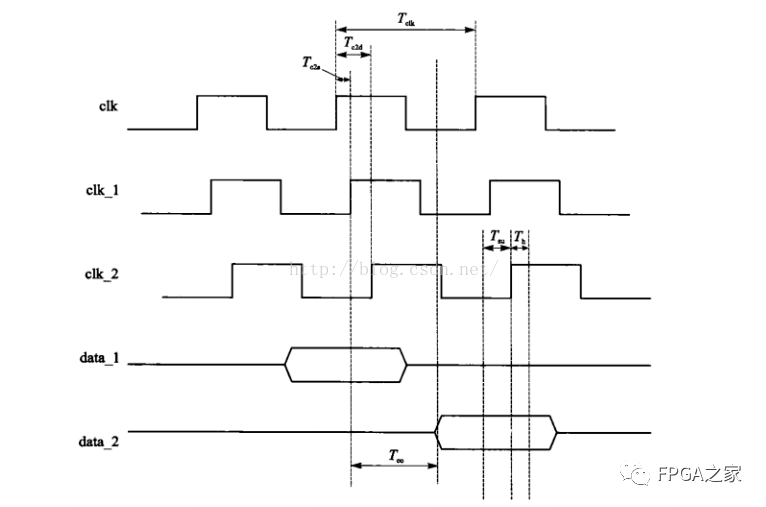

時鐘分析的起點是源寄存器(reg1),終點是目的寄存器(reg2)。時鐘和其他信號的傳輸一樣都會有延時。圖4中,時鐘信號從時鐘源傳輸?shù)皆醇拇嫫鞯难訒r定義為Tc2s,傳輸?shù)侥康募拇嫫鞯难訒r定義為Tc2d,時鐘網(wǎng)絡(luò)延時就定義為Tc2d與Tc2s之差,即Tskew=Tc2d-Tc2s。

圖4 時鐘偏斜的寄存器傳輸模型

圖5是時鐘偏斜模型的波形表示。

圖5 時鐘偏斜的波形圖

clk是源時鐘,可以認(rèn)為是一個理想的時鐘模型。clk_1是時鐘傳輸?shù)皆醇拇嫫鱮eg1的波形(延時Tc2s),clk_2是時鐘傳輸?shù)侥康募拇嫫鱮eg2的波形(延時Tc2d)。data_1是數(shù)據(jù)在源寄存器reg1的傳輸波形,data_2是數(shù)據(jù)在目的寄存器reg2的傳輸波形。

圖6 數(shù)據(jù)與時鐘關(guān)系

原文標(biāo)題:時鐘相關(guān)概念

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636245 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7335瀏覽量

94755 -

時鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134986

原文標(biāo)題:時鐘相關(guān)概念

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

原子鐘相較于晶振有哪些特殊優(yōu)勢

數(shù)字IC/FPGA設(shè)計中的時序優(yōu)化方法

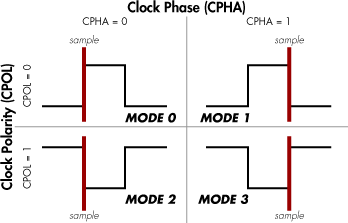

蜂鳥SOC的SPI外設(shè):如何修改SPI的時鐘相位和時鐘極性

FPGA的基礎(chǔ)概念和應(yīng)用場景

PLL技術(shù)在FPGA中的動態(tài)調(diào)頻與展頻功能應(yīng)用

FPGA芯片的概念和結(jié)構(gòu)

FPGA時序約束之設(shè)置時鐘組

AD9547雙路/四路輸入網(wǎng)絡(luò)時鐘發(fā)生器/同步器技術(shù)手冊

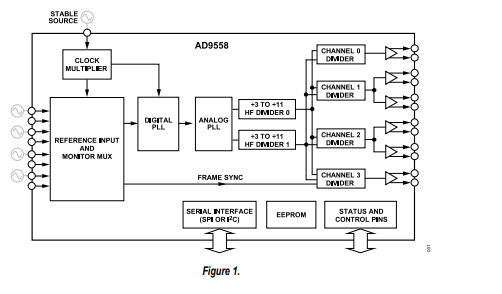

AD9558四路輸入多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

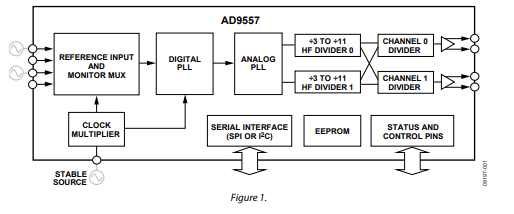

AD9557雙路輸入多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

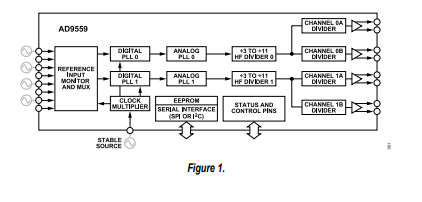

AD9559雙路PLL四通道輸入多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

AD9554四路PLL、四通道輸入、八通道輸出多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

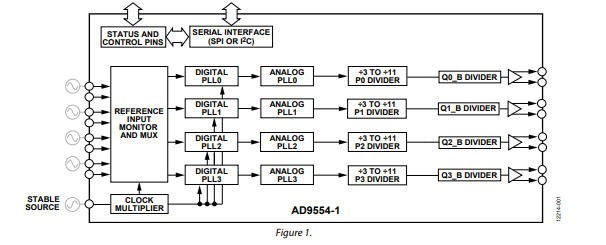

AD9554-1四路PLL、四通道輸入、四通道輸出多服務(wù)線路卡自適應(yīng)時鐘轉(zhuǎn)換器技術(shù)手冊

FPGA中的時鐘相關(guān)概念

FPGA中的時鐘相關(guān)概念

評論