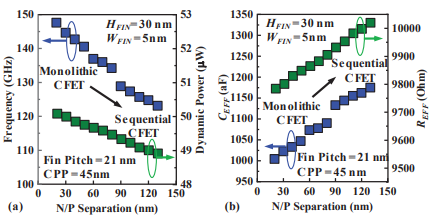

在去年六月舉辦的IEEE Symposium on VLSI Technology會議上,IMEC展示了基于N14工藝開發的單片集成CFET器件,由于N/P之間更加緊湊,相比較“順序法”制備的CFET,“單片法”制備的CFET具有更低的寄生電阻(REF)和電容(CEFF),從而獲得更高的性能增益。IMEC認為這一技術將會成1nm集成電路制造工藝的解決方案。

研究背景

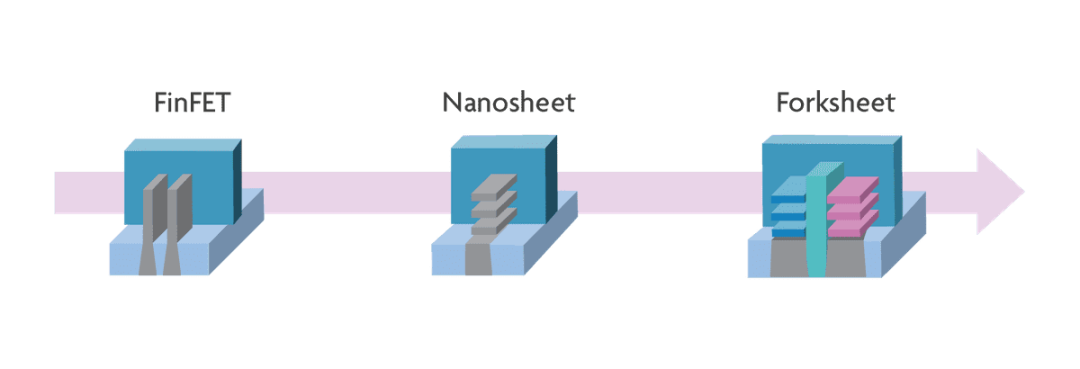

先進集成電路沿著摩爾定律發展,晶體管尺寸每隔一段時間就會縮小;但一種工藝結構總會接近其物理極限,當一種晶體管結構達到其縮小的物理極限,便需要新的器件結構以滿足更高性能、更小晶體管的需求,例如平面CMOS工藝在28nm節點之后便轉換為FinFET立體器件工藝;而當前FinFET走到5nm節點,GAA環柵晶體管也即將導入到三星和臺積電產線。

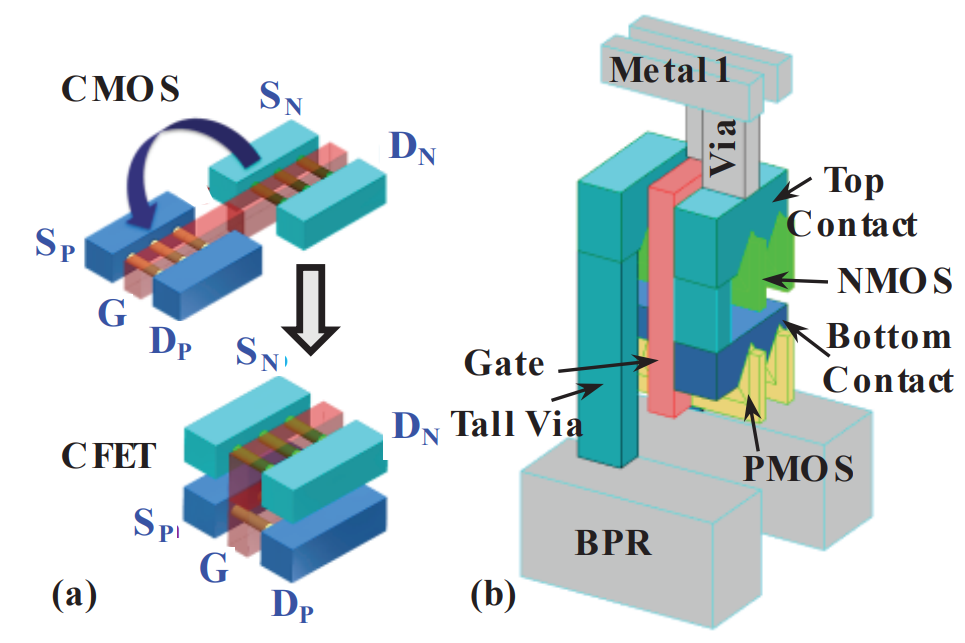

對于5nm以下的技術節點,目前已有多種晶體管結構的研究模型,其中最有前途的結構包括垂直堆疊的stacked Nanosheets結構、forksheets*結構以及CFET*結構,他們的共通點是先構建平面結構再構建垂直方向的結構。在CFET的制備工藝中,目前分為順序集成(sequential Integration)與單片集成(monolithic integration),在“順序法”中,nFET和pFET被制造在同一片晶圓上;而在“單片法”中,nFET和pFET在分離的晶圓上制造并進行“貼合”,從而可以針對該器件最佳化每個器件的制造流程。

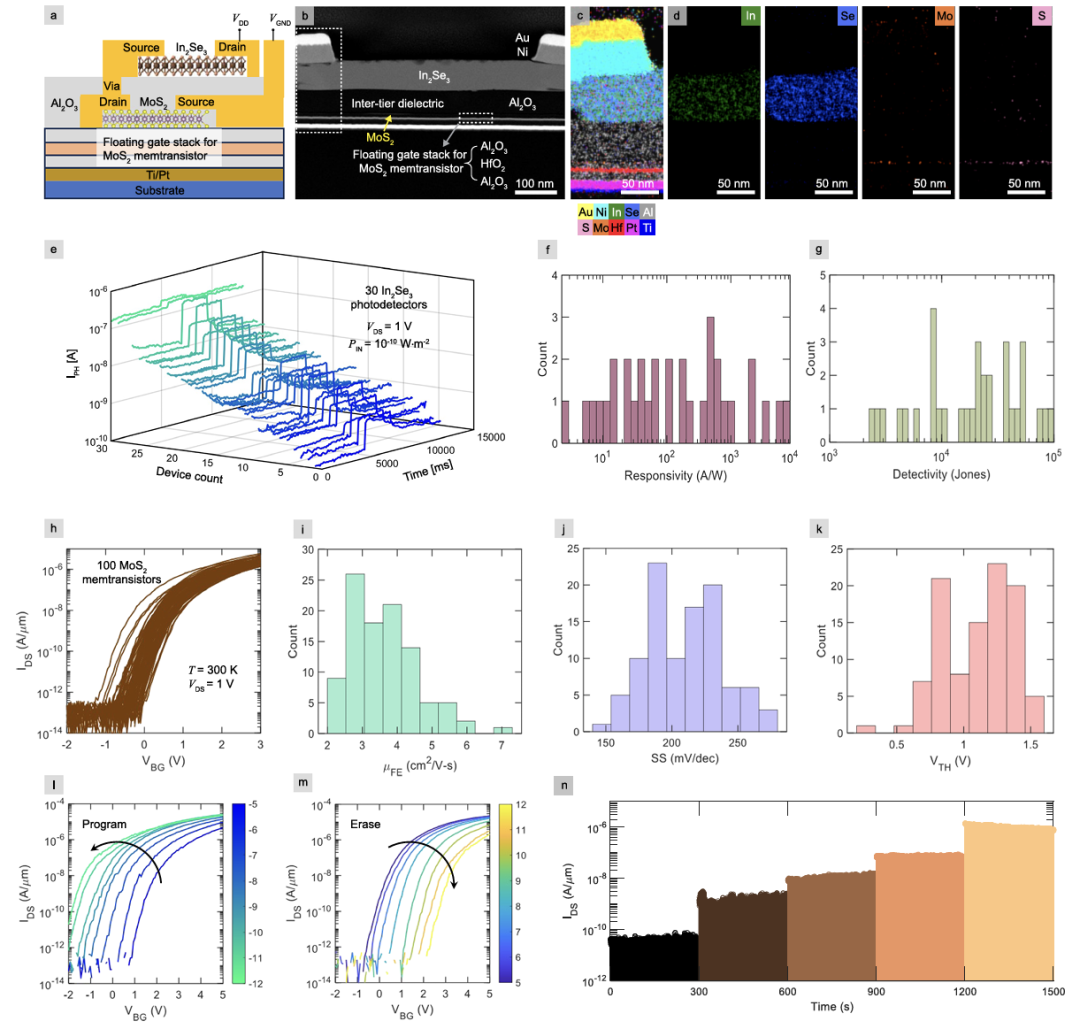

基于比利時IMEC提出的這一技術路線,他們基于其開發的N14 FinFET工藝進行CFET的開發制備,通過“單片法”工藝在12吋晶圓上實現了樣品的片上演示,并與“順序法”的數據進行了對比。

相關成果以“First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers”為題發表于2020年6月舉辦的2020IEEE Symposium on VLSI Technology,并于12月公開,S.Subramanian, M. Hosseini等32名來自IMEC研究中心和以色列nova半導體公司的研究人員為本文共同作者。

從FinFET到Forksheet

*Forksheet,是IMEC提出的一種新興器件架構,是Nanosheet的自然延伸。相比Nanosheet,其在溝道由叉形柵極結構控制,通過在柵極圖案化之前在p和nMOS器件之間引入“介電墻”來實現的。該墻將p柵溝槽與n柵溝槽物理隔離,從而允許更緊密的n到p間距。

*CFET(完整名稱Complementary FET),是將nMOS和pMOS縱向排列的一種新型晶體管結構,通過將Contact Poly Pitch(PP)做到最小,極大地縮小了CMOS和SRAM的面積。

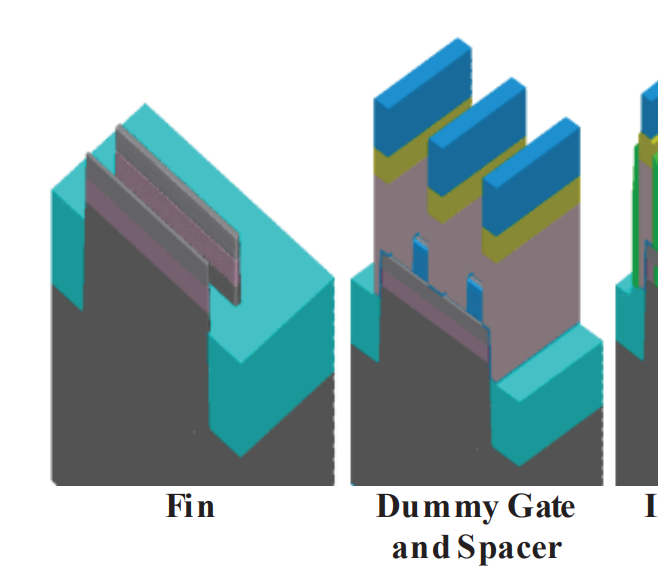

制備方法

IMEC團隊首次在300mm晶圓上演示了在底部pMOS FinFET上構筑nMOS nanosheet的CFET制備工藝。由于N/P之間更加緊湊,相比較“順序法”制備的CFET,“單片法”制備的CFETs具有更低的寄生電阻(REFF)和電容(CEFF),從而獲得更高的性能增益。

CFET結構示意圖

滑動查看:CFET制備工藝中的關鍵步驟

RO性能與寄生參數測試

滑動查看:制備過程中晶體管橫截面的TEM形貌像

前景展望

本項研究是集成電路新工藝研發的一大重要成果,“單片法”CFET器件以更緊湊的空間提供了更佳的晶體管理論性能,被認為是1nm工藝上的重要技術路線之一,IMEC提出并局部驗證了這一方向的實際性能表現,對于先進工藝的發展有著舉足輕重的指導意義,新材料、新型器件結構以及多種路線混合(例如異質CFET),究竟哪一種解決方案會贏得晶圓制造廠的青睞并成為最終產品的答案,也很值得期待。

團隊介紹

IMEC,全稱:Interuniversity Microelectronics Centre,即比利時微電子研究中心,是一家成立于?1984?年的科技研發中心,?總部設在魯汶。IMEC?的戰略定位為納米電子和數字技術領域全球領先的前瞻性重大創新中心,與?IBM?和英特爾(Intel)并稱科技界的“3I”。

IMEC?從?2004?年起參與了從45nm到7nm的芯片前沿技術的研發,核心科研合作伙伴覆蓋了全球幾乎所有頂尖信息技術公司,如英特爾、IBM、德州儀器、應用材料、AMD、索尼、臺積電、西門子、三星、愛立信和諾基亞等,擁有來自近80個國家4000名研究人員。

在國內,以中芯國際為代表的晶圓代工企業也與IMEC有著緊密合作:2015年中芯國際先進制程研發項目簽約儀式在人民大會堂舉行,IMEC、華為和高通在合作方中各占一席,四方共同進行標準單元庫的定義、優化和制造工藝的開發。

原文標題:科研前線 | IMEC首次在12吋晶圓上實現3D CFET集成

文章出處:【微信公眾號:芯片揭秘】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

3D

+關注

關注

9文章

3011瀏覽量

115088 -

晶圓

+關注

關注

53文章

5411瀏覽量

132312 -

IMEC

+關注

關注

0文章

60瀏覽量

22846

原文標題:科研前線 | IMEC首次在12吋晶圓上實現3D CFET集成

文章出處:【微信號:ICxpjm,微信公眾號:芯片揭秘】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

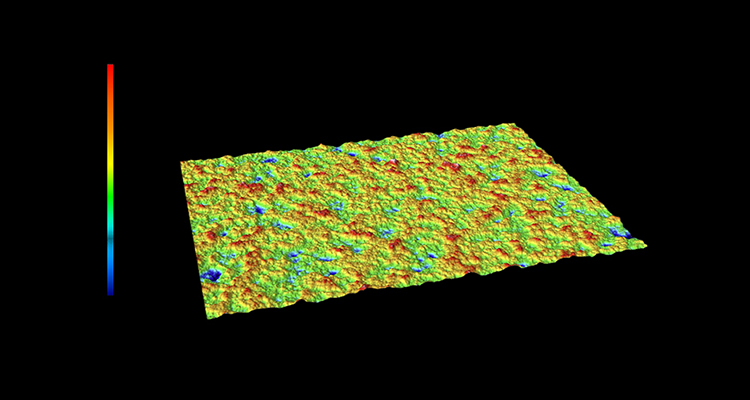

晶圓表面的納米級缺陷光學3D輪廓測量-3D白光干涉儀

2D材料3D集成實現光電儲備池計算

三維集成電路與晶圓級3D集成介紹

白光干涉儀在肖特基二極管晶圓的深溝槽 3D 輪廓測量

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

iTOF技術,多樣化的3D視覺應用

下一代高速芯片晶體管解制造問題解決了!

IMEC首次在12吋晶圓上實現3D CFET集成

IMEC首次在12吋晶圓上實現3D CFET集成

評論