作者:邢萬,俞珍傳,賀磊,陸鋒

1 引言

隨著IC設計方法與工藝技術的不斷進步,集成電路結構和功能日益復雜,測試問題成為必 須考慮的關鍵問題,測試成本作為整個IC產品成本的主要組成部分,也受到了極大的重視。由 于國內自動測試設備(Automatic testing EquIPMent)主要依賴進口,價格昂貴,測試圖形產生, 特別是測試量產過程的花費(例如測試時間),就顯得尤為重要。為了使測試成本保持在合理 的限度內,最有效的方法就是采用可測性設計(Design For Testibility)。可測性設計(DFT) 是適應集成電路的發展要求所出現的一種技術,主要任務是通過適當的設計重構或調整來提高電路整體性能的輔助設計方法,其核心是通過適當的前期代價來提高電路的可測性,即可控制 性和可觀察性,降低產品的測試成本。本文設計的RISC_CPU是一個復雜的數字邏輯電路,采用DFT策略可以很好地解決測試問題。

2 CPU 結構

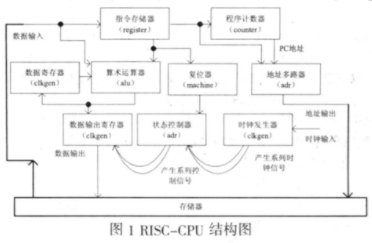

本文設計的RISC_CPU,主要分為幾個模塊,各個模塊之間的互連關系如圖1所示。

1. 時鐘發生器(clkgen):產生一系列的時鐘信號送往 CPU 其他部件;

2. 指令寄存器(register):存儲指令;

3. 累加器(accum):存放算術邏輯運算單元當前的結果,它也是算術邏輯運算單元雙目運算中的一個數據來源;

4. 算術邏輯運算單元(alu):根據輸入的不同操作碼分別實現相應的加、與、讀、寫、異或,跳轉等指令;

5. 數據輸出控制器(datactl):控制累加器的數據輸出;

6. 狀態控制器(control):CPU 的控制核心,用于產生一系列的控制信號,啟動或停止某些部件;

7. 程序計數器(counter):提供指令地址,以便讀取指令;

8. 地址多路器(adr):選擇輸出的地址是 PC(程序計數)地址還是跳轉的目標地址;

9. 狀態復位器(machine),狀態控制器復位信號生成模塊。

3 基本概念釋義

3.1 掃描

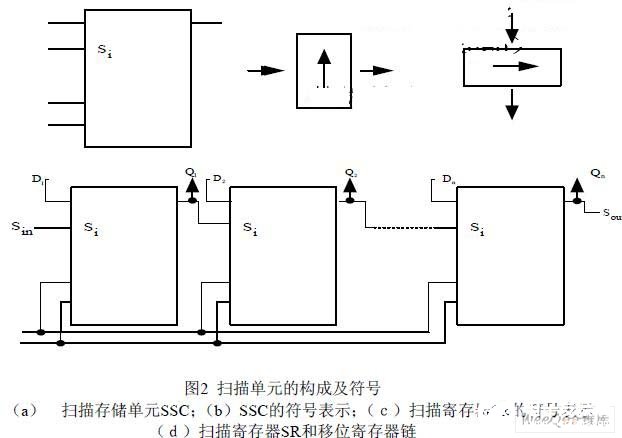

掃描設計方法是通過將電路中的時序元件替換為相應的可掃描的時序元件(即掃描單元), 然后將它們串聯起來,形成一個從測試輸入到測試輸出的串行移位寄存器。這樣,測試數據由 測試輸入,通過移位,到達要控制的單元;內部數據,再次通過移位,由測試輸出的端口,觀 察結果。

3.2 基于沿觸發的掃描單元結構

圖2是掃描單元構成,其工作原理是:在掃描模式控制下實現數據的掃描輸出,即T/N =1 時,掃描數據從i s 輸入,在時鐘作用下從Q輸出,輸出的是掃描輸入的數據。而當T/N = 0時, 掃描單元處于正常工作模式,也就是在時鐘作用下從Q輸出,但輸出的是單元正常工作的數據。

4 掃描設計

4.1 自動掃描單元替換

RISC_CPU有近萬個時序單元,為了獲得較高的故障覆蓋率,采用了全掃描的設計方案, 使用Synopsys公司Design Compiler自動完成測試插入功能,用最基本的掃描觸發器來替換時序 單元,共設計了9條掃描連, 測試激勵使用Synopsys公司的TetraMAX測試產生工具產生出來:共 產生組合測試向量1413個,其故障覆蓋率達到95.06%;產生時序測試向量147個,覆蓋率增加到 97.39%。在剩余2.61%未覆蓋的故障中,1.4%的故障是電路設計中的冗余故障。

4.2 掃描移位測試

測試使能端test_se=1,將電路置為掃描模式,每條掃描鏈上的所有觸發器數為n,從scan_in送 入一個長為n+4的輸入序列:00110011…0011。這個序列將在每個掃描觸發器中產生所有可能的 4種跳變信號情況:0→0,0→1,1→1,1→。從scan_out可以觀測到信號跳變情況。這個測試覆 蓋了觸發器中大多數單故障型故障,從而確保掃描鏈的移位操作不出錯。由于9條掃描鏈可以并 發測試,以最長掃描鏈的長度為準,完成移位測試的測試時間約為582=(289*2+4)個測試時鐘 周期。

4.3 固定型故障的測試

單固定型故障是芯片測試的主要目標。由于我們采用全掃描設計,因此對大部分電路可以 使用組合電路的測試方式完成,即測試輸入數據通過掃描鏈準備好后,只經過一個節拍就進行 輸出響應的捕獲。但是,由于RAM的存在,讀寫RAM的信號不可觀測和控制,因此對于最靠近 RAM的一級觸發器到RAM之間的組合邏輯,稱為RAM的陰影邏輯(shadow logic),無法通過組 合電路的測試方式完成。解決這個問題一般有兩種方式,一種方式是在RAM外部插入測試點來 提高陰影邏輯的可控制性和可觀測性, 由于這會影響訪存RAM的性能,這種方案在該 RISC_CPU中不可取。另一種方式被采用,即對RAM建立等價功能模型,這將導致需要用測試 時序電路的方式來測試陰影邏輯。

為了保證測試時鐘的可控性,在芯片測試時需要將測試控制信號test 置為有效(test=1),使 芯片工作在測試方式。對一個芯片的測試過程如下:在掃描模式下,測試激勵通過一條或幾條 掃描的scan_in管腳,串行移位到響應的掃描觸發器。當一個測試的所有輸入激勵準備好后,使 用系統時鐘將測試激勵送入被測邏輯。一個時鐘周期(對組合測試)或幾個時鐘周期(對時序 測試)后從被測模塊的輸出端口所在的掃描鏈上,將輸出信號依次串行移位到相應的scan_out 引 腳,將讀出的數據與期待的輸出比較,以判斷被測邏輯中是否存在故障。

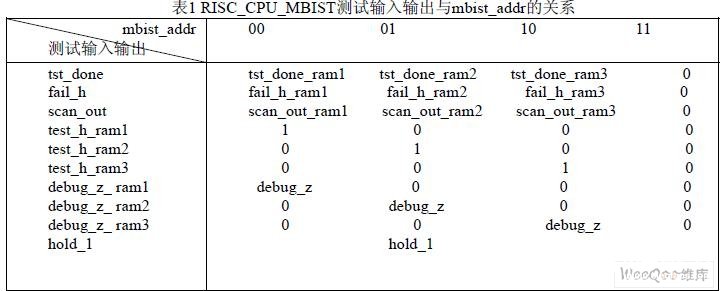

5 存儲器測試

本文采用了Mentor 公司的MBIST 插入工具MBISTArchitect。MBISTArchitect 可以創建和 連接RTL 級BIST 邏輯到待測芯片中。RISC_CPU 的存儲器由RAM1、RAM2、RAM3 三塊大 小分別為20*128 字節、64*128 字節、64*48 字節的存儲器構成面積約為45%,我們用三塊帶有 比較結構的MBIST 電路,這三塊MBIST 是通過mbist_addr 和MBIST 模塊來控制的,三塊MBIST 電路共享測試控制信號hold_1 和診斷控制信號debug_z 以及三個測試輸出tst_done、fail_h 和 scan_out(錯誤定位即診斷數據輸出)。MBIST 測試使能信號由mbist_addr 解碼得到,從而決定三塊MBIST 電路的工作次序以及最終的芯片測試輸出,他們之間的關系由表1 給出。

由表1可知:當mbist_addr為00時,ram1的MBIST電路的控制信號即為外部相應輸入的控制 信號,其他兩個ram模塊的MBIST電路的控制信號輸入置為0。異步復位置位有效,系統處于ram1 的測試狀態,系統測試輸出即為ram1的測試輸出;當mbist_addr為01時,系統處于ram2的測試狀 態,系統測試輸出即為ram2的MBIST測試輸出;當mbist_addr為10時,系統處于ram3的測試狀 態,系統測試輸出為ram3的MBIST測試輸出。

為了得到每一塊RAM的測試結果,我們將MBIST的測試結果通過第九條掃描鏈移出,在多 個分組測試中,測試時間最長的執行MBIST算法大約需要1044800個時鐘周期,加上初始化和測 試完成后將測試結果掃描移出的時間,共需要的時鐘周期數不超過10445900個,如果測試時鐘 的頻率為20MHZ,則測試時間約為0.52秒。借助于BIST,對嵌入式存儲器的單固定型故障、開 路故障、地址譯碼故障均獲得了100%的故障覆蓋率,達到了預定的要求。

6 結束語

本文合理地選擇了邊界掃面和內建自測試方式,根據時鐘域劃分各個功能單元,修改設計, 消除了設計規則違反,選擇了適當的綜合流程,在對設計負面影響不大的情況下,僅增加了0.2% 的時序消耗和0.02%的面積消耗,取得了良好的可測性效果,達到了芯片邏輯的97.39%的單固 定型故障覆蓋率,能夠監測到RAM中100%的單固定型故障覆蓋率,滿足了芯片生產測試需求。

責任編輯:gt

-

控制器

+關注

關注

114文章

17796瀏覽量

193378 -

IC

+關注

關注

36文章

6411瀏覽量

185708 -

cpu

+關注

關注

68文章

11281瀏覽量

225098

發布評論請先 登錄

全球首創!RISC-V+AI架構高性能服務器CPU成功點亮

Jim Killer掌舵,Tenstorrent CPU IP進軍高性能計算,AI令RISC-V勢在必得

高通收購Ventana Micro Systems,深化RISC-V CPU技術專長

Tenstorrent與AutoCore宣布戰略合作,以AutoCore.OS賦能高性能RISC-V汽車計算

那么龍芯CPU性能如何呢?

提高RISC-V在Drystone測試中得分的方法

DFT算法與FFT算法的優劣分析

智芯公司RISC-V高性能CPU芯片獲得權威認可

RISC-V架構CPU的RAS解決方案

RISC-V架構下的編譯器自動向量化

借助DFT技術實現競爭力最大化

DC-ROMA RISC-V AI PC 正式發布!

采用DFT策略提高RISC_CPU的性能設計

采用DFT策略提高RISC_CPU的性能設計

評論