電子發燒友網報道(文/黃晶晶)由被譽為“硅仙人”的傳奇CPU架構師Jim Keller創辦的Tenstorrent公司,作為高性能RISC-V CPU與AI 計算領域的翹楚備受關注。近日,Tenstorrent 在上海舉辦TT Blueprint China技術峰會,官宣TT-Ascalon高性能RISC-V CPUIP正式上市,并介紹全系列IP產品。Tenstorrent十分重視中國市場的開拓,與Corelab、希姆計算公司等建立合作伙伴關系,共同推動RISC-V 在汽車、機器人以及服務器等高性能 AI 計算領域的廣泛落地。

Jim Keller創辦Tenstorrent公司的初衷正是希望提供基于開源架構的RISC-V IP、拓展性優秀的AI硬件和完全開源的AI軟件棧,以幫助芯片設計降低成本、提高開發成功率。

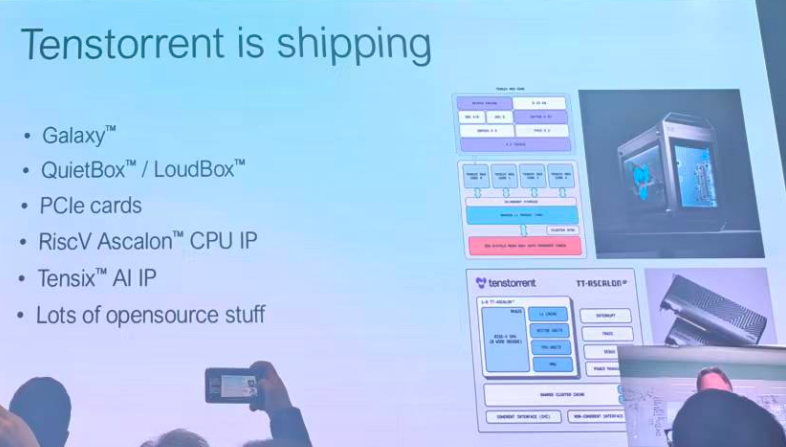

Tenstorrent正在出貨的產品包括應用于高端服務器的Galaxy AIIP、小型服務器的QuietBox(采用水冷方案,適用于辦公環境),以及LoudBox(采用風冷方案,適用于大型機架),此外還有PCIe卡、RISC-V Ascalon CPU IP、以及TensixAI處理器等等,并且明年Tenstorrent將進行IP產品線的重大升級。

同時,Tenstorrent還提供開源軟件棧,開源AI編譯器、AI模型、算子庫和底層編程。在下一代AI方案中,Tenstorrent將發布芯粒OCA,芯粒將單芯片分割成更小的部分,開發者能夠復用多個芯粒,而專注于AI、CPU處理器核心部分的開發,從而提高人工智能解決方案的易構建性,并降低成本。

值得一提的是,針對中國市場Tenstorrent的IP完全滿足出口合規性要求,Tenstorrent還積極參與RISC-V的大學合作計劃。

Ascalon高性能RISC-V IP

RISC-V是一種開源指令集架構(ISA)規范,正在全球范圍內被廣泛采用,此前在IoT領域已有不少RISC-V芯片出貨,但鮮有產品在高性能計算領域取得突破。Tenstorrent工程副總裁Divyang Agrawal先生表示,Tenstorrent高性能RISC-V CPUTT-Ascalon具備真正的高性能計算能力,性能超越市場上任何現有RISC-V CPU,Ascalon在眾多采用不同專有指令集架構的高端處理器中穩居領先行列。

Ascalon通過業界標準SPEC CPU基準測試驗證,單核性能達到22 SPECint? 2006/GHz、>2.3 SPECint? 2017/GHz和>3.6 SPECfp? 2017/GHz,并可在Samsung SF4X工藝節點下實現>2.5 GHz主頻,充分展現了其強大的設計和在先進工藝節點上的可擴展性。

Ascalon具有高度擴展,產品系列覆蓋從AscalonX到S,其中S針對中端核心,對標Cortex A78,A710級別的性能。高端產品方面,Ascalon X擁有極致性能,對標Neoverse V3。

Ascalon完全兼容RVA23規范,并集成高性能RVV1.0矢量引擎,支持硬件虛擬化、先進內存管理和高級中斷架構。此外,Ascalon還具備安全性和RAS(可靠性、可用性和可維護性)特性,包括側信道攻擊防護。Tenstorrent同步宣布,Ascalon已全面支持GCC、LLVM和Qemu,并已完成上游合入,開發者和客戶可立即部署使用。

現場demo演試,基于單核心AscalonCPU運行90年代《毀滅戰士》游戲十分順暢,其加速器的功能直接由Ascalon的矢量單元運行,無需GPU。

Ascalon為服務器、AI基礎設施、汽車高性能計算(HPC)及高級駕駛輔助系統(ADAS)等廣泛應用場景提供完整的高性能解決方案。例如在網絡市場存在大量定制化需求,在存儲、智能網關、深度學習等領域需要卸載主要計算任務,這些任務可由RISC-V架構的渲染器或基于RISC-V的IT系統構建。

Atlantis高性能SoC芯片平臺

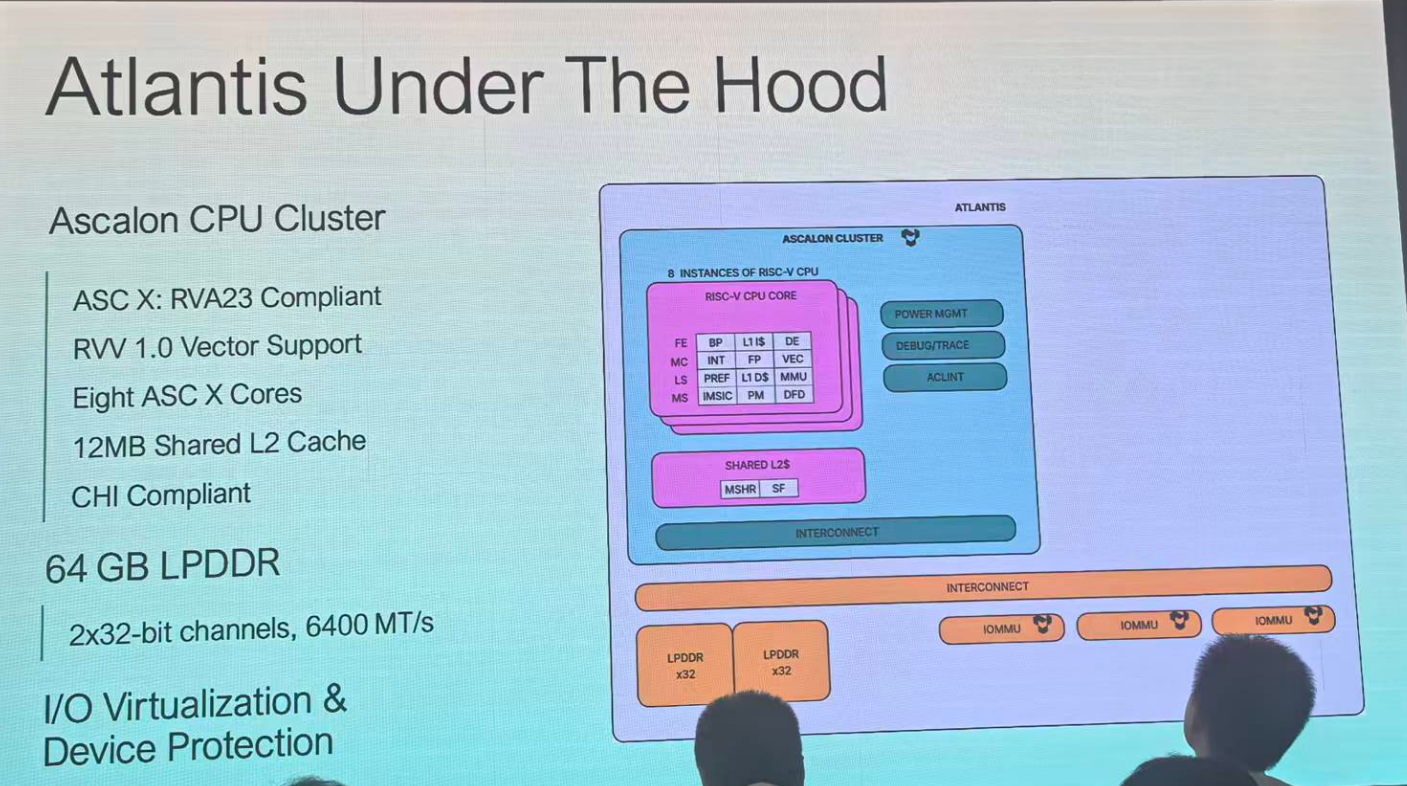

Tenstorrent已與CoreLab建立合作伙伴關系,推動區域客戶支持和設計優化,幫助客戶高效采用并快速部署其IP。Atlantis是高性能SoC芯片平臺,圍繞AscalonCPU構建集群。

從AscalonCluster來看,Ascalon可配置1-8個高性能核,每個核心搭配L1級緩存,多個核心共享L2級緩存。Tenstorrent首席工程師Sajosh Janarthanam表示,核心計算的實時性能有賴于內存帶寬,我們配置64GBLPDDR內存運行速度可達6400MT/s,在Atlantis平臺配備雙通道LPDDR內存,高性能且低功耗。可利用軟件輕松擴展并添加額外的I/O設備,包括20通道的PCIe Gen4接口,可以將其配置為16x1、4x5,或者2x8和1x4。USB3.1和USB2.0接口以滿足設備的連接需求。配置網絡控制功能,兩個千兆以太網接口、SDA端口等。Atlantis配置GPU IP來自Imagination GPUBMX Force D40,視頻解碼器、多個顯示端口、支持MP和SDMA協議,還有中斷控制器用于處理來自設備和加速器的所有中斷。并且添加加密引擎以及隨機數生成器等。

在軟件生態系統方面,Tenstorrent推出專有的調試功能,也與第三方供應商合作建立Atlantis的立方體模型用于測試、調試等。此外還提供開放的SVA功能用于內核支持,優化部分工具鏈例如LLVM、GCC以及開放的OCD腳本用于自動代碼的分析等等。針對目前現有的RISC-V開發平臺不允許軟件開發者進行高性能軟件開發、運行測試反饋慢等問題,Tenstorrent的生態平臺能大幅縮短反饋時間,加速開發者的設計進程。

Tenstorrent不斷豐富自有的IP體系,除了CPU IP之外還提供系統IP,眾多子系統IP加持下的CPU組合、AI加速器組合等加速了客戶的驗證,助力產品快速上市。

希姆計算CEO梅迪認為,RISC-V在平衡可編輯性和通信加速能力上幾乎是最好的方案,但是單純的AI計算架構已經難有巨大突破,業界紛紛從單一芯片架構轉到GPU、AI芯片、網絡芯片的聯合研發和優化上面。未來AI芯片發展方向必定是AI芯片和CPU的強強聯合。基于這樣的趨勢,希姆計算與Tenstorrent、CoreLab建立密切的合作伙伴關系。希姆計算在成立的六年時間里研發兩代AI芯片,出貨超過1萬張AI加速卡。合作三方基于硬件基礎在系統層面、網絡連接協議等做進深入的交互融合將產生更強大的生命力。

CoreLab Technology董事長吳雄昂指出,CoreLab平臺極大地加速計算能力的實現,可以預制近80%的軟硬件,讓開發更高效。CoreLab通過?開放可定制計算系統平臺(OpenCSS)?解決AI芯片的碎片化問題,支持客戶在統一RISC-V基座上靈活定制加速器(如NPU、GPU),實現性能成倍提升。這個面向開發者的平臺,支持AI PC、邊緣服務器等應用。Tenstorrent提供高性能CPU的解決方案、希姆計算的AI加速卡可插接到Atlantis平臺上。該平臺還面向機器人市場,開發者能夠將機器人的一些算法部署到Atlantis平臺上進行優化。

Alexandria汽車芯片IP

Tenstorrent觀察到快速發展的新能源汽車行業的痛點在于,缺乏通用編程模型。Tenstorrent力圖基于Ascalon和Alexandria的平臺采用相同的通用編程模型來打通數據的訓練和推理。這套編程模型可以跨越不同代際不同層次的技術,而這正是RISC-V的靈活性開放性所賦予的。

TT Alexandria是 Tenstorrent 推出的一款高性能 RISC-V 汽車和機器人解決方案。Alexandria 以Ascalon處理器系列為基礎打造,這一高性能IP添加功能安全特性。Alexandria 具備鎖步(Lockstep)能力,可防護瞬態和永久性故障。Alexandria 所構建的安全特性使其能夠支持 ADAS(高級駕駛輔助系統)、IVI(車載信息娛樂系統)和中央計算功能。它可以針對各種需求進行配置,并以 ISO 26262 認證為目標。

Alexandria 集成了硬件故障保護,以提供混合模式(Hybrid)、分離模式(Split)和鎖定模式(Lock Modes);它優化了軟件測試庫(STL)和所有緩存上的內存保護,以及接口保護。Alexandria 適用于數字座艙、IVI、ADAS 和車輛中央計算。憑借這一系列特性,Alexandria 已經為用 RISC-V 應對汽車領域的挑戰做好了充分準備,并滿足市場對于一款高性能 RISC-V 設計的需求。

此外,Alexandria 將繼續支持 Tenstorrent 建立一個真正的開放生態系統的愿景。在軟件定義汽車的時代,Tenstorrent與AutoCore達成合作,AutoCore將以其旗艦產品AutoCore.OS賦能Tenstorrent高性能RISC-V處理器平臺TT-Ascalon。這標志著成熟汽車軟件與高性能RISC-V架構CPU及AI平臺深度融合的里程碑。雙方聯合打造的該解決方案打破了傳統封閉架構的壟斷。Tenstorrent堅持開放性的解決方案,支持指令集架構(ISA)擴展及功能安全(FUSA),結合AutoCore靈活的軟件配置,為主機廠(OEM)帶來前所未有的自由度,讓客戶可以針對特定應用進行優化。

據悉,Alexandria IP計劃在 2026 年第三季度發布,包括四核、4 兆字節的 ASIL B CPU IP,以及八核、12 兆字節的 ASIL B CPU IP兩款。還將推出八核、12 兆字節的 ASIL D 和 B 兼容 CPU IP。

開放芯粒生態系統OCA

每一次科技浪潮幾乎都伴隨著一次芯片技術的飛躍,而隨著 AI 的發展,人們對芯片的算力、存儲都有了更高一個階層的要求。隨之而來的是芯片復雜度的提升,同時也是設計成本的極度提升。根據 IBS 的研究報告,如果從頭設計一款 2 納米的芯片,需要耗費7億美元。這樣的設計開銷讓許多量不是特別大的芯片,幾乎沒有辦法使用2納米或3納米的工藝。隨著設計成本的提高,芯片項目的成功率也在逐步降低,這和芯片本身的復雜度緊密關聯。

一方面是設計成本的節節攀升,另一方面是成功率的穩步下降,這直接導致了越來越少的企業設計可產品化的高性能芯片。Tenstorrent 作為一個初創公司致力于高性能芯片,在經過多年的探索之后,認為有必要主導的一個開放芯粒生態系統Open Chiplet Atlas Ecosystem,簡稱 OCA 生態系統。

經濟學之父亞當·斯密在他的著作《國富論》中提到:“分工是人類生產力的提高的第一要素。而開放的貿易交換是將分工轉換成生產力的必要條件”。如果把樸素的經濟學理論套用在芯片產業,那么芯粒(Chiplet)就是我們新芯片設計的再分工。而一個開源的生態系統,就是將這個芯粒轉換成更高生產力的必要條件。

例如,在設計一顆芯粒的解決方案中,我們需要設計的僅僅是那一顆AI芯粒。所有其他功能都已經是現成的芯粒,你只需要拿來用。這樣設計成本自然可以極大地降下來。同時,Tenstorrent 還提供芯粒的開發平臺,可以進一步降低芯片開發成本。

Tenstorrent高級主任工程師Zhimin chen介紹,Tenstorrent 從六個方向支持OCA 生態系統,包括OCA 架構,它全面保障芯粒之間的互可操作性。OCA Harness,它是一個開源的芯粒系統邏輯的實現,它和架構的要求完全吻合。OCA Compliance,是一系列用于芯粒合規性的測試。OCA Chiplet Shell,是OCA Harness 和 Tenstorrent 連接芯粒之間的模塊結合,目的是最大限度地簡化芯粒設計當中的復雜度。OCA Chiplet,一個生態系統必須有很多芯粒,Tenstorrent 正在與合作伙伴全力開發OCA 芯粒。最后是OCA 芯粒模型,它包括功能模型和性能模型,主要可以幫助大家在設計芯粒時做協同仿真。這應該是現今業界對于一個芯粒生態系統最完整的支持。

截止目前,Tenstorrent 已經發布OCA 架構的 0.7 版本,以及 AXI over UCIe 的0.6 版本。已經得到來自業界非常廣泛的支持,包括芯片設計公司、IP 提供商、芯片設計服務公司、Foundry、系統集成商、科研機構,還有一部分政府相關的產業部門。在國內包括藍芯算力、中科創達(ThunderSoft)、Verisilicon 以及上海交大的孫亞男教授等紛紛給予支持。隨著架構的完善,Tenstorrent計劃于明年上半年對OCA架構 1.0 版本進行定稿。屆時,該公司設計的一批基于 OCA 架構的芯粒也將完成封裝,并完成一系列的測試。從而給業界提供經過實際產品驗證的架構方案。

AI時代到來,RISC-V成為必然選擇

在媒體群訪環節,CoreLab Technology董事長吳雄昂談到RISC-V趕上AI的大爆發,將獲得前所未有的發展機遇。過去幾年,計算機領域每次技術革命爆發初期都會催生大量新需求,且這些需求的計算方式差異巨大、迭代速度驚人。舉例來說,過去是跑操作系統的時代,而現在是AI驅動的token生成時代。傳統計算模式由Arm和英偉達主導,前者以通用處理器見長,后者則擅長數據密集型計算。Arm之所以能成功,正是因為其相對開放且成本可控的特性。

國內早期曾質疑Arm性能不足,認為“跑都跑不動”,但正是其開放性和低成本,讓許多企業敢于嘗試。一旦部分創新者驗證成功,就會帶動整個生態快速迭代。背后的經濟邏輯很清晰:敢于嘗試的新銳企業往往創新能力更強,在新一輪技術革命中更能搶占先機,最終脫穎而出。歷史規律反復印證這點——英特爾擊敗IBM,正是憑借X86架構的開放性打破了封閉生態;Arm后來居上,則因其比x86更開放的授權模式,讓安卓等軟件生態得以蓬勃發展,吸引眾多企業參與。同理,特斯拉初入電車領域時面臨“沒有充電樁”的質疑,但創新者敢于突破,最終改變了行業格局。

每一波技術創新浪潮中,由于新架構門檻較低,愿意試錯的新玩家能夠崛起。Jim Keller作為芯片設計領域頂尖技術團隊的領導者,他愿意嘗試新架構,正是看準RISC-V的巨大潛力。

AI正是這波技術創新浪潮的驅動力。有了這個驅動力,我們的硬件架構就有了用武之地。在硬件創新架構上,每一次有100倍成長的時候就會有新架構出來,這是經濟規律,未來三大計算架構RISC-V必有其一。

在吳雄昂看來,AI計算的token generation會不斷地演進,那么與之相適應的硬件和OS必然是全新的。其中硬件架構要體現性能和好用,但現在RISC-V性能尚可,但遠未到好用的程度。CoreLab搭建的平臺正是針對AI智能的平臺化,重點解決AI計算的需求問題。

他認為,未來大模型就是OS,機器人或類機器人就是硬件承載體。而RISC-V的機會在于能否在這些自主式設備中驅動算力的釋放。這就要求RISC-V的CPU具有區塊化功能,可以根據大模型OS進行轉換,芯片基于數據在算法基礎上設計,算法又跟數據強相關,也就是說核心數據決定了OS以及芯片的最終形態。

發布評論請先 登錄

RT-Thread 邀您參與“開放?連接”2026玄鐵 RISC-V 生態大會,攜手共鑄 RISC-V“芯”紀元

Powered by XuanTie,Qwen Inside:阿里通義大模型攜手玄鐵 RISC-V開啟“端側智能”新紀元

Tenstorrent與AutoCore宣布戰略合作,以AutoCore.OS賦能高性能RISC-V汽車計算

探索RISC-V在機器人領域的潛力

為什么RISC-V是嵌入式應用的最佳選擇

提高RISC-V在Drystone測試中得分的方法

大灣區RISC-V生態全景展示:RISC-V生態發展論壇、開發者Workshop和生態應用專區

時擎科技亮相2025 RISC-V中國峰會,深度解析高性能RISC-V SoC技術挑戰與創新

基于北海云計算試驗平臺的 RISC-V 虛擬化技術探索

知合計算:RISC-V架構創新,阿基米德系列劍指高性能計算

孟建熠:攀登 RISC-V 高性能高峰,打造標桿產品

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

智芯公司RISC-V高性能CPU芯片獲得權威認可

RISC-V架構下的編譯器自動向量化

DC-ROMA RISC-V AI PC 正式發布!

Jim Killer掌舵,超強RISC-V高性能計算來了!大模型即OS時代,RISC-V勢在必得

Jim Killer掌舵,超強RISC-V高性能計算來了!大模型即OS時代,RISC-V勢在必得

評論