Zen3架構為7nm、也為AM4接口畫上句號,明年或者2022年早些時候,AMD將拿出基于5nm工藝、AM5接口的Zen4架構銳龍處理器,保持每12~18個月更新架構的傳統(tǒng)。

日前與外媒交流時,AMD執(zhí)行副總裁Rick Bergman談到了關于Zen4的一些話題。

他表示,大家可以期待Zen4有著和Zen3一樣多的改進細節(jié),后者相較于Zen2,IPC增加了19%。也就是包括但不限于前端、預取、解碼、執(zhí)行、整數(shù)、浮點、載入、存儲、緩存等等,只要有助于提高IPC,AMD就會去優(yōu)化改進。

他強調(diào),Zen4將榨出更多的性能,并暗示核心數(shù)可能進一步增加(當前銳龍桌面CPU是最多16核)。

另外,Zen4也會充分發(fā)回5nm工藝在功耗和晶體管密度上的優(yōu)勢,確保每瓦輸出更多的運算性能。

當然,在Zen4登場前,AMD還有大量Zen3家族產(chǎn)品的拼圖需要補完,包括銳龍3 5000、銳龍筆記本處理器、EPYC 7xx3、銳龍線程撕裂者等。

責任編輯:PSY

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

amd

+關注

關注

25文章

5684瀏覽量

139947 -

核心

+關注

關注

0文章

47瀏覽量

15349 -

架構

+關注

關注

1文章

532瀏覽量

26589 -

5nm

+關注

關注

1文章

342瀏覽量

26646

發(fā)布評論請先 登錄

相關推薦

熱點推薦

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構

Timing Group 及SCA(獨立指令地址)架構,具備基于固件的訓練能力,能夠完美適配全球主流廠商的存儲顆粒。

3. 技術規(guī)格參數(shù)核心指標技術參數(shù)行業(yè)價值

最高速率4800Mbps (ONFI

發(fā)表于 01-29 17:32

AMD 推出銳龍 AI 嵌入式處理器產(chǎn)品組合,為汽車、工業(yè)和物理 AI 領域提供 AI 驅(qū)動的沉浸式體驗

新聞亮點 ·?全新 AMD 銳龍 AI 嵌入式 P100 和 X100 系列處理器融入了高性能“Zen 5”CPU 核心、AMD RDNA

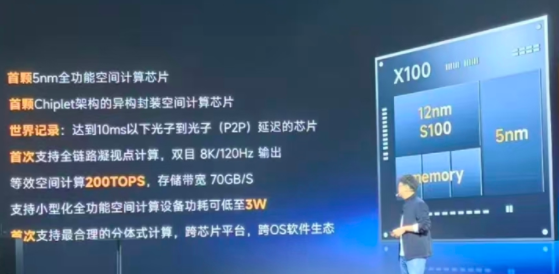

1600TOPS!美國新勢力車企自研5nm芯片,轉用激光雷達硬剛特斯拉

的2025 AI Day上,也首次公布了自研自動駕駛大模型,以及自研的5nm定制芯片,同時還明確了激光雷達是其下一代自動駕駛系統(tǒng)的核心傳感器之一。 ? 5nm芯片、高速互連、全新神經(jīng)網(wǎng)絡引擎 ? 作為一家美國新勢力車企,Rivi

那么龍芯CPU性能如何呢?

· ? 3A6000 ?:采用LA464架構,4核8線程設計,實測單核性能與英特爾10代酷睿i3-10100F持平,多核性能提升60%以上其每GHz性能表現(xiàn)甚至超越

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產(chǎn)業(yè)的前沿技術

MI300,是AMD首款數(shù)據(jù)中心HPC級的APU

③英特爾數(shù)據(jù)中心GPU Max系列

3)新粒技術的主要使用場景

4)IP即芯粒

IP即芯粒旨在以芯粒實現(xiàn)特殊功能IP的即插即用,解決5nm

發(fā)表于 09-15 14:50

江波龍企業(yè)級DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性認證

2025年7月23日,AMD(超威半導體)正式發(fā)布了基于全新Zen5架構的銳龍線程撕裂者Threadripper9000系列處理器,包括面向?qū)I(yè)工作站的撕裂者

芯動科技獨家推出28nm/22nm LPDDR5/4 IP

面對近來全球大廠陸續(xù)停產(chǎn)LPDDR4/4X以及DDR4內(nèi)存顆粒所帶來的巨大供應短缺,芯動科技憑借行業(yè)首屈一指的內(nèi)存接口開發(fā)能力,服務客戶痛點,率先在全球多個主流28nm和22

今日看點丨蔚來自研全球首顆車規(guī)5nm芯片!;沃爾沃中國區(qū)啟動裁員計劃

1. 蔚來自研全球首顆車規(guī)5nm 芯片!將對全行業(yè)開放 ? 據(jù)了解,李斌在直播中介紹了蔚來自研神璣NX9031芯片,他表示:“這是全球首顆車規(guī)5nm的智駕芯片,這個應該說是量產(chǎn)非常不容易的,要能支持

發(fā)表于 07-08 10:50

?2143次閱讀

基于AMD Versal器件實現(xiàn)PCIe5 DMA功能

Versal是AMD 7nm的SoC高端器件,不僅擁有比16nm性能更強的邏輯性能,并且其PS系統(tǒng)中的CPM PCIe也較上一代MPSoC PS硬核PCIe單元強大得多。本節(jié)將基于AMD

三星在4nm邏輯芯片上實現(xiàn)40%以上的測試良率

方式來改進電容器表現(xiàn),但穩(wěn)定性尚未達到預期水平,很可能會拖慢 1c nm 進度。

半導體業(yè)內(nèi)人士表示,“從三星電子的角度來看,剩下的任務是穩(wěn)定搭載在HBM上的DRAM以及封裝技術。”

發(fā)表于 04-18 10:52

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現(xiàn)流片成功

我們很高興能在此宣布,Cadence 基于 UCIe 標準封裝 IP 已在 Samsung Foundry 的 5nm 汽車工藝上實現(xiàn)首次流片成功。這一里程碑彰顯了我們持續(xù)提供高性能車規(guī)級 IP 解決方案?的承諾,可滿足新一代汽車電子和高性能計算應用的嚴格要求。

AMD自爆5nm Zen4:核心數(shù)可能增加 架構改進幅度不會遜于Zen3

AMD自爆5nm Zen4:核心數(shù)可能增加 架構改進幅度不會遜于Zen3

評論