01

超級(jí)計(jì)算機(jī)和FPGA

1、超算?

大數(shù)據(jù)、基因科學(xué)、金融工程、人工智能、新材料設(shè)計(jì)、制藥和醫(yī)療工程、氣象災(zāi)害預(yù)測(cè)等領(lǐng)域所涉及的計(jì)算處理,家用個(gè)人計(jì)算機(jī)級(jí)別的性能是遠(yuǎn)遠(yuǎn)不夠的。超級(jí)計(jì)算機(jī)(以下簡(jiǎn)稱(chēng)超算)就是為了解決這種超大規(guī)模的問(wèn)題而開(kāi)發(fā)的。超算并沒(méi)有一個(gè)明確的定義, 通常所說(shuō)的超算大致是性能在家用計(jì)算機(jī)的1000倍以上,或者理論性能在50 TFLOPST以上的系統(tǒng)。

FPGA作為可以提高超算能效比的通用器件受到了廣泛關(guān)注。從性能、靈活性和功耗效率方面,CPU、FPGA和ASIC里面FPGA走的是中間路線(xiàn)。FPGA的功耗效率是高于CPU的,靈活性高于ASIC;從功耗效率、性能保障性和算法適用性來(lái)看,F(xiàn)PGA應(yīng)該是碾壓GPU的。GPU適用的算法非常有限,拿到一個(gè)算法,能否達(dá)到最終的性能是有風(fēng)險(xiǎn)的;早期GPU的實(shí)現(xiàn)算法非常容易,但是自從Xilinx在高層次綜合HLS方面深度耕耘后,F(xiàn)PGA的編程容易度也降低了很多。其優(yōu)勢(shì)是不但可以作為運(yùn)算加速器,還可以作為連接器件讓超算中眾多的運(yùn)算處理器和運(yùn)算加速器更緊密地結(jié)合。此外,IoT技術(shù)正在推動(dòng)硬件基礎(chǔ)設(shè)施的升級(jí),今后運(yùn)算和數(shù)據(jù)的集中化和分散化進(jìn)程都會(huì)加速發(fā)展。在這個(gè)進(jìn)程當(dāng)中,為了運(yùn)用超算技術(shù),也要求數(shù)據(jù)中心具備更加嶄新和有效的方法和技術(shù)口。除了大規(guī)模計(jì)算以外,從強(qiáng)化升級(jí)社會(huì)IT基礎(chǔ)建設(shè)的角度上看,超算技術(shù)也越來(lái)越必要。因此,PLD/FPGA必將會(huì)在超算中得到更廣泛的運(yùn)用。

02

超算中的FPGA應(yīng)用案例

1、首先是筑波大學(xué)20世紀(jì)70年代開(kāi)始研發(fā)用于科學(xué)計(jì)算的并行計(jì)算機(jī)PACS/PAX,而HA-PACS是該系列的第8代。PACS/PAX系列自開(kāi)發(fā)之初就以實(shí)現(xiàn)了CPU和內(nèi)存間的高速互聯(lián)架構(gòu)而聞名。HA-PACS是PACS/PAX系列中首次采用GPU作為運(yùn)算加速器的超算。用GPU提高超算性能,還必須要實(shí)現(xiàn)能夠充分發(fā)揮GPU高運(yùn)算性能的并行系統(tǒng)架構(gòu)。然而,HA-PACS開(kāi)發(fā)時(shí)的GPU存在些問(wèn)題,導(dǎo)致難以實(shí)現(xiàn)高效的并行系統(tǒng)架構(gòu)。例如在多個(gè)GPU間共享數(shù)據(jù)時(shí),傳輸前后需要在宿主CPU的主存中進(jìn)行數(shù)據(jù)復(fù)制。還有將數(shù)據(jù)傳輸從PCle轉(zhuǎn)為其他通信方式時(shí),很難削減通信延遲。為了改善這些問(wèn)題,HA-PACS系統(tǒng)基于PEARL ( PCI Express Adaptive and Reliable Link)概念提出了TCA ( Tightly Coupled Accelerato-rs) 技術(shù),并開(kāi)始開(kāi)發(fā)實(shí)現(xiàn)TCA的PEACH2板卡。

那么由CPU+GPU+FPGA組成的異構(gòu)系統(tǒng)的性能又如何呢? HA-PACS/TCA是一個(gè)只有64個(gè)節(jié)點(diǎn)的小規(guī)模系統(tǒng),理論性能為364.3TFLOPS,實(shí)測(cè)性能為277.1 TFLOPS, 2013年11月位列TOP500的第134名。另外,由于該系統(tǒng)達(dá)到了3.52 GFLOPS/W的高能效比,在2013年11月和2014年6月的Green500榜中位列第3名。HA-PACS/TCA的基礎(chǔ)部分采用GPU和CPU組合來(lái)實(shí)現(xiàn)高性能、低功耗的運(yùn)算,再加上基于FPGA的PEACH2的使用,進(jìn)一步提高了跨學(xué)科合作應(yīng)用中的運(yùn)算性能。

PEACH2提供了可以讓多個(gè)GPU直接互聯(lián)通信的框架。具體來(lái)說(shuō),PEACH2擴(kuò)展了PCle通信連接,并實(shí)現(xiàn)了GPU間的直接通信,從而達(dá)到了提高數(shù)據(jù)傳輸效率的目的”。技術(shù)上,PEACH2實(shí)現(xiàn)了一種路由,可以將PCIe協(xié)議中Root Complex和多個(gè)End Point間的數(shù)據(jù)包在多個(gè)節(jié)點(diǎn)間傳輸。

原本的數(shù)據(jù)傳輸路徑GPUmem→CPUmem→(InfiniBand/MPI)→CPUmem→GPU mem, 縮短為了GPU mem→(PCIe/PEACH2)→GPU mem,即GPU間的直連傳輸。此外,通信協(xié)議的統(tǒng)一也實(shí)現(xiàn)了比InfiniBand更低的延遲。

下面一起看一下PEACH2的通信性能。PEACH2具備4個(gè)PCleGen2 x8 (8通路)端口。這里的端口數(shù)量上的限制并非源于PEACH2本身,而是因?yàn)樗捎玫腇PGA器件的物理限制,這點(diǎn)可以通過(guò)FPGA制造技術(shù)的提升而改善。PEACH2中GPU對(duì)GPU的DMA的Ping-pong延遲為2.0us ( 100萬(wàn)分之2秒),CPU對(duì)CPU的延遲為1.8 us,可以說(shuō)通信延遲十分小了。PEACH2能達(dá)到這種性能要?dú)w功于使用了PLD/FPGA,正因如此它才能將傳輸開(kāi)銷(xiāo)降低到2.0 us的程度。這個(gè)性能和MVAPICH2 v2.0-GDR ( 帶GDR : 4.5us ;不帶GDR : 19 us) 相比已經(jīng)足夠了。FPGA的采用實(shí)現(xiàn)了輕量化協(xié)議、多RootComplex互聯(lián)、Block-Stride通信硬件,從而獲得了高應(yīng)用性能。此外,在Ping-pong帶寬方面,PEACH2 的CPU對(duì)CPU的DMA傳輸性能約為3.5 GB/s,達(dá)到了理論性能的95%;GPU對(duì)GPU的DMA性能約為2.8GB/s。然而,當(dāng)負(fù)載大小超過(guò)512 KB時(shí)MVAPICH2 v2.0-GDR的性能更高,可以在實(shí)際應(yīng)用時(shí)根據(jù)需求進(jìn)行選擇。綜上,無(wú)論研究領(lǐng)域或商業(yè)系統(tǒng),今后都會(huì)繼續(xù)探索能夠發(fā)揮PLD/FPGA優(yōu)勢(shì)的高效方法,從而提高系統(tǒng)的整體性能。

2、其次是Cray Research,該公司的超級(jí)計(jì)算機(jī):XD1就有用上FPGA,XD1用的是Xilinx(賽靈思)公司的VIRTEX系列FPGA。XD1機(jī)內(nèi)有所謂的FPGA應(yīng)用程序加速模塊(FPGA ApplicaTIon AcceleraTIon Module),模塊等于是機(jī)內(nèi)的一個(gè)小型輔助運(yùn)算系統(tǒng),VIRTEX是模塊內(nèi)的主控芯片,等于是一個(gè)協(xié)同處理器(Co-Processor),只不過(guò)這個(gè)協(xié)同處理器與ASIC型式的協(xié)同處理器不同,F(xiàn)PGA具有可程序化的功效,因此VIRTEX是一顆可程序化的協(xié)同處理器。運(yùn)算模塊內(nèi)除了有FPGA的協(xié)同處理器外,處理器也必須搭配內(nèi)存才能行使運(yùn)算,所以FPGA會(huì)再連接4顆QDR II SRAM(極高速性的內(nèi)存),然后模塊一方面用HyperTransport與XD1的主處理器相連,另一方面也連往XD1的特有高速I(mǎi)/O界面:RapidArray。

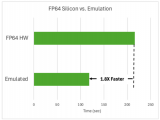

接著,由于高效運(yùn)算多是執(zhí)行大量重復(fù)性的運(yùn)算,例如氣象預(yù)測(cè)、風(fēng)洞測(cè)試等,所以可以將執(zhí)行的應(yīng)用程序轉(zhuǎn)化成FPGA內(nèi)的組態(tài)(ConfiguraTIon)程序,以硬件線(xiàn)路方式來(lái)執(zhí)行運(yùn)算,如此將比過(guò)往用純軟件方式執(zhí)行快上數(shù)倍至數(shù)十倍的效能,甚至在特定的應(yīng)用運(yùn)算上能達(dá)一百倍以上的效能。

更仔細(xì)而言,其實(shí)是將整個(gè)應(yīng)用程序中重復(fù)性最高、且最經(jīng)常用的函數(shù)庫(kù)進(jìn)行轉(zhuǎn)化,并以FPGA的硬件線(xiàn)路執(zhí)行,如此就能獲得最大的加速效果。

Cray如此,與Cray同為高效運(yùn)算市場(chǎng)的另一家業(yè)者:SGI(視算科技)也實(shí)行相同的作法,SGI提出所謂的RASC(Reconfigurable ApplicaTIon Specific Computing,可組態(tài)化應(yīng)用程序性運(yùn)算,)RASC也是以模塊方式讓原有的超級(jí)計(jì)算機(jī)能獲得加速效果。

SGI的作法與Cray有部分相同也有部分不同,Cray是將模塊設(shè)置在原有超級(jí)計(jì)算機(jī)的機(jī)內(nèi),而SGI則是運(yùn)用既有超級(jí)計(jì)算機(jī)機(jī)箱的上部來(lái)加搭加速模塊,不過(guò)就功效機(jī)制而言?xún)烧弋惽ぃ送鈨烧叨际褂肵ilinx的VIRTEX系列FPGA,但是內(nèi)存與I/O部分兩家也實(shí)行不同的設(shè)計(jì),Cray是使用QDR II SRAM,SGI則是可實(shí)行QDR SRAM,或者也可用DDR2 SDRAM,前者容量少(80MB)但速度快,后者容量大(20GB)而速度慢,提供兩種選擇的原因是可依據(jù)不同的應(yīng)用程序特性來(lái)選用。

另外,高效運(yùn)算業(yè)者通常有獨(dú)門(mén)的機(jī)內(nèi)通訊傳輸技術(shù),RapidArray即是Cray的獨(dú)家技術(shù),而SGI自身也有獨(dú)家的傳輸技術(shù),即NUMAlink 4(已是第四代技術(shù)),所以SGI的RASC不是使用RapidArray,而是使用NUMAlink 4。

其實(shí)Cray系統(tǒng)內(nèi)所用的FPGA模塊是與DRC Computer公司技術(shù)合作而成,因此DRC Computer自身也有提供相近方案,DRC的RPU(Reconfigurable Processor Units)同樣也是用FPGA來(lái)加速,一樣是用Xilinx VIRTEX FPGA,但與主系統(tǒng)間的連接接口改成AMD Opteron處理器的接座接口,如此一般使用AMD Opteron處理器的x86服務(wù)器也可以加裝RPU來(lái)提升高效運(yùn)算的效能。

原文標(biāo)題:FPGA應(yīng)用案例——超級(jí)計(jì)算機(jī)

文章出處:【微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636218 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7806瀏覽量

93189 -

人工智能

+關(guān)注

關(guān)注

1817文章

50094瀏覽量

265273

原文標(biāo)題:FPGA應(yīng)用案例——超級(jí)計(jì)算機(jī)

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

使用NVIDIA技術(shù)驅(qū)動(dòng)的超級(jí)計(jì)算機(jī)助力開(kāi)放科學(xué)研究

快450000000倍!超導(dǎo)量子計(jì)算機(jī)“天衍-287”建成

奧士康召開(kāi)DGX Spark AI超級(jí)計(jì)算機(jī)項(xiàng)目表彰大會(huì)

【作品合集】賽昉科技VisionFive 2單板計(jì)算機(jī)開(kāi)發(fā)板測(cè)評(píng)

工業(yè)計(jì)算機(jī)的重要性

NVIDIA助力AI超級(jí)計(jì)算機(jī)Isambard-AI投入使用

自動(dòng)化計(jì)算機(jī)經(jīng)過(guò)加固后有什么好處?

自動(dòng)化計(jì)算機(jī)的功能與用途

工業(yè)計(jì)算機(jī)與商用計(jì)算機(jī)的區(qū)別有哪些

NVIDIA驅(qū)動(dòng)的現(xiàn)代超級(jí)計(jì)算機(jī)如何突破速度極限并推動(dòng)科學(xué)發(fā)展

Blue Lion超級(jí)計(jì)算機(jī)將在NVIDIA Vera Rubin上運(yùn)行

NVIDIA技術(shù)賦能歐洲最快超級(jí)計(jì)算機(jī)JUPITER

NVIDIA助力全球最大量子研究超級(jí)計(jì)算機(jī)

計(jì)算機(jī)網(wǎng)絡(luò)入門(mén)指南

NVIDIA 宣布推出 DGX Spark 個(gè)人 AI 計(jì)算機(jī)

超級(jí)計(jì)算機(jī)和FPGA

超級(jí)計(jì)算機(jī)和FPGA

評(píng)論