DDR3的設計有著嚴格等長要求,歸結起來分為兩類(以64位的DDR3為例): 數據 (DQ,DQS,DQM):組內等長,誤差控制在20MIL以內,組間不需要考慮等長;地址、控制、時鐘信號:地址、控制信號以時鐘作參考,誤差控制在100MIL以內,Address、Control與CLK歸為一組,因為Address、Control是以CLK的下降沿觸發的由DDR控制器輸出,DDR顆粒由CLK的上升沿鎖存Address、Control總線上的狀態,所以需要嚴格控制CLK與Address/Command、Control之間的時序關系,確保DDR顆粒能夠獲得足夠的建立和保持時間。

關注等長的目的就是為了等時,繞等長時需要注意以下幾點:

1.確認芯片是否有Pin-delay,繞線時要確保Pin-delay開關已經打開;

2.同組信號走在同層,保證不會因換層影響實際的等時;同樣的換層結構,換層前后的等長要匹配,即時等長;不同層的傳播延時需要考慮,如走在表層與走在內層,其傳播速度是不一樣的,所以在走線的時候需要考慮,表層走線盡量短,讓其差別盡量小(這也是為什么Intel的很多GUIDE上面要求,表層的走線長度不超過250MIL等要求的原因);

3. Z軸的延時:在嚴格要求的情況下,需要把Z軸的延時開關也打開,做等長時需要考慮(ALLEGRO中層疊需要設置好,Z軸延時才是對的)。

4.蛇形繞線時單線按3W,差分按5W繞線(W為線寬)。且保證各BUS信號組內間距按3H, 不同組組間間距為5H (H為到主參考平面間距),DQS和CLK 距離其他信號間距做到5H以上。單線和差分繞線方式如下圖1所示:

圖1.單線和差分繞線方式示例

而另一個核心重點便是電源處理。DDR3中有三類電源,它們是VDD(1.5V)、VTT(0.75V)、VREF(0.75V,包括VREFCA和VREFDQ)。

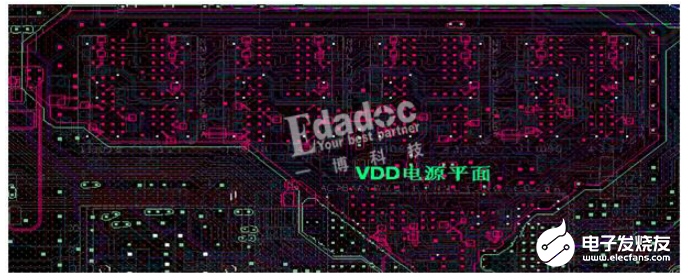

1. VDD(1.5V)電源是DDR3的核心電源,其引腳分布比較散,且電流相對會比較大,需要在電源平面分配一個區域給VDD(1.5V);VDD的容差要求是5%,詳細在JEDEC里有敘述。通過電源層的平面電容和專用的一定數量的去耦電容,可以做到電源完整性。VDD電源平面處理如下圖2所示:

圖2:VDD電源處理

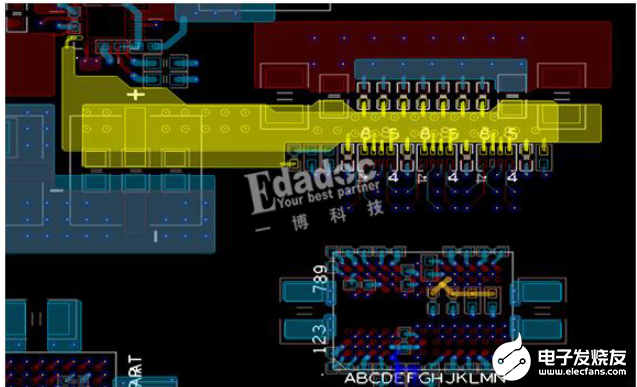

2. VTT電源,它不僅有嚴格的容差性,而且還有很大的瞬間電流;可以通過增加去耦電容來實現它的目標阻抗匹配;由于VTT是集中在終端的上拉電阻處,不是很分散,且對電流有一定的要求,在處理VTT電源時,一般是在元件面同層通過鋪銅直接連接,銅皮要有一定寬度(120MIl)。VTT電源處理如圖3所示:

圖3:VTT電源

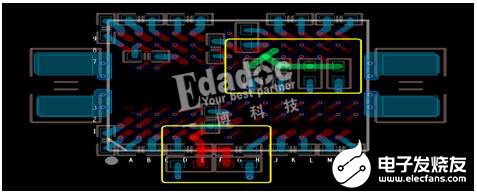

3.VREF電源 。 VREF要求更加嚴格的容差性,但是它承載的電流比較小。它不需要非常寬的走線,且通過一兩個去耦電容就可以達到目標阻抗的要求。DDR3的VERF電源已經分為VREFCA和VREFDQ兩部分,且每個DDR3顆粒都有單獨的VREFCA和VREFDQ,因其相對比較獨立,電流也不大,布線處理時也建議用與器件同層的銅皮或走線直接連接,無須在電源平面層為其分配電源。注意鋪銅或走線時,要先經過電容再接到芯片的電源引腳,不要從分壓電阻那里直接接到芯片的電源引腳。VREF電源處理如圖4所示:

圖4:VREF電源

濾波電容的FANOUT 小電容盡量靠近相應的電源引腳,電容的引線也要盡量短,并減少電源或地共用過孔;

圖5 : 小濾波電容的Fanout

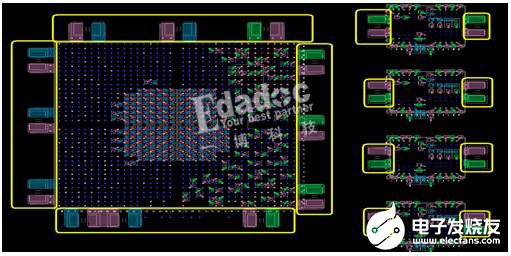

Bulk電容的FANOUT

電源的Bulk電容一般在設計中起到的是儲能濾波的作用,在做Fanout時要多打孔,建議2個孔以上,電容越大需要過孔越多,也可以用鋪銅的形式來做。電容的電源孔和地孔盡量靠近打,如圖6所示。

圖6:儲能電容的Fanout

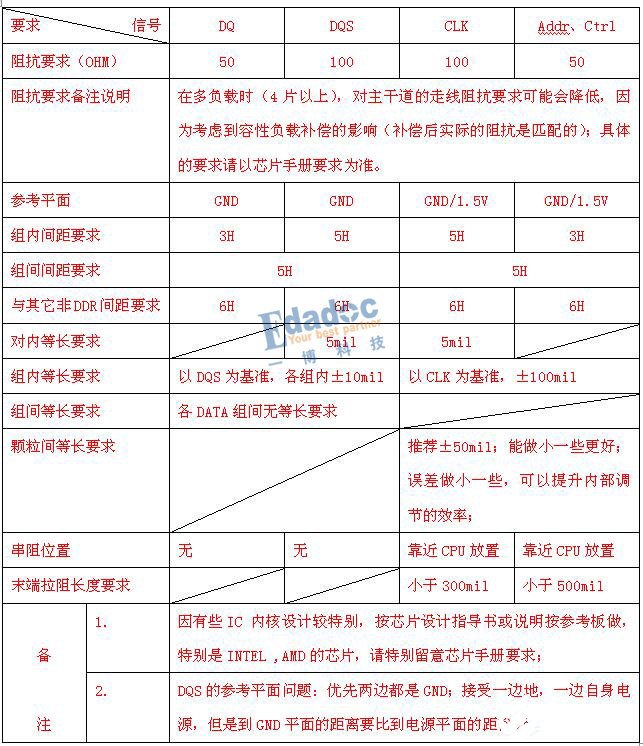

綜上所述,我們常規DDR3的走線設計總結如下表:

編輯:hfy

-

DDR3

+關注

關注

2文章

288瀏覽量

44144 -

濾波電容

+關注

關注

8文章

462瀏覽量

41574 -

控制信號

+關注

關注

0文章

200瀏覽量

12693 -

時鐘信號

+關注

關注

4文章

505瀏覽量

29972 -

Bulk

+關注

關注

0文章

8瀏覽量

8957

發布評論請先 登錄

TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

探索SN74SSQEB32882:DDR3內存的高效時鐘驅動解決方案

探索 SN74SSQEC32882:DDR3 注冊 DIMM 的理想時鐘驅動器

Texas Instruments TS3DDR3812:DDR3應用的理想12通道開關解決方案

到底DDR走線能不能參考電源層啊?

基于DDR200T開發板的e203進行DDR3擴展

DDR200T中的DDR3的使用配置

AD設計DDR3時等長設計技巧

AD設計DDR3時等長設計技巧

TPS51116 完整的DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據手冊

DDR3 SDRAM配置教程

淺談DDR3的走線設計

淺談DDR3的走線設計

評論