HDI設計在高速中的應用以及仿真方法

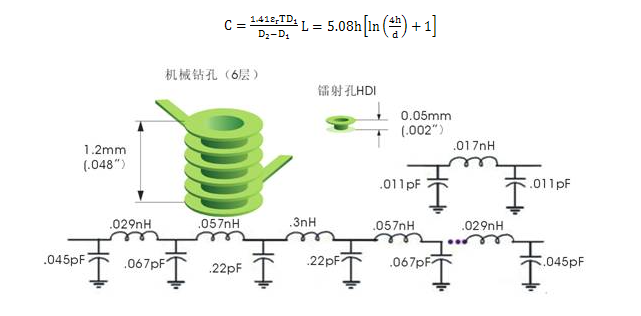

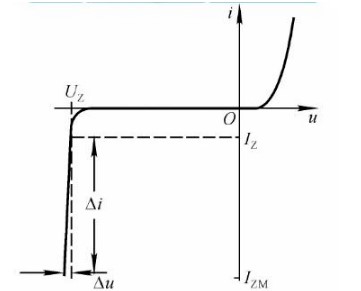

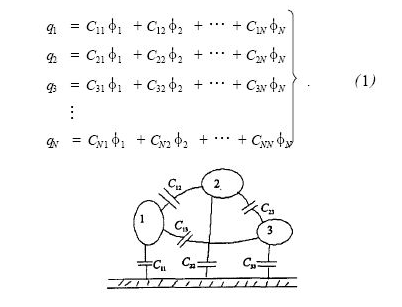

高速串行總線技術的發(fā)展,信號傳輸速率繼續(xù)提升,過孔寄生參數(shù)帶來的影響也越來越被重視。高速仿真工程師關注過孔優(yōu)化,通過各種手段來減小過孔寄生參數(shù)帶來的影響。HDI由于采用盤中孔的設計要求,可以減少表層器件的寄生參數(shù)。同時,微孔的電感和電容大約只是一個標準過孔的十分之一左右。圖九是能在很多資料上找到的過孔電感和電容,這是根據(jù)以下兩個計算公式得到的。

圖九 鐳射孔和機械孔的寄生參數(shù)但是圖七還是存在很多問題,寄生電容是對地的電容,機械孔不會6層都連接地平面,計算會遠遠比公式來得復雜;現(xiàn)在的過孔生產(chǎn)的時候,基本都采用無盤工藝,即去除非連接層的過孔焊盤,這可以有效減小過孔的寄生電容。這種情況下,只用![]() 來簡單考慮過孔特征阻抗的影響是遠遠不夠的。

來簡單考慮過孔特征阻抗的影響是遠遠不夠的。

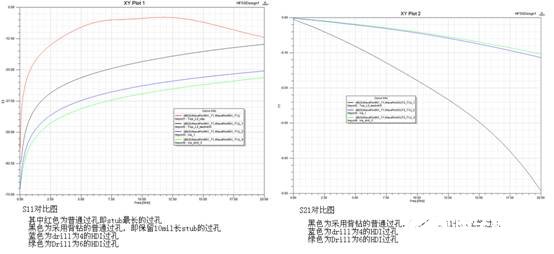

圖十是從S參數(shù)分析微孔和普通機械孔的插入損耗與回波損耗

圖十 S參數(shù)分析微孔和普通機械孔的插入損耗

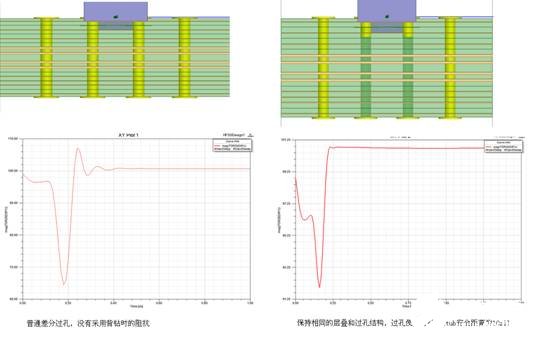

然后通過TDR的公式可以看到過孔的阻抗和回損曲線是密切相關的,S11在全頻段的仿真精度,也決定了通過軟件仿真看TDR曲線來研究阻抗的準確性,如圖十一所示:

TDRZ(t) = Zref*(1+IFFT(S11*input)) / (1-IFFT(S11*input))

能看到背鉆對過孔阻抗還是影響很大的

差分HDI微孔的阻抗,和100歐姆比較接近

圖十一 差分過孔的優(yōu)化策略以及TDR仿真結果

微孔的阻抗可以比較容易優(yōu)化到差分線的100歐姆阻抗值,這樣就減少了過孔引起的阻抗不連續(xù)帶來的高速問題。

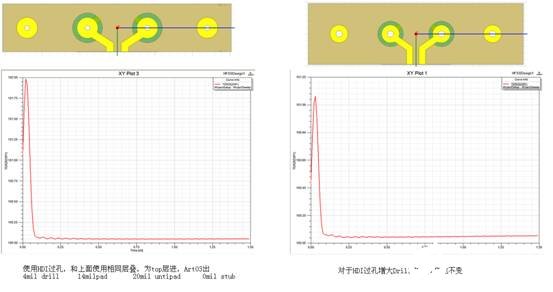

從以上分析可以看出,微孔的高速性能遠遠優(yōu)于普通機械孔,并且沒有Stub的問題,機械孔就算是采用背鉆工藝,也不可避免的要出現(xiàn)一定長度的Stub。而這個Stub,往往是影響高速電路性能的致命殺手。

有如果關心微孔的過電流能力,需要的時候可采用微孔填銅來提高載流能力。

結 論

Cadence的SPB16.X平臺提供了出色的小型化設計能力,在HDI多階過孔設計,任意階過孔設計,埋入式器件設計以及基于PDN的埋容仿真分析等領域都提供了出色的支持。全面基于HDI進行優(yōu)化更新的約束管理器,幫助工程師實現(xiàn)在小型化設計領域的約束驅動布局布線,提升設計效率和保證設計成功率。

基于Cadence強大的平臺和自身HDI設計上豐富的經(jīng)驗,同時結合自有板廠以及合作伙伴在國內領先的HDI加工能力,一博科技可以提供全方位的小型化設計、仿真、生產(chǎn)、貼片、組裝等一站式服務,全面實現(xiàn)客戶在小型化領域的各類需求,更多資訊請參見:www.edadoc.com。

一博科技和Cadence合作,強強聯(lián)手,推出《Cadence印刷電路板設計 – Allegro PCB Editor設計指南》一書,書中也專題介紹了小型化設計的技術,歡迎大家參考交流。

參考文獻

[1] 《Cadence印刷電路板設計 – Allegro PCB Editor設計指南》

[2] 《High-Speed Digital Design – A Handbook of Black Magic》

致 謝

本文引用了《Cadence印刷電路板設計 – Allegro PCB Editor設計指南》王輝負責的小型化章節(jié),同時仿真部分和Cadence 鐘章明做了很多交流,在此表示感謝!

編輯:hfy

-

HDI

+關注

關注

7文章

224瀏覽量

22717 -

信號傳輸

+關注

關注

4文章

494瀏覽量

21092

發(fā)布評論請先 登錄

什么是HDI?PCB設計基礎與HDI PCB制造工藝

HDI設計在高速中的應用以及仿真方法

HDI設計在高速中的應用以及仿真方法

評論