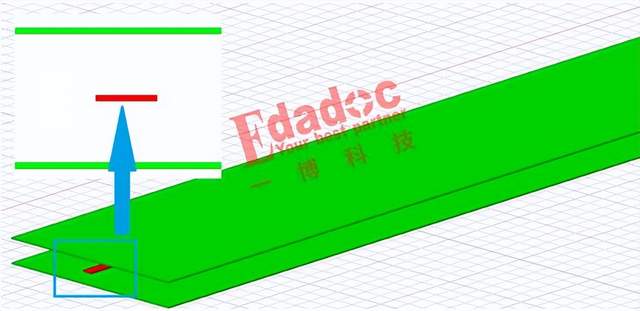

PCB 上的任何一條走線在通過高頻信號的情況下都會對該信號造成時延時,蛇形走線的主要作用是補償“同一組相關"信號線中延時較小的部分,這些部分通常是沒有或比其它信號少通過另外的邏輯處理;最典型的就是時鐘線,通常它不需經過任何其它邏輯處理,因而其延時會小于其它相關信號。

高速數字 PCB 板的等線長是為了使各信號的延遲差保持在一個范圍內,保證系統在同一周期內讀取的數據的有效性(延遲差超過一個時鐘周期時會錯讀下一周期的數據),一般要求延遲差不超過 1/4 時鐘周期,單位長度的線延遲差也是固定的,延遲跟線寬,線長,銅厚,板層結構有關,但線過長會增大分布電容和分布電感,使信號質量,所以時鐘 IC 引腳一般都接 RC 端接,但蛇形走線并非起電感的作用,相反的,電感會使信號中的上升元中的高次諧波相移,造成信號質量惡化,所以要求蛇形線間距最少是線寬的兩倍,信號的上升時間越小就越易受分布電容和分布電感的影響 .

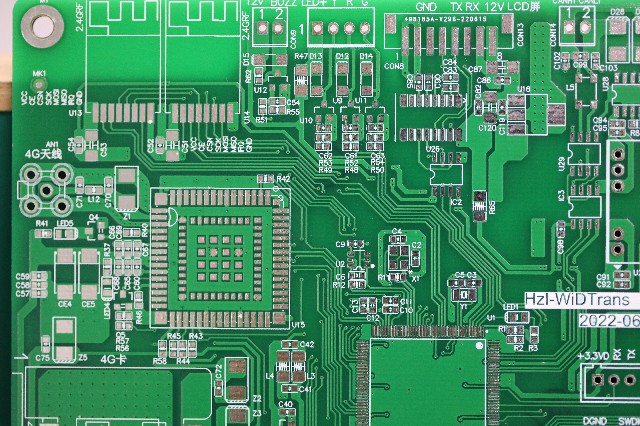

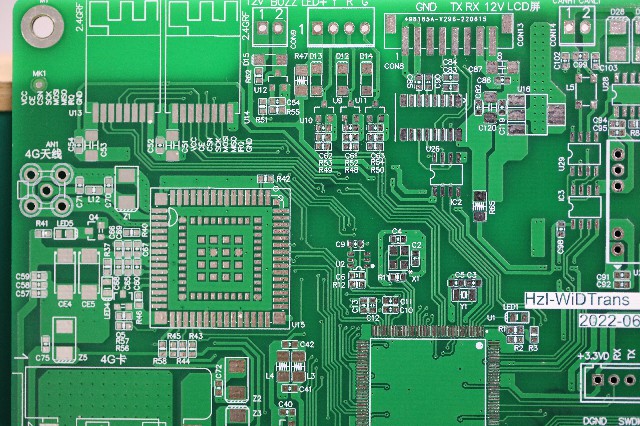

因為應用場合不同具不同的作用,如果蛇形走線在電腦板中出現,其主要起到一個濾波電感的作用,提高電路的抗干擾能力,電腦主機板中的蛇形走線,

主要用在一些時鐘信號中,如 CIClk,AGPClk,它的作用有兩點:

1、阻抗匹配

2、濾波電感。

對一些重要信號,如 INTEL HUB 架構中的 HUBLink,一共 13 根,跑 233MHz,要求必須嚴格等長,以消除時滯造成的隱患,繞線是唯一的解決辦法。一般來講,蛇形走線的線距>=2 倍的線寬。PCI 板上的蛇行線就是為了適應 PCI 33MHzClock 的線長要求。若在一般普通 PCB 板中,是一個分布參數的 LC 濾波器,還可作為收音機天線的電感線圈,短而窄的蛇形走線可做保險絲等等 .

審核編輯 黃昊宇

-

pcb

+關注

關注

4404文章

23878瀏覽量

424294

發布評論請先 登錄

MCU 的 3.3V 電源線走線有沒有問題?比如濾波電容的位置、走線長度這些是不是規范?

PCB板雙面布局的DDR表底走線居然不一樣

到底DDR走線能不能參考電源層啊?

PCB抄板打樣避坑指南:PCB抄板打樣全流程解析

PCB板蛇形走線有哪些好處?

PCB板蛇形走線有哪些好處?

評論