1、前言

磁珠的全稱為鐵氧體磁珠濾波器(另有一種是非晶合金磁性材料制作的磁珠),是一種抗干擾元件,濾除高頻噪聲效果顯著。

磁珠的主要原料為鐵氧體。鐵氧體是一種立方晶格結構的亞鐵磁性材料,鐵氧體材料為鐵鎂合金或鐵鎳合金,它的制造工藝和機械性能與陶瓷相似,顏色為灰黑色。

二、磁珠基礎知識

磁珠(Ferritebead)有很高的電阻率和磁導率,其等效電路是一個DCR電阻串聯一個電感并聯一個電容和一個電阻。DCR是一個恒定值,但后面三個元件都是頻率的函數,也就是說它們的感抗,容抗和阻抗會隨著頻率的變化而變化,當然它們阻值,感值和容值都非常小。磁珠比普通的電感有更好的高頻濾波特性,在高頻時呈現阻性,所以能在相當寬的頻率范圍內保持較高的阻抗,從而提高調頻濾波效果。磁珠的電路符號就是電感,但是型號上可以看出使用的是磁珠。在電路功能上,磁珠和電感是原理相同的,只是頻率特性不同而已。

從等效電路中可以看到,當頻率低于fL(LC諧振頻率)時,磁珠呈現電感特性;當頻率等于fL時,磁珠是一個純電阻,此時磁珠的阻抗(impedance)最大;當頻率高于諧振頻率點fL時,磁珠則呈現電容特性。EMI選用磁珠的原則就是磁珠的阻抗在EMI噪聲頻率處最大。比如如果EMI噪聲的最大值在200MHz,那你選擇的時候就要看磁珠的特性曲線,其阻抗的最大值應該在200MHz左右。

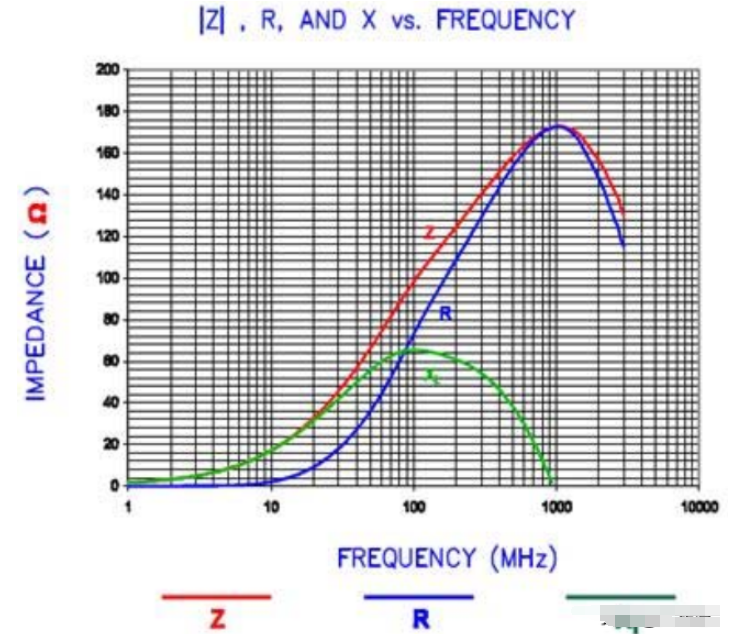

下圖是一個磁珠的實際的特性曲線圖。大家可以看到這個磁珠的峰值點出現在1GHz左右,在峰點時,阻抗(Z)曲線的值與電阻(R)的相等。也就是說這個磁珠在1GHz時,是個純電阻,而且阻抗值最大。

Z:impedanceR:R(f)X1:L\C前面簡單介紹了EMI磁珠的基本特性曲線。從磁珠的阻抗曲線來看,其實它的特性就是可以用來做高頻信號濾波器。需要注意的是,通常大家看到的廠家提供的磁珠阻抗曲線,都是在無偏置電流情況下測試得到的曲線。但大部分磁珠通常被放在電源線線上用來濾除電源的EMI噪聲。在有偏置電流的情況下,磁珠的特性會發生一些變化。

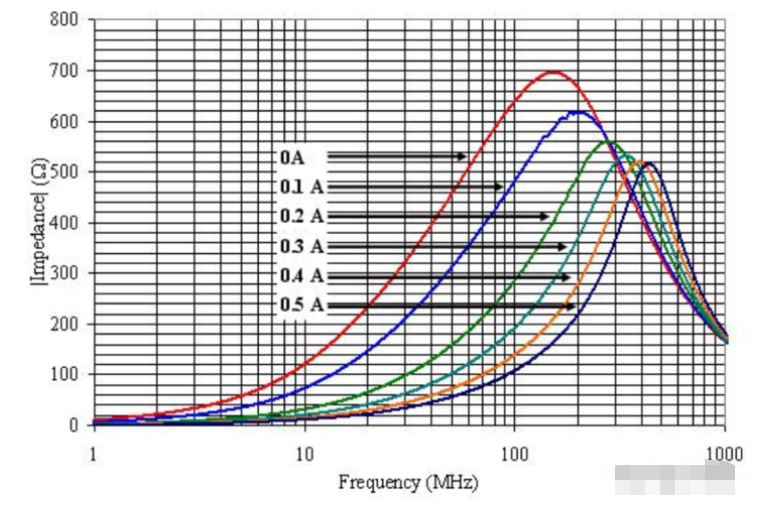

下面是某個0805尺寸500mA的磁珠在不同的偏置電流下的阻抗曲線。大家可以看到,隨著電流的增加,磁珠的峰值阻抗會變小,同時阻抗峰值點的頻率也會變高。

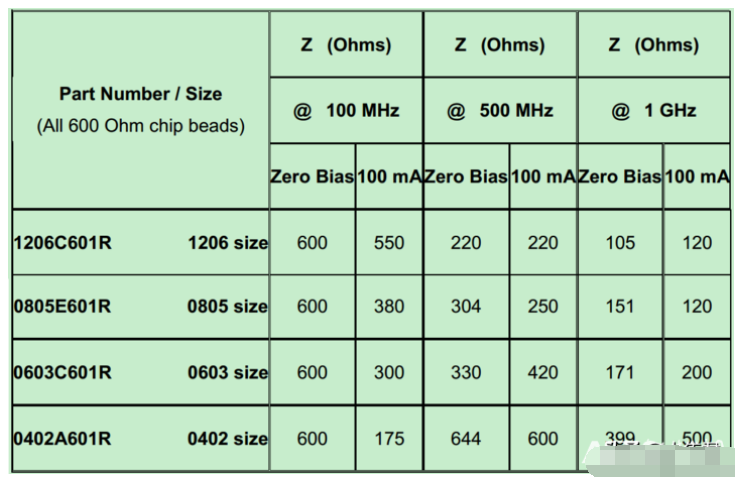

在進一步闡述磁珠的特性之前,讓我們先來看一下磁珠的主要特性指標的定義:Z(阻抗,impedanceohm):磁珠等下電路中所有元件的阻抗之和,它是頻率的函數。通常大家都用磁珠在100MHz時的阻抗值作為磁珠阻抗值。DCR(ohm):磁珠導體的的直流電阻。額定電流:當磁珠安裝于印刷線路板并加入恒定電流,自身溫升由室溫上升40C時的電流值。那么EMI磁珠的磁珠有成千上萬種,阻抗曲線也各不相同,我們應該如何根據我們的實際應用選擇合適的磁珠呢?讓我們首先來看一下阻抗值同為600ohm@100MHz,但尺寸大小不同的磁珠在不同偏置電流電流和工作頻率下的特性。

上面是四個不同大小的磁珠分別工作在0A,100mA偏置電流及在100MHz,500MHz和1GHz工作頻率下的阻抗值。

從上表的測試數據中可以看出,1206尺寸的磁珠在低頻100MHz工作時,其阻抗值僅從0A下的600ohm減小到100mA偏置電流下的550ohm,而0402尺寸的磁珠阻抗值卻從0A下的600ohm大幅減小為175ohm。

由此看來,在低頻大偏置電流應用的情況下,應該選擇大尺寸的磁珠,其阻抗特性會更好一些。讓我們來看一下磁珠在高頻工作時的情形。1206尺寸的磁珠其1GHz下的阻抗從100MHz下的600ohm大幅減小為105ohm,而0402尺寸的磁珠其1GHz下的阻抗則只由100MHz下的600ohm小幅減小為399ohm。

這也就是說,在低頻大偏置電流的情況下,我們應該選擇較大尺寸的磁珠,而在高頻應用中,我們應該盡量選擇小尺寸的磁珠。

三、應用于信號線上的磁珠

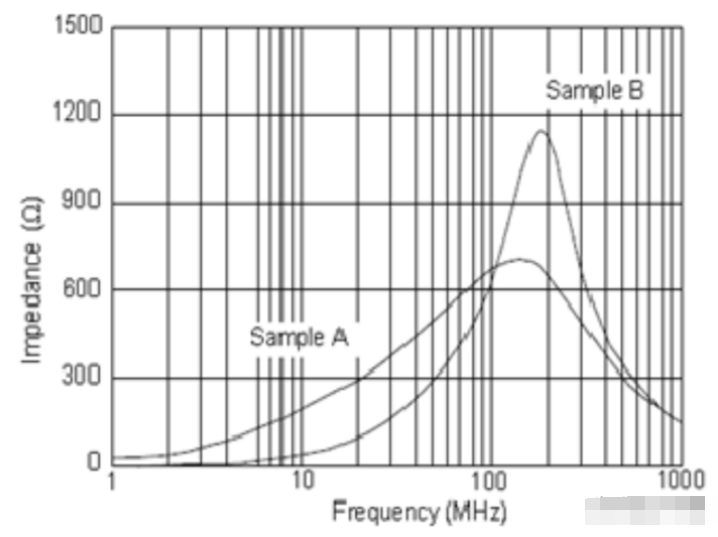

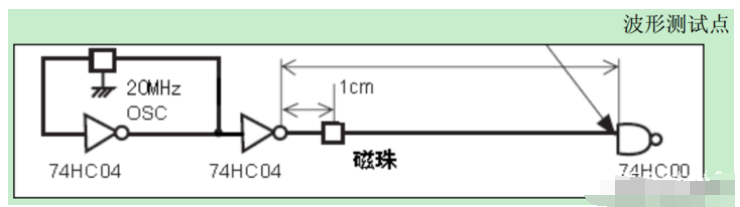

讓我們再來看一下下面兩個不同曲線特征的磁珠A和磁珠B應用于信號線時的情況。

磁珠A和磁珠B的阻抗峰值都在100MHz和200MHz之間,但磁珠A阻抗頻率曲線比較平坦,磁珠B則比較陡峭。我們將兩個磁珠分別放在如下的20MHz的信號線上,看看對信號輸出會產生什么樣的影響。

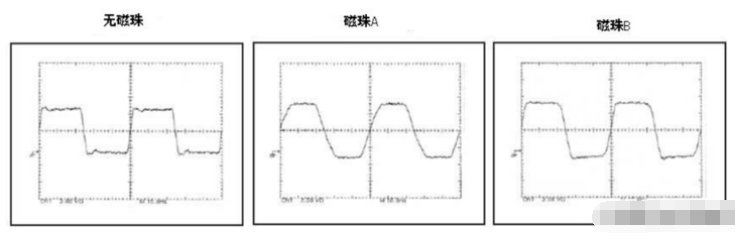

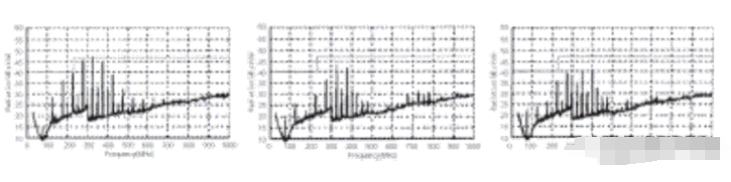

下面是用示波器分別量測磁珠輸出端的波形圖

從輸出波形來看,磁珠B的輸出波形失真要明顯小于磁珠A。原因是磁珠B的阻抗頻率波形比較陡峭,其阻抗在200MHz時較高,只對200MHz附近的信號的衰減較大,但對頻譜很寬的方波波形影響較小。而磁珠A的阻抗頻率特性比較平坦,其對信號的衰減頻譜也比較寬,因此對方波的波形影響也較大。

下面是上述三種情況對應的EMI測試結果。結果是磁珠A和磁珠B都會對EMI噪聲產生很大的衰減。磁珠A在整個EMI頻譜范圍內的衰減要稍好于磁珠B。

因此,在具體選用磁珠時,阻抗頻率特性平坦型的磁珠A比較適合應用于電源線,而頻率特性比較陡峭的磁珠B則較適合應用于信號線。磁珠B在應用于信號線時,可以在盡量保持信號完整性的情況下,盡可能只對EMI頻率附近的噪聲產生最大的衰減。

四、磁珠與電容回路

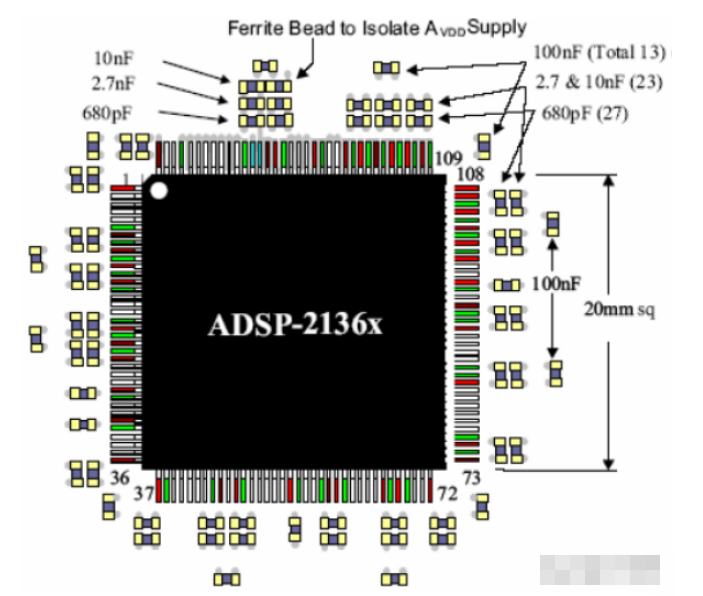

在一些器件的數據手冊或者應用文檔中,一般會建議對一些要求較高的電源管腳(比如VCCA,VCCPLL之類的)做隔離處理,并推薦使用磁珠進行隔離。

一般建議將電容放在更加靠近器件電源管腳的地方(相對于磁珠的位置),如下圖所示。至于電容的容值,和該電源管腳的功率(電壓&電流),電容距離管腳的位置,電容的封裝大小等因素有關系。

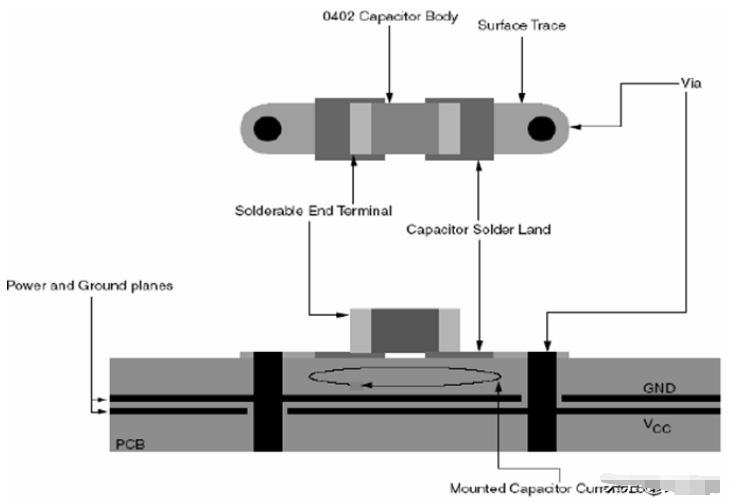

對于電容的Layout也有一些講究,安裝電容時,要從焊盤拉出一下段引線通過過孔和電源平面連接,接地段也一樣。則電容的電流回路是:電源平面→過孔→引出線→焊盤→電容→焊盤→引出線→過孔→低平面。如下圖所示:

放置過孔的基本原則就是讓這一環路面積最小,減小寄生電感。下圖顯示幾種安裝方法:

第一種方法從焊盤引出很長的線然后連接到過孔,這會引入很大的寄生電感,一定要避免這樣做。

第二種方法在焊盤二端打過孔,比第一種方法路面積小的多,寄生電感也較小,可以接受。

第三種方法在焊盤側面打孔,進一步減小了環路面積,寄生電感比第一個更小,是比較好的方法。

第四種方法焊盤二側面打孔,和第三種方法相比,電容的每端都是通過并聯的過孔接入電源和地平面,比第三種的寄生電感還小,只要空間允許,盡量使用。

最后一種方法在焊盤上直接打孔,寄生電感最小,但是焊接可能會出現問題。

五、“濫用”磁珠的危害

典型的8層以上單板,或者6層板采用3個電源地平面,電源地相對緊耦合的設計,這時候板上的濾波電容呈現“全局特性”,也就是說電容的位置不是很“重要”,電容在全局起作用。雙面板四層板,以及6層板電源地距離比較遠,相對松耦合的時候,板上的濾波電容傾向于“局部特性”,電容的位置比較重要,最好能靠近芯片管腳放置。

當電源供電網絡不使用電源地平面來設計的時候,電容更傾向于“局部特性”。如PLL電源的電容,如DDR3設計中Vref電源的電容,都希望嚴格把相應的電容靠近芯片的管腳,甚至最好能做到設計時指定電源必須從濾波電容進入芯片管腳。

同樣的,對于常規數字電源,如3.3V,2.5V等IO電源,如果我們對每一個芯片都使用磁珠隔離之后單獨供電,那么電容就失去了“全局”作用。最直接的一個負面作用就是導致設計需要增加更多的濾波電容。或者某個芯片的電容數量與種類不夠,導致電源軌道噪聲變大。

就算是電容的數量不是問題,電源噪聲可控,“濫用”磁珠還會造成其他設計問題。電源種類多是設計的現狀,“濫用”磁珠會“雪上加霜”的讓電源種類更多。加大電源地平面設計的難度。而增加的磁珠,其實并沒有給電源噪聲帶來好處。

六、總結

常規的數字電源,在采用多層板設計,電源地平面緊耦合的情況下,不建議“濫用”磁珠,保持電容的“全局”特性起作用。

需要使用磁珠的場合大致分為兩種

1、“特別”保護自己,如PLL電源,FPGA中的SerDes模擬電源等

2、“關愛”他人,自身的干擾性比較強,避免EMI問題,如強驅動的時鐘芯片等

責任編輯人:CC

-

電源

+關注

關注

185文章

18841瀏覽量

263535 -

磁珠

+關注

關注

6文章

278瀏覽量

45368

發布評論請先 登錄

Cadence工具如何解決芯粒設計中的信號完整性挑戰

貼片電感磁珠的選型方法有哪些?

電源完整性分析——謹慎使用磁珠

是德DSOX1204A示波器在電源完整性測試中的關鍵優勢

了解信號完整性的基本原理

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

電源完整性基礎知識

各種常用電路模塊設計原則:電源完整性

受控阻抗布線技術確保信號完整性

信號完整性測試基礎知識

使用羅德與施瓦茨RTE1104示波器進行電源完整性測試

磁珠是如何影響電源的完整性

磁珠是如何影響電源的完整性

評論