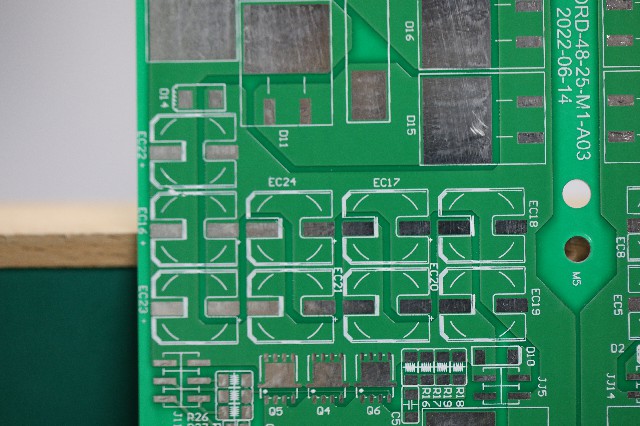

由于開關電源的開關特性,容易使得開關電源產生極大的電磁兼容方面的干擾,作為一個電源工程師、電磁兼容工程師,或則一個 PCB layout 工程師必須了解電磁兼容問題的原因已經解決措施,特別是 layout 工程師,需要了解如何避免臟點的擴大,本文主要介紹了電源 PCB 設計的要點。

layout與PCB的29個基本關系

1、幾個基本原理:任何導線都是有阻抗的;電流總是自動選擇阻抗最小的路徑;輻射強度和電流、頻率、回路面積有關;共模干擾和大 dv/dt 信號對地互容有關;降低 EMI 和增強抗干擾能力的原理是相似的。

2、布局要按電源、模擬、高速數字及各功能塊進行分區。

3、盡量減小大 di/dt 回路面積,減小大 dv/dt 信號線長度(或面積,寬度也不宜太寬,走線面積增大使分布電容增大,一般的做法是:走線的寬度盡量大,但要去掉多余的部分),并盡量走直線,降低其隱含包圍區域,以減小輻射。

4、感性串擾主要由大 di/dt 環路(環形天線),感應強度和互感成正比,所以減小和這些信號的互感(主要途徑是減小環路面積、增大距離)比較關鍵;容性串擾主要由大 dv/dt 信號產生,感應強度和互容成正比,所有減小和這些信號的互容(主要途徑是減小耦合有效面積、增大距離,互容隨距離的增大降低較快)比較關鍵。

5、盡量利用環路對消的原則來布線,進一步降低大 di/dt 回路的面積,

6、降低環路面積不僅降低了輻射,同時還降低了環路電感,使電路性能更佳。

7、降低環路面積要求我們精確設計各走線的回流路徑。

8、當多個 PCB 通過接插件進行連接時,也需要考慮使環路面積達到最小,尤其是大 di/dt 信號、高頻信號或敏感信號。最好一個信號線對應一條地線,兩條線盡量靠近,必要時可以用雙絞線進行連接(雙絞線每一圈的長度對應于噪聲半波長的整數倍)。如果大家打開電腦機箱,就可以看到主板到前面板 USB 接口就是用雙絞線進行連接,可見雙絞線連接對于抗干擾和降低輻射的重要性。

9、對于數據排線,盡量在排線中多安排一些地線,并使這些地線均勻分布在排線中,這樣可以有效降低環路面積。

10、有些板間連接線雖然是低頻信號,但由于這些低頻信號中含有大量的高頻噪聲(通過傳導和輻射),如果沒有處理好,也很容易將這些噪聲輻射出去。

11、布線時首先考慮大電流走線和容易產生輻射的走線。

12、開關電源通常有 4 個電流環:輸入、輸出、開關、續流。其中輸入、輸出兩個電流環幾乎為直流,幾乎不產生 emi ,但容易受干擾;開關、續流兩個電流環有較大的 di/dt ,需要注意。

13、mos ( igbt )管的柵極驅動電路通常也含有較大的 di/dt 。

14、在大電流、高頻高壓回路內部不要放置小信號回路,如控制、模擬電路,以避免受到干擾。

15、減小易受干擾(敏感)信號回路面積和走線長度,以減小干擾。

16、小信號走線遠離大 dv/dt 信號線(比如開關管的 C 極或 D 極,緩沖 (snubber) 和鉗位網絡),以降低耦合,可在中間鋪地(或電源,總之是常電位信號)進一步降低耦合,鋪地和地平面要良好接觸。小信號走線同時也要盡量遠離大 di/dt 的信號線,防止感性串擾。小信號走線最好不要走到大 dv/dt 信號的下方。小信號走線背面如果能夠鋪地(同性質地),也能降低耦合到的噪聲信號。

17、比較好的做法是,在這些大 dv/dt 、 di/dt 信號走線(包括開關器件的 C/D 極、開關管散熱器)的周圍和背面鋪地,將上下兩層鋪地用過孔連接,并將此地用低阻抗走線接到公共接地點(通常為開關管的 E/S 極,或取樣電阻)。這樣可以減小輻射 EMI 。要注意,小信號地一定不能接到此屏蔽地上,否則會引入較大干擾。大 dv/dt 走線通常會通過互容將干擾耦合到散熱器及附近的地,最好將開關管散熱器接到屏蔽地上,采用表貼開關器件也會降低互容,從而降低耦合。

18、易產生干擾的走線最好不要使用過孔,它會通過過孔干擾過孔所穿過的所有層。

19、屏蔽可以降低輻射 EMI ,但由于增大了對地的電容,會使傳導 EMI (共模,或非本征差模)有所增大,不過只要屏蔽層接地得當,不會增大很多。實際設計中可權衡考慮。

20、要防止共阻抗干擾,采用一點接地,電源從一點引出。

21、開關電源通常有三種地:輸入電源大電流地、輸出電源大電流地、小信號控制地。

22、接地時首先應先判斷地的性質,再進行連接。采樣及誤差放大的地通常應當接到輸出電容的負極,采樣信號通常應從輸出電容的正極取出,小信號控制地和驅動地通常要分別接到開關管的 E/S 極或取樣電阻上,防止共阻抗干擾。通常 IC 的控制地和驅動地不單獨引出,此時取樣電阻到上述地的引線阻抗必須盡量小,最大程度減小共阻抗干擾,提高電流采樣的精度。

23輸出電壓采樣網絡最好靠近誤差放大器,而不是靠近輸出端,這是由于低阻抗信號比高阻抗信號更不容易受到干擾,采樣走線對要盡量相互靠近以減小拾取到的噪聲。

24、布局注意電感要遠離,并相互垂直,以減小互感,尤其是儲能電感和濾波電感。

25、布局注意高頻電容和低頻電容并聯使用時,高頻電容靠近使用者。

26、低頻干擾一般為差模( 1M 以下),高頻干擾一般為共模,通常通過輻射耦合。

27、如果高頻信號被耦合到輸入引線,很容易形成 EMI (共模),可在輸入引線接近電源處套一個磁環,如果 EMI 降低就表明存在此問題。解決此問題的方法是,降低耦合或降低電路的 EMI 。如果高頻噪聲沒有被過濾干凈而傳導到輸入引線,也會形成 EMI (差模),此時套磁環不能解決問題,在輸入引線接近電源處串兩個高頻電感(對稱),如果 EMI 降低就表明存在此問題。解決此問題的方法是改善濾波,或采用緩沖、鉗位等手段減小高頻噪聲的產生。

28、差模和共模電流的測量:

29、EMI 濾波器要盡量靠近進線,進線的走線要盡量短,盡量減小 EMI 濾波器前后級的耦合。進線最好用機殼地進行屏蔽(方法如上所述)。輸出 EMI 濾波器也要作類似處理。盡量拉開進線和高 dv/dt 信號走線的距離,在布局上要加以考慮。

審核編輯 黃昊宇

-

pcb

+關注

關注

4415文章

23933瀏覽量

425722 -

Layout

+關注

關注

15文章

424瀏覽量

75374

發布評論請先 登錄

PCB設計與工藝規范 PCB Layout工程師一次講透

PCB Layout設計內容詳解:從布局到布線的核心工作要點

班通科技:PCB線寬線距對阻抗的影響有哪些?

SAW 濾波器 PCB Layout 與 ESD 小技巧總結

PCB設計與打樣的6大核心區別,看完少走3個月彎路!

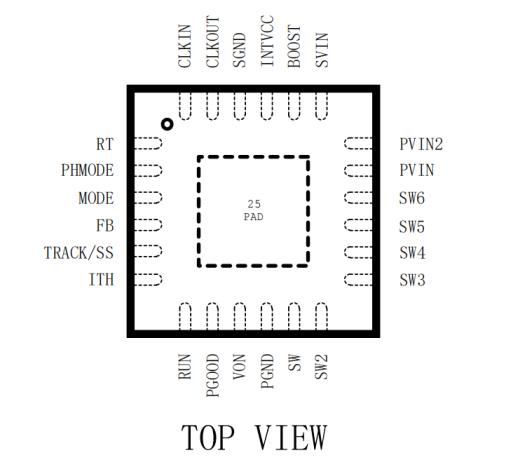

ASP3605S型BUCK DCDC芯片的pcb layout注意事項

如何判斷PCB板的厚度?

經驗分享:深槽設計與板材力學性能的關系

手機板 layout 走線跨分割問題

PCB設計與工藝規范

為什么PCB Layout設計不可忽視?影響電子設備的關鍵因素

PCB Layout 約束管理,助力優化設計

layout和PCB的29個基本關系

layout和PCB的29個基本關系

評論