1、介紹

本用戶指南介紹了Digilent DVI-to-RGB視頻解碼器知識產權。 該IP直接連接到Sink器件的DVI 1.0規范中定義的原始轉換最小化差分信號(TMDS)時鐘和數據通道輸入。 它解碼視頻流并輸出24位RGB視頻數據以及從TMDS鏈路恢復的像素時鐘和同步信號。

2、特性

?直接連接到頂級數字視頻接口(DVI)端口

?24位視頻(帶同步信號的時鐘并行視頻數據)輸出

?帶有內置EDID ROM的顯示數據通道接口

?支持的分辨率:1920x1080 / 60Hz至800x600 / 60Hz(148.5 MHz - 40 MHz)

?EDID中可選的首選分辨率

?使用Xilinx接口:IIC,vid_io

?使用Digilent接口:TMDS

3、性能

IP將TMDS_Clk限制在165 MHz,這是DVI 1.0規范中列出的最大頻率。 但是,根據實際的FPGA部件或速度等級,最大支持頻率可能較低。 如果頂層設計在IP實例內的脈沖寬度檢查上沒有約束,TMDS_Clk需要(重新)限制到項目部分支持的最大頻率。 檢查FMAX_BUFIO部分的數據表,這是定時失敗的最可能原因。 TMDS_Clk應該限制在FMAX_BUFIO / 5。 因此,這是FPGA系列和速度等級支持的最大像素時鐘頻率。

4、 概覽

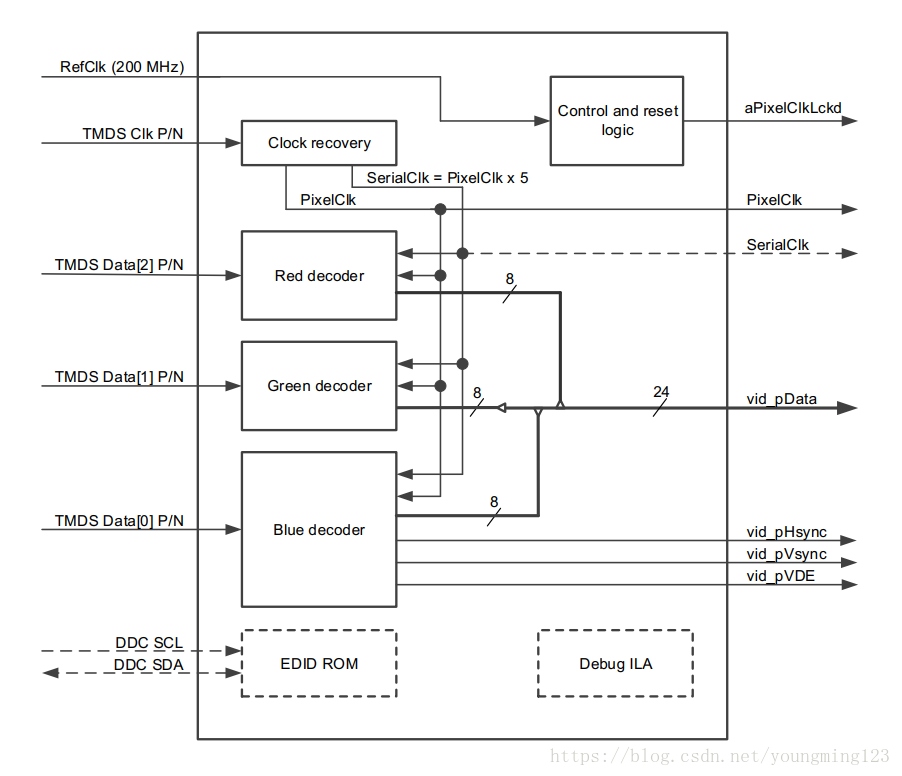

IP由多個模塊構成:一個時鐘恢復模塊,每個數據通道一個數據解碼器模塊(參見[3],[4]),一個可選的DDC(顯示數據通道)模塊和一個控制/復位模塊。

4.1、時鐘復位

時鐘通道載有一個字符速率頻率參考。 一個字符(或10比特)在每個數據信道的每個周期傳輸。 專用解串器原語(需要快速串行時鐘)將用于對串行數據流進行采樣。 時鐘恢復模塊從時鐘通道產生一個串行時鐘和一個像素時鐘。 兩個時鐘之間的頻率比是5:1。

由于時鐘頻率相對較高并且恢復的時鐘具有嚴格的相位要求,因此在該塊內部實例化專用時鐘基元。 這些可以在圖2中看到。MMCM原始設備包含一個壓控振蕩器(VCO),其具有FPGA數據手冊中指定的工作范圍。 由于沒有一組MMCM參數可將整個DVI像素時鐘頻率范圍映射到VCO范圍,因此可以使用IP定制參數來優化預期的分辨率和像素時鐘頻率。

4.2、數據解碼

恢復的像素時鐘或串行時鐘與數據通道之間不存在相位關系。 此外,數據通道本身在它們之間允許相當大的偏差。 所以解碼器塊需要將串行時鐘的相位與數據位對齊,并在每個數據流中找到字符邊界。 由于這必須在三個數據通道中的每一個上獨立完成,因此在保持時鐘相位固定的同時改變數據流的相位是有意義的。

4.2.1、同步

為了幫助同步,DVI協議規定了要發送的周期線索(控制令牌)。這些控制令牌與數據的其余部分充分不同,它們的繼承可用于同步。當檢測到并恢復穩定的時鐘時,同步會自動(重新)開始。鎖定所需的時間取決于時鐘和數據流的相位關系。它不應該持續超過1分鐘。

DVI字符的長度為10位,因此需要對數據流進行10:1的反序列化。這可以通過級聯DDR配置中的兩個ISERDESE2原語來實現。在這種配置中,主機和從機ISERDESE2接收串行數據流并在串行時鐘的兩個邊沿對其進行采樣。因此,對于每五個串行時鐘周期,十個數據位被采樣。這個10位數據然后與一個分頻時鐘同步輸出,這是我們來自時鐘恢復模塊的像素時鐘。雖然這可以從數據流中恢復10位字,并且頻率可以傳遞給FPGA內部的通用邏輯,但確實保證字實際上始于字符邊界,或者數據穩定時采樣數據流。

為了找到采樣數據流的最佳時刻(即,睜眼的中間),在ISERDESE2之前插入IDELAYE2基元。該原語能夠以分接增量來延遲數據信號。在這個IP中,一個78ps的增量用于總共32個增量。對于支持的最高像素時鐘頻率(165 MHz),以7個抽頭增量覆蓋一個位周期。目標是找到抽頭延遲值,將數據移動到足夠的位置,以便在穩定區域的中間進行采樣。相位對齊模塊將10位字與四個特殊控制令牌進行比較。如果在超時時段內未識別出連續的令牌,則我們處于抖動區域,并且會增加抽頭延遲。這一直重復進行,直到控制令牌被可靠地識別并且算法穩定在穩定位周期(開放眼睛)的中間。一個“開放的眼睛”是由一系列最小數量的抽頭值(3)定義的,其中控制令牌可以被可靠地檢測到,并且它在兩端由一個抽頭值定界,但不能。但是,使用此定義將會漏掉開始或結束于分接延遲范圍(0或31)末端的睜眼,因為不會找到兩個抖動分隔符。所以即使睜開的眼睛在四肢開始或結束,如果它足夠長(16次增量),它將被視為有效的眼睛。但是,IDELAYE2原語僅在位級別上提供了精細的相位調整,而不是覆蓋整個字符。為了找到字符邊界,需要粗略的相位調整。這是通過ISERDESE2原語的“bitslip”功能實現的。如果所有的分接增量都已經嘗試過,并且控制標記還沒有被檢測到,那么就認為我們不在正確的字符邊界。在這種情況下,調用“bitslip”會導致在10位字中右移一位或在hree中左移一位。 “bitslip”完成后,相位對齊再次開始,循環通過抽頭增量。直到找到令牌。當在所有數據通道上可靠地檢測到連續的控制令牌時,認為相位對齊完成。此時所有三個數據通道都被認為是有效的。

然而,由于對間信道時滯不可忽略且信道獨立對齊,所恢復的數據流可能具有不同的延遲。為了消除這種偏差,通道通過在FIFO存儲器中緩沖并獨立保持它們直到視頻消隱周期同時在所有三個時間同時開始而被結合。在這個階段,所有三個數據通道都是有效的并且是同步的。

4.2.2、 解碼

TMDS標準對數據進行編碼,以便串行數據流包含很少的轉換(0到1或1到0)和一個DC平衡(長時間內相同數量的零和1)。 每個10位字符實際上封裝了8位有用數據。 這個例外是控制令牌,它封裝了2位控制數據。 數據解碼器模塊應用DVI 1.0規范中規定的解碼算法。 在解碼之后,我們在消隱期間留下控制數據或者在有效期內保留像素數據。 由于每個數據通道攜帶一種顏色,因此從IP輸出一個24位RGB像素總線。

4.3、 EDID ROM(數據顯示通道)

DDC模塊模擬包含缺省Digilent品牌擴展顯示標識數據(EDID)的只讀存儲器。 有四種變體只在首選分辨率上有所不同。 該參數是用戶可在IP自定義向導中選擇的。 EDID在與IP捆綁在一起的src / *。data文件中定義(參見第6.4節)。 合成后,對應于首選分辨率的文件將被納入網表。 允許修改這些文件,只要它與DDC規范兼容即可。

5、端口描述

表1列出了DVI至VGA內核的信號。

6、 圍繞IP核設計

6.1、 約束

TMDS時鐘輸入Clk_p / n被限制在最大DVI時鐘頻率165 MHz的IP中。 在某些體系結構中,這可能導致無法實現。 根據應用的不同,如果較低的像素時鐘頻率可以接受,則時鐘可以被限制在頂層,這將覆蓋IP內部約束。

例如,要限制720p分辨率(74.25 MHz)的設計,計算de clock period(13.468ns),并將以下內容添加到項目XDC文件中,以約束頂層輸入端口上的時鐘:

create_clock -period 13.468 -waveform {0.000 5.000} [get_ports hdmi_rx_clk_p]

6.2、 定制

IP提供以下可自定義的參數:復位信號的極性,PixelClk時鐘緩沖器類型,TMDS時鐘的頻率范圍,調試邏輯的實例化,要在捆綁的EDID中聲明的首選分辨率,DDC通道的可用性,和串行時鐘輸出。啟用DDC通道和串行時鐘將會將相應端口添加到IP中,并可用于用戶邏輯。并行像素時鐘(PixelClk)通過使用BUFR緩沖器進行恢復。由于BUFR僅限于一個時鐘區域,并且從內核輸出的視頻數據與PixelClk同步,因此任何下游消耗視頻數據的邏輯也都受限于此時鐘區域。重新緩沖PixelClk的選項在BUFR之后引入BUFG,并將視頻數據重新注冊到BUFG域。這將允許下游邏輯放置在設備的任何位置。通過設置預期的TMDS時鐘頻率,IP可以實例化符合時鐘恢復邏輯中時序要求的FPGA原語。如果從流中恢復的實際像素時鐘落在此處設置的范圍之外,FPGA的VCO工作范圍可能不受尊重,并且在極端情況下,時鐘恢復可能會失敗,并且視頻流將無法正確解碼。

如果啟用了DDC通道,則可以設置首選分辨率。 此處設置的分辨率將為模擬的EDID ROM選擇正確的初始化文件。 這個EDID將被連接的數據源讀出,并可能選擇以這個分辨率傳輸。

調試模塊可以通過啟用向導中的選項來實例化。 啟用它將導致合成兩個ILA內核,這些內核可用于Vivado硬件管理器來分析一些幫助調試的內部狀態信號。

6.3、SerialClk的使用

雖然快速串行時鐘通常僅用于內部反序列化,但在其他有限的情況下它可用并且有用。 這個限制源于這樣一個事實,即該時鐘的頻率通常太大(PixelClk頻率的五倍),無法為用戶邏輯提供時鐘。 例如,1080p將導致742.5 MHz SerialClk。 BUFIO原語驅動這個時鐘網絡以適應大的頻率,這只能在相同的存儲區/時鐘區域為I / O列提供時鐘。 一種情況是使用此時鐘驅動Digilent RGB2DVI內核,共享兩個內核之間的時鐘邏輯。

6.4、 EDID捆綁

IP帶有幾個EDID文件,每個EDID文件聲明不同的首選/原生分辨率。 名為* .data的文件包含Vivado合成可讀格式的256個字節的EDID數據。 每行只有一個二進制格式的字節。 字節0是文件中的第一個字節。 下表總結了人類可讀格式的EDID。 您也可以在您可以在EDID編輯器工具中打開的docs /目錄中找到* .dat文件。

7、 調試

當啟用調試模塊時,將添加兩個ILA內核,每個時鐘域一個:RefClk和PixelClk。 即使TMDS接口上沒有接收到時鐘,RefClk域也包含活動的控制邏輯。 與重置和時鐘恢復有關的信號與該ILA相關聯。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22410瀏覽量

636254 -

壓控振蕩器

+關注

關注

10文章

174瀏覽量

30508 -

DDC

+關注

關注

2文章

99瀏覽量

38259 -

視頻解碼器

+關注

關注

0文章

90瀏覽量

20356 -

差分信號

+關注

關注

4文章

408瀏覽量

29007

發布評論請先 登錄

一文解讀Digilent DVI-to-RGB視頻解碼器

一文解讀Digilent DVI-to-RGB視頻解碼器

評論