前言:

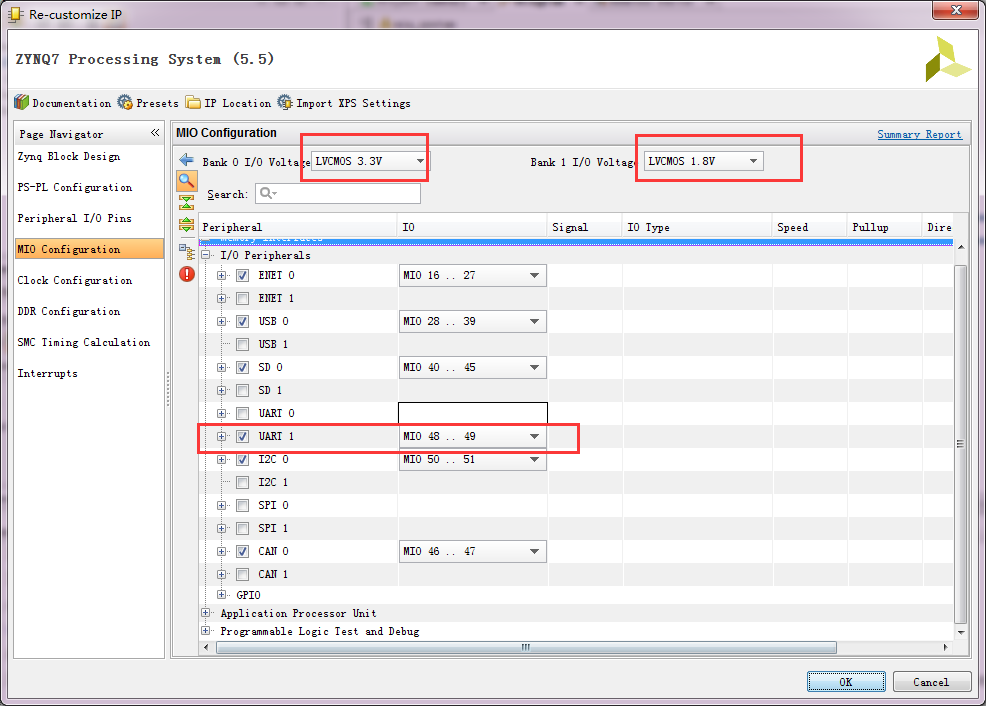

使用的板子是zc702。用Vivado的IP核搭建最小系統(tǒng),包括ARM核(CPU xc7z020),DDR3(4×256M),一個(gè)UART串口(Mini USB轉(zhuǎn)串口),純PS,通過(guò)串口打印出HelloWorld,工程雖小,五臟俱全,算是一種朝圣。配置要和板子對(duì)應(yīng),大家注意修改。

操作步驟:

硬件部分

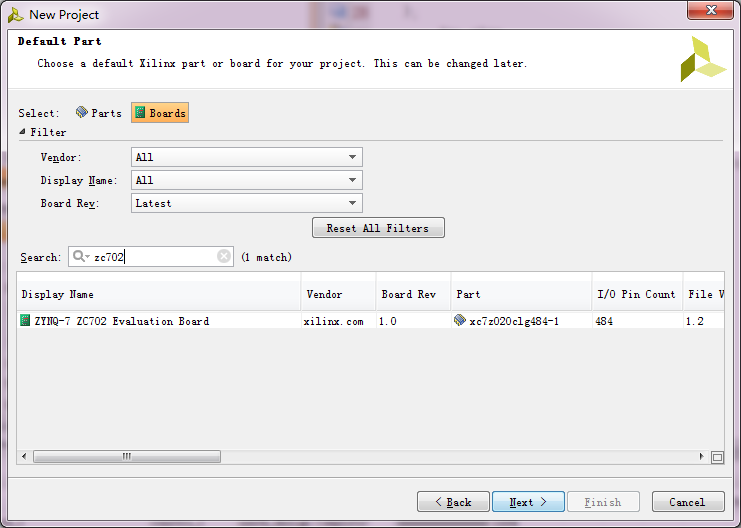

1. 新建Vivado工程。選擇芯片型號(hào)xc7z020clg484_1或者點(diǎn)擊Boards選擇zc702

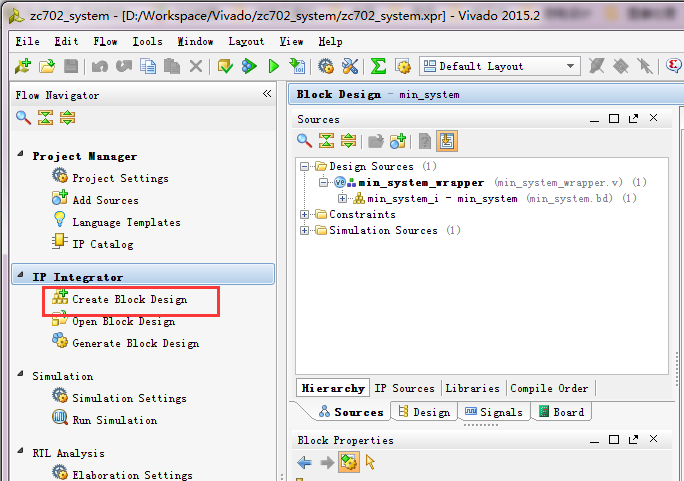

2.單擊Create Block Design, 命名

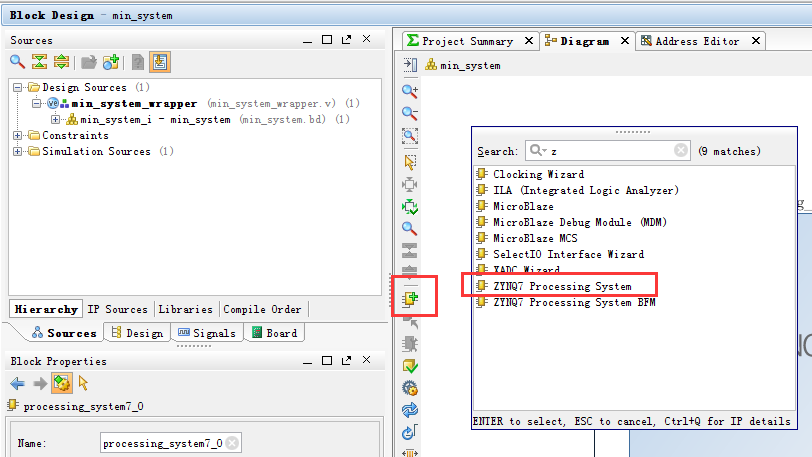

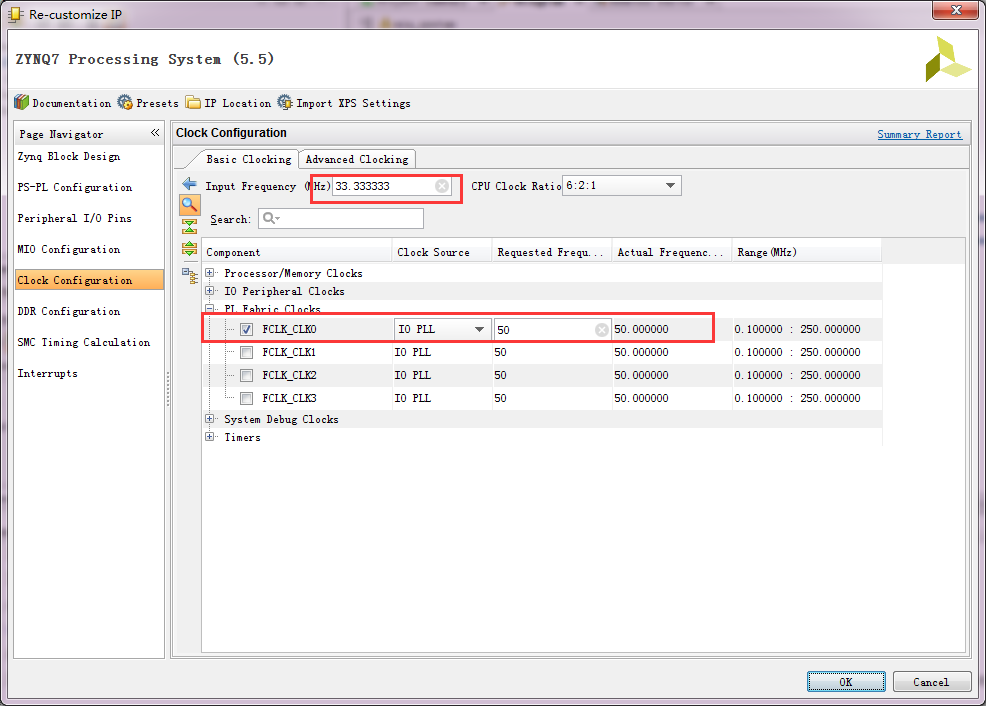

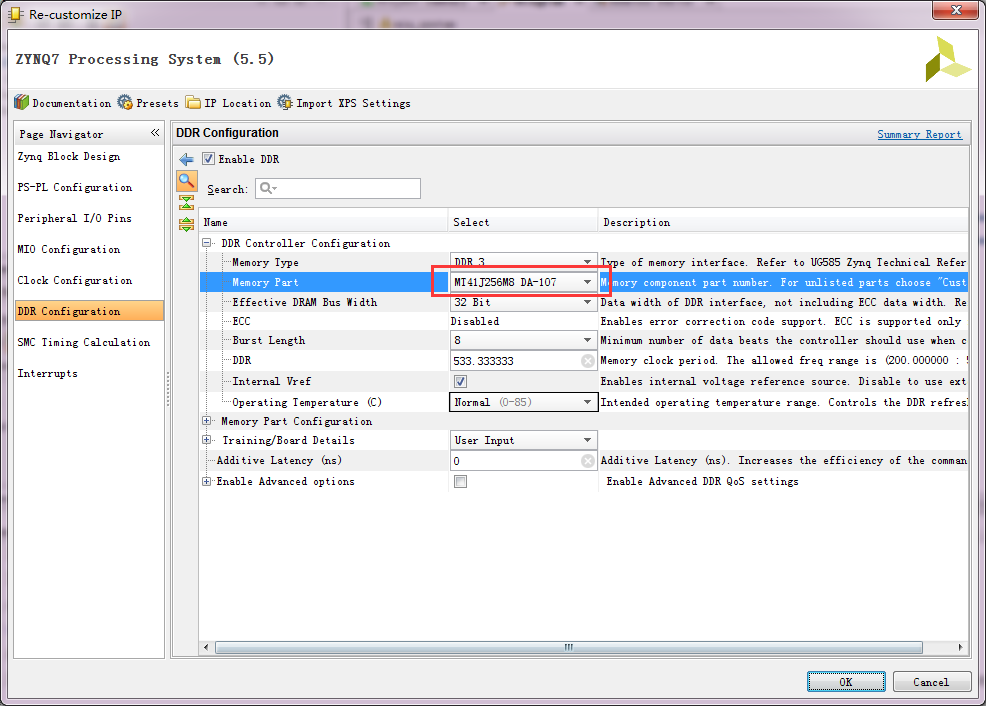

3.添加IP,ZYNQ7 Processing System

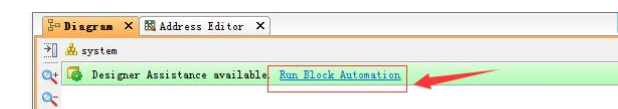

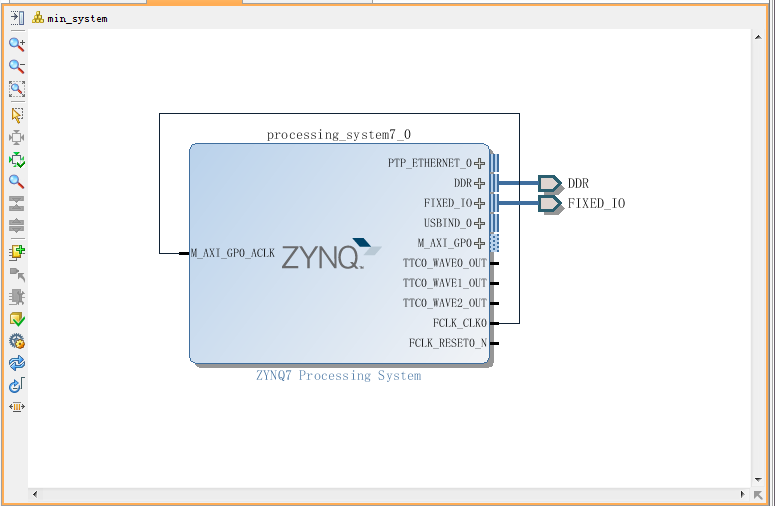

5.單擊上方藍(lán)字Run Block Automation ,然后將鼠標(biāo)放在引腳處, 鼠標(biāo)變成鉛筆后迚行拖拽連線,這是給PL時(shí)鐘,完全可以不連,本實(shí)驗(yàn)用不到。

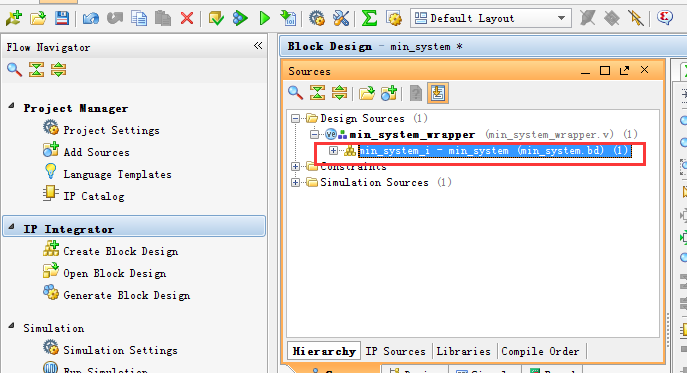

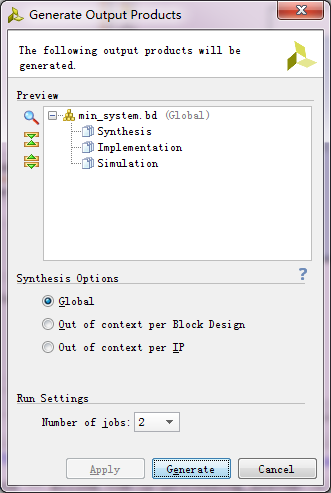

點(diǎn)擊Generate:

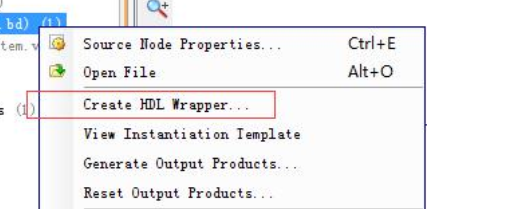

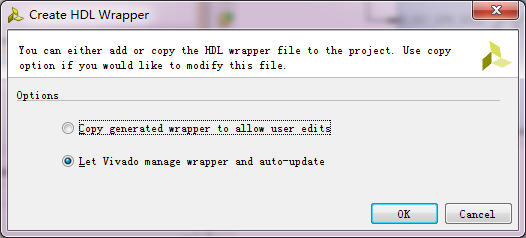

7.右擊 .bd文件, 選擇Create HDL Wrapper ,產(chǎn)生頂層文件,選擇 Let Vivado manager wrapper and auto-update 點(diǎn)擊OK

8. 產(chǎn)生Bit文件

9.File->Export->Export Hardware,勾選 Include bitstream ,點(diǎn)擊OK

10.File->Launch SDK

軟件部分

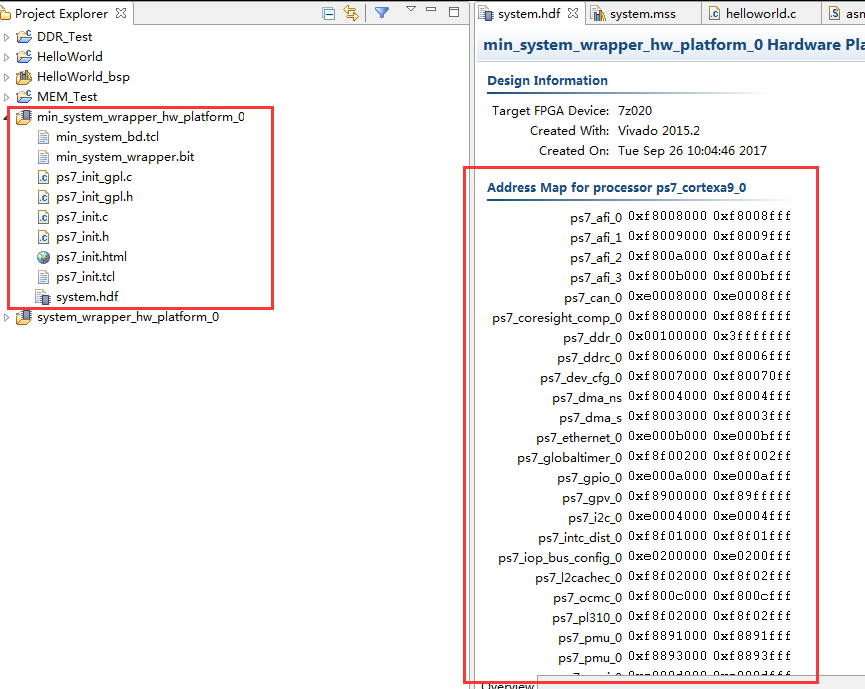

定制的硬件和地址空間分配

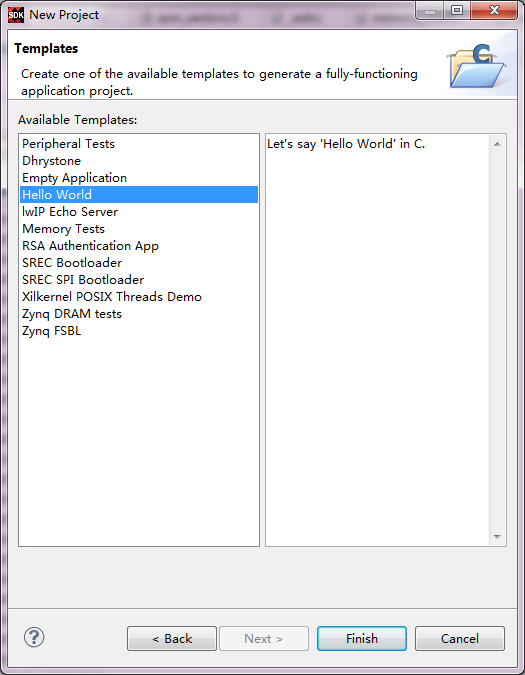

1.File->New->Application Project ,命名,點(diǎn)擊next,選擇自帶的模板HelloWorld

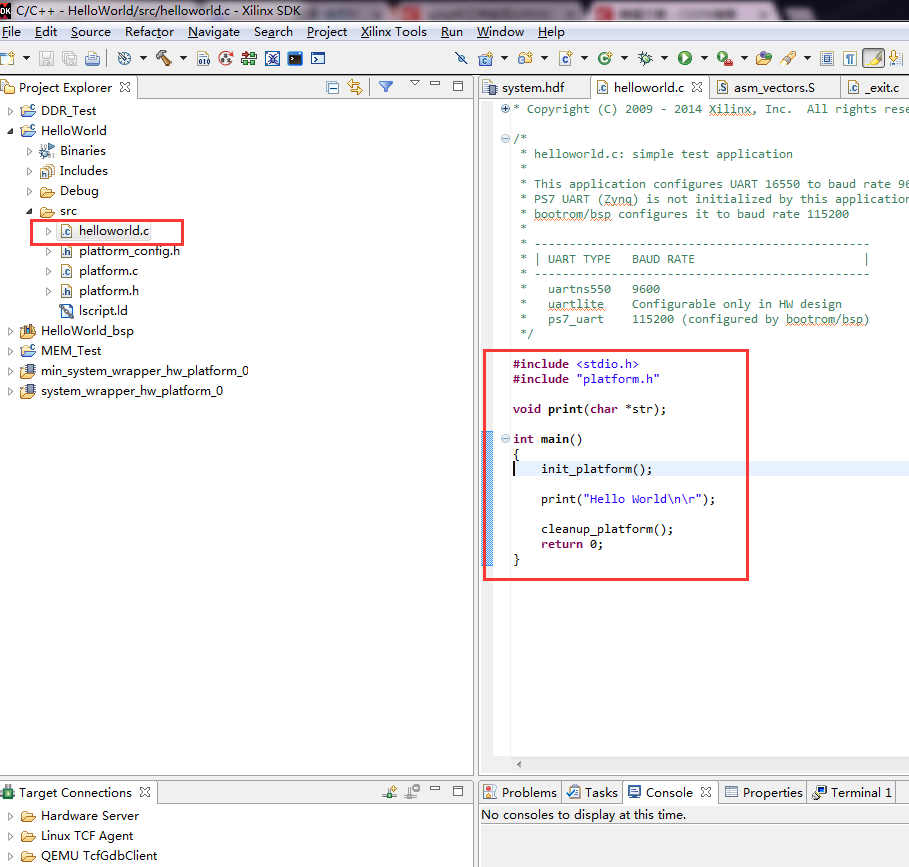

查看一下生成的代碼

3.雙擊

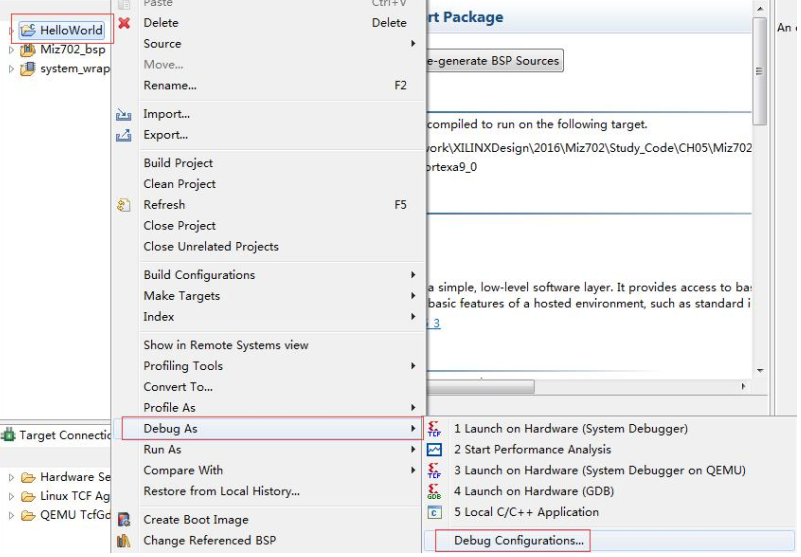

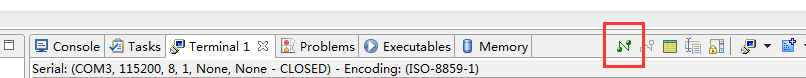

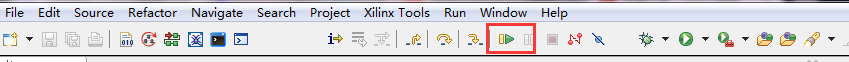

6.Debug界面 點(diǎn)擊這個(gè)啟動(dòng)程序

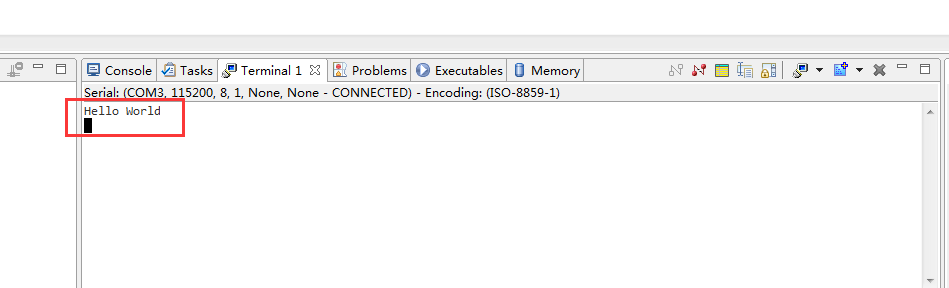

7.在串口調(diào)試助手串口Terminal里可見(jiàn)看見(jiàn)打印的信息

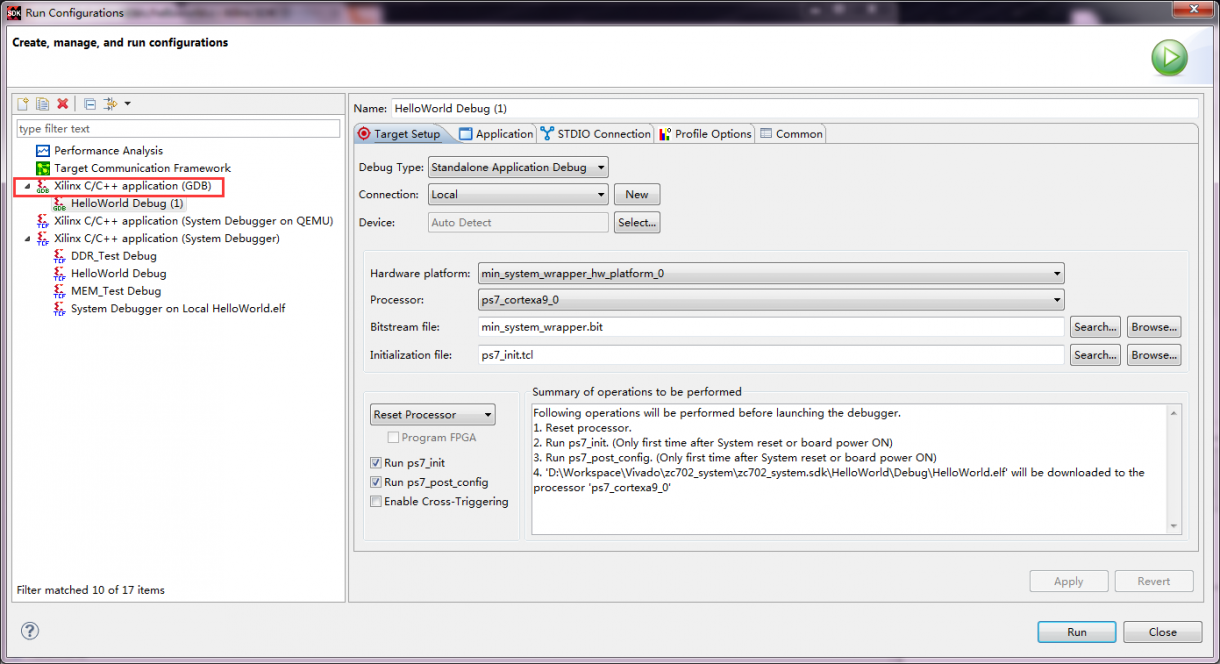

或者直接run:

右擊工程名-->run as -->run configrations

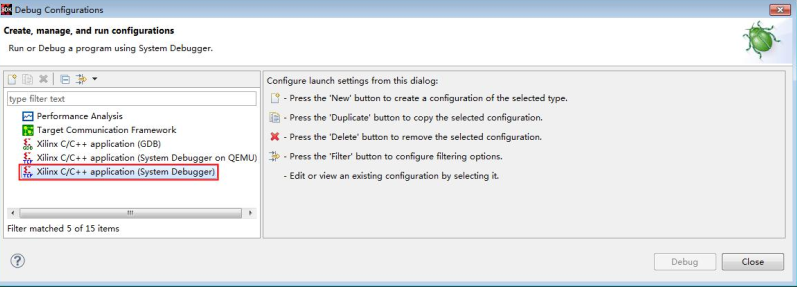

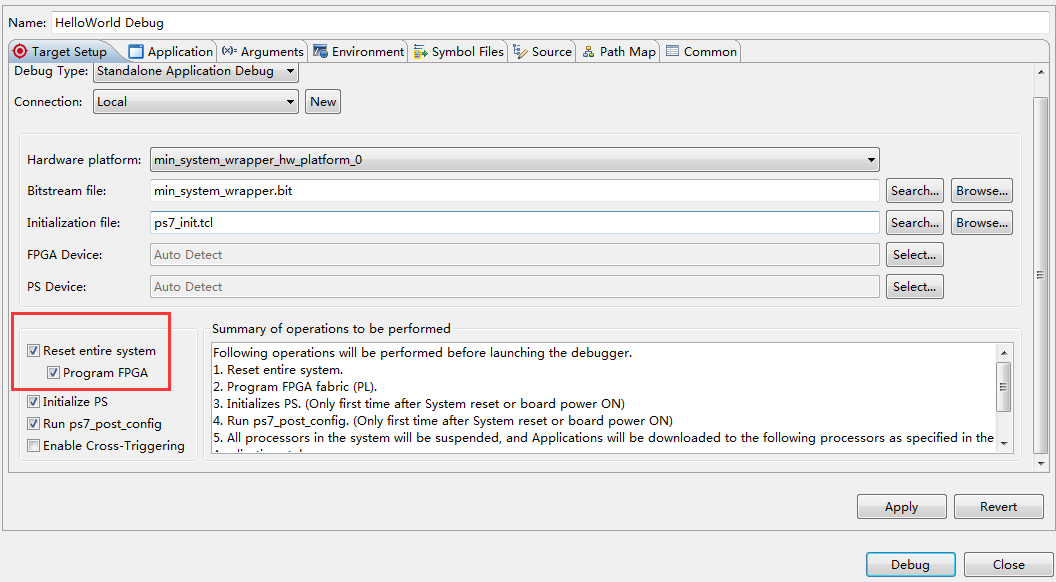

雙擊紅色框選項(xiàng):

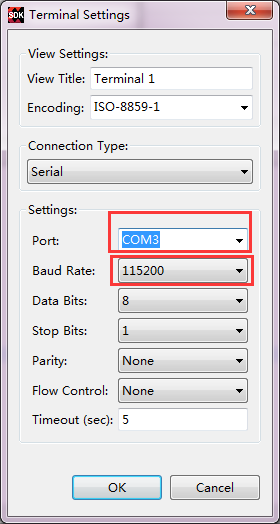

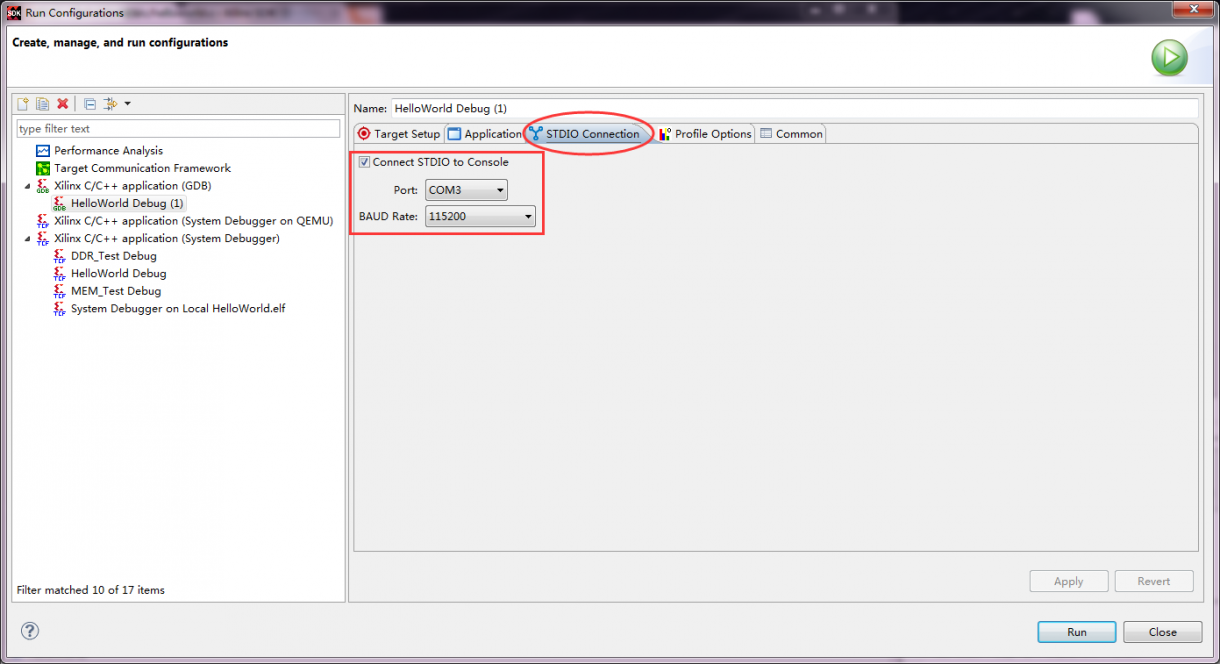

在STDIO Connection窗口設(shè)置串口信息:

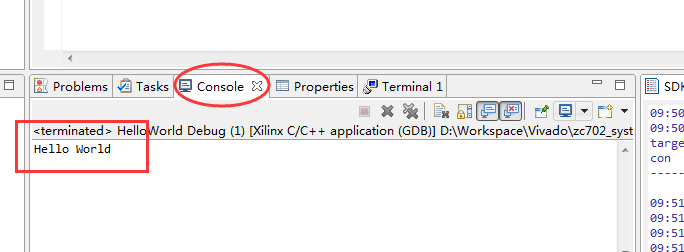

點(diǎn)擊Apply,點(diǎn)擊Run,在Console窗口可以看見(jiàn)打印的信息:

總結(jié):

Vivado+SDK設(shè)計(jì)流程初識(shí),里面的每一步要在后續(xù)過(guò)程中理解是什么意思,就不會(huì)云里霧里了。軟件部分的編程也是今后學(xué)習(xí)的一個(gè)要點(diǎn)。

-

Xilinx

+關(guān)注

關(guān)注

73文章

2200瀏覽量

131125 -

Zynq

+關(guān)注

關(guān)注

10文章

630瀏覽量

49447 -

Vivado

+關(guān)注

關(guān)注

19文章

857瀏覽量

71106 -

helloworld

+關(guān)注

關(guān)注

0文章

13瀏覽量

4665

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx Zynq-7000SOC的相關(guān)資料推薦

NOW!Xilinx SDSoC開(kāi)發(fā)環(huán)境支持16nm Zynq UltraScale+ MPSoC器件

基于Xilinx Zynq SoC的“小傻瓜(Snickerdoodle)”開(kāi)發(fā)套件

如何使用Xilinx的仿真平臺(tái)加速自己的開(kāi)發(fā)

使用Xilinx SDK進(jìn)行Zynq裸金屬應(yīng)用程序開(kāi)發(fā)

Xilinx:如何使用Zynq仿真平臺(tái)

如何使用Xilinx SDK創(chuàng)建Zynq引導(dǎo)映像

基于Xilinx Zynq SoC的“小傻瓜(Snickerdoodle)”開(kāi)發(fā)套件

使用XIlinx的FPGA芯片開(kāi)發(fā)的流水燈實(shí)驗(yàn)工程文件免費(fèi)下載

Vitis IDE入門(mén)helloworld程序

第一個(gè)Xilinx Vitis IDE入門(mén)helloworld程序

Xilinx Zynq上FreeRTOS的Tracealyzer

Xilinx ZYNQ開(kāi)發(fā)案例HelloWorld實(shí)驗(yàn)工程

Xilinx ZYNQ開(kāi)發(fā)案例HelloWorld實(shí)驗(yàn)工程

評(píng)論