在大部分的教科書中,都會提到如何分頻,包括奇數分頻,偶數分頻,小數分頻等。

1、DDS相位累加器

(1)DDS合成流程

首先講述DSS(直接頻率合成法)的原理。

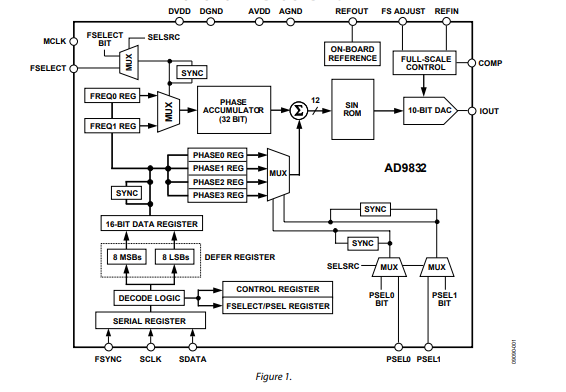

DDS是重要的頻率合成方法,在波形發生器中有極其重要的應用。DDS主要由以下幾部分組成:

a) 相位累加器

b) RAM數據讀取

c) D/A轉換器

d) 低通濾波器

直接頻率合成法的流程圖,有固定模塊,輸入頻率控制器,輸出固定頻率的波形。如下圖:

此電路最主要模塊是相位累加器,通過相位累加器循環計數,循環讀取RAM的數據,從而得到固定頻率的波形數據。

(2)相位累加器原理

相位累加原理流程如下:

輸入頻率控制字,根據算法,來實現相位的變化,分析如下所示:

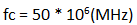

假定FPGA基準頻率為50MHz,即基準頻率:

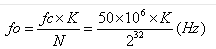

假定計數器為32位計數器,即:

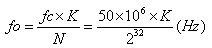

K為頻率控制字,則相位輸出的頻率為:

即:

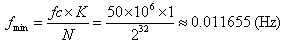

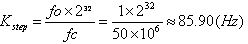

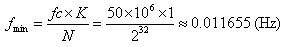

根據相位累加原理,以及RAM緩存讀取數據,每一次0~(N-1)的循環, RAM數據間隔K讀取一次。當K=1的時候,公式能輸出最小頻率,即:

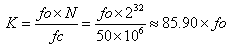

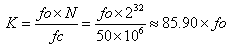

最小波形頻率步進為0.011655Hz。當fo=1Hz的時候:

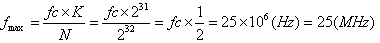

所以,頻率每變化1Hz,K的步進為85.90。當K=N/2的時候,公式能輸出最大頻率(因為每個CLK跳變一次),此時:

因此,根據頻率控制字K的變化,能輸出及固定頻率的波形。

2、任意頻率分頻原理

在FPGA中某些應用場合,對頻率要求比較高的情況下,用相位累加器原理來生成固定頻率的方法,未嘗不可。

我們規定,對Cnt進行對半50%拆分,具體如下:當cnt < N/2時,f0 = 0,也就是低電平;而當cnt > N/2時,f0 = 2,也就是低電平。

同理:

在FPGA中應用,Verilog代碼如下所示:

/*************************************************** * Module Name : clk_generator * Engineer : Crazy Bingo * Target Device : EP2C8Q208C8 * Tool versions : Quartus II 9.1SP1 * Create Date : 2011-6-25 * Revision : v1.0 * Description : **************************************************/ /************************************************* fc = 50MHz 50*10^6 fo = fc*K/(2^32) K = fo*(2^32)/fc = fo*(2^32)/(50*10^6) **************************************************/ module clk_generator # ( parameter FREQ_WORD = 32'd8590 //1KHz ) ( input clk, //50MHz input rst_n, //clock reset output reg clk_out ); //************************************************/ reg [31:0] max_value; always@(posedge clk or negedge rst_n) begin if(!rst_n) max_value <= 1'b0; else max_value <= max_value + FREQ_WORD; end //****************************************************/ always@(posedge clk or negedge rst_n) begin if(!rst_n) clk_out <= 1'b0; else begin if(max_value < 32'h7FFF_FFFF) clk_out <= 1'b0; else clk_out <= 1'b1; end end endmodule /*******************************************************/

本模塊可應用在多個對頻率精準度要求比較高的工程中(如UART中,需要115200Hz的bps,用這種任意分頻的原理來得到精準的方法,一定程度上能夠提高數據傳輸的準確率)。

DDS中的相位累加器的任意分頻原理,在一般工程中同樣可以應用。在某些應用場合,還是值得考慮的。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22410瀏覽量

636255 -

低通濾波器

+關注

關注

15文章

554瀏覽量

49005 -

分頻

+關注

關注

0文章

254瀏覽量

25351 -

波形發生器

+關注

關注

3文章

320瀏覽量

32709 -

相位累加器

+關注

關注

0文章

11瀏覽量

9354

發布評論請先 登錄

探索MAX34427:SMBUS雙通道高動態范圍功率累加器

LMX1214:高性能低噪聲時鐘緩沖與分頻器的深度解析

深入解析MAX34407:SMBus 4通道寬動態范圍功率累加器

同惠TH2838精密阻抗分析儀相位測量功能原理解析

音響中軟件分頻和硬件分頻區別解析以及對音質和成本的影響

基于E203 RISC-V的音頻信號處理系統 -協處理器的乘累加過程

普源信號發生器DG5000直接數字合成(DDS)

同惠TH2838精密LCR測試儀相位測量功能原理解析

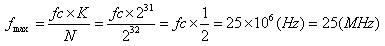

MAX9377/MAX9378任意邏輯至LVPECL/LVDS轉換器,引腳可設置四分頻電路技術手冊

相位累加器的實現原理

基于 FPGA 的任意波形發生器+低通濾波器系統設計

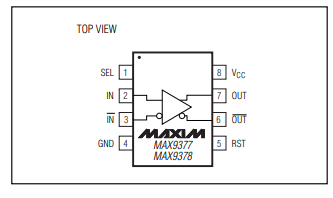

AD9835 50MHz直接數字頻率合成器、波形發生器技術手冊

AD9832 25MHZ直接數字頻率合成器、波形發生器技術手冊

ADF4151小數N/整數N分頻PLL頻率合成器技術手冊

HMC705LP4/HMC705LP4E 6.5GHz可編程分頻器SMT技術手冊

基于相位累加器的任意分頻原理解析

基于相位累加器的任意分頻原理解析

評論