為保證信號傳輸質量、降低EMI干擾、通過相關的阻抗測試認證,需要對PCB關鍵信號進行阻抗匹配設計。本設計指南是綜合常用計算參數、電視機產品信號特點、PCB Layout實際需求、SI9000軟件計算、PCB供應商反饋信息等,而最終得出此推薦設計。適用于大部分PCB供應商的制程工藝標準和具有阻抗控制要求的PCB板設計。

一、 雙面板阻抗設計

100歐姆差分阻抗推薦設計①、包地設計:線寬、間距 7/5/7 mil地線寬度≥20mil信號與地線距離6mil,每400mil內加接地過孔;②、不包地設計:線寬、間距 10/5/10mil差分對與對之間距離≥20mil(特殊情況不能小于10mil)建議整組差分信號線外采用包地屏蔽,差分信號與屏蔽地線距離≥35mil(特殊情況不能小于20mil)。90歐姆差分阻抗推薦設計①、包地設計:

線寬、間距 10/5/10mil地線寬度≥20mil信號與地線距離6mil或5mil,每400mil內加接地過孔;②、不包地設計:

線寬、間距 16/5/16mil差分對與對之間距離≥20mil建議整組差分信號線外采用包地屏蔽,差分信號與屏蔽地線距離≥35mil(特殊情況不能小于20mil)。要領:優先使用包地設計,走線較短并且有完整地平面可采用不包地設計;計算參數:板材FR-4,板厚1.6mm+/-10%,板材介電常數4.4+/-0.2,銅厚1.0盎司(1.4mil)阻焊油厚度 0.6±0.2mil,介電常數 3.5+/-0.3

圖1 包地設計

圖2 不包地設計

二、 四層板阻抗設計

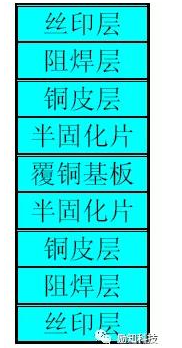

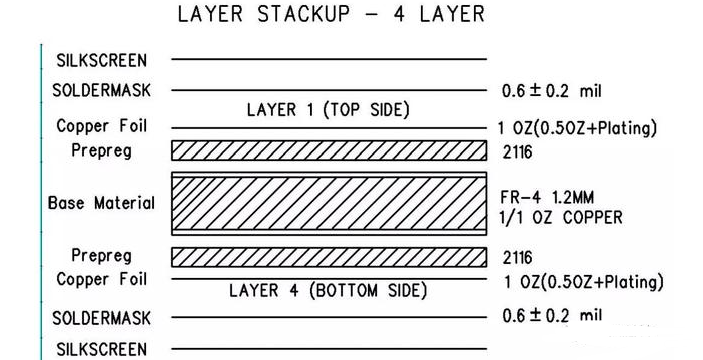

100歐姆差分阻抗推薦設計線寬、間距 5/7/5mil差分對與對之間距離≥14mil(3W準則)注:建議整組差分信號線外采用包地屏蔽, 差分信號與屏蔽地線距離≥35mil (特殊情況不能小于20mil)。90歐姆差分阻抗推薦設計線寬、間距 6/6/6mil差分對與對之間距離≥12mil(3W準則)要領:在差分對走線較長情況下,USB的差分線建議兩邊按6mil的間距包地以降 低EMI風險(包地與不包地,線寬線距標準一致)。計算參數:板材FR-4,板厚1.6mm+/-10%,板材介電常數4.4+/-0.2,銅厚1.0盎司(1.4mil)半固化片(PP) 2116(4.0-5.0mil),介電常數4.3+/-0.2阻焊油厚度 0.6±0.2mil,介電常數 3.5+/-0.3疊層結構:絲印層阻焊層銅皮層半固化片覆銅基板半固化片銅皮層阻焊層絲印層

圖3

三、 六層板阻抗設計

六層板疊層結構針對不同的場合會有不同,本指南只對比較常見的疊層(見圖 2)進行了設計推薦,后面的推薦設計都是以圖2的疊層下得到的數據。外層走線的阻抗設計與四層板相同因內層走線一般情況下比表層走線多了個平面層,電磁環境與表層不同以下是第三層走線阻抗控制建議(疊層參考圖4)100歐姆差分阻抗推薦設計線寬、間距 6/10/6 mil差分對與對之間距離≥20mil(3W準則);90歐姆差分阻抗推薦設計線寬、線距 8/10/8 mil差分對與對之間距離≥20mil(3W準則);計算參數:板材FR-4,板厚1.6mm+/-10%,板材介電常數4.4+/-0.2,銅厚1.0盎司(1.4mil)半固化片(PP) 2116(4.0-5.0mil),介電常數4.3+/-0.2阻焊油厚度 0.6±0.2mil,介電常數 3.5+/-0.3疊層結構:頂層絲印阻焊層銅皮層半固化片覆銅基板半固化片覆銅基板半固化片銅皮層阻焊層底層絲印

圖4

四、 六層以上,請按相關的規則自行設計或咨詢相關人員確定疊層結構及走線方案。

注:①、影響阻抗的情況較多,需要阻抗控制的PCB仍需要在PCB設計資料或樣板單中標 明阻抗控制要求;②、100歐姆差分阻抗主要用于HDMI、LVDS信號,其中HDMI需要通過相關認證是強制要求;③、90歐姆差分阻抗主要用于USB信號;④、單端50歐姆阻抗主要用于DDR部分信號,鑒于DDR顆粒大部分采用內部調節匹配阻抗設計,設計以方案公司提供Demo板為參考,本設計指南不作推薦;⑤、單端75歐姆阻抗主要用于模擬視頻輸入輸出,在線路設計上都有一顆75歐姆的電阻對地電阻進行了匹配,所以在PCB Layout中不需要再進行阻抗匹配設計,但需要注意線路中的75歐姆接地電阻應靠近端子引腳放置。常用PP

阻焊油厚:0.6±0.2mil Cer=3.5+/-0.3

編輯:hfy

-

PCB板

+關注

關注

27文章

1496瀏覽量

55218 -

阻抗

+關注

關注

17文章

988瀏覽量

49235 -

阻抗控制

+關注

關注

1文章

57瀏覽量

11161

發布評論請先 登錄

阻抗匹配解析:原理、影響與工程實踐

線路板阻抗匹配:實操中要避開的 3 個設計誤區

線路板阻抗匹配實操:過孔與拐角的處理技巧

極細同軸線阻抗不匹配的后果與解決辦法

技術資訊 I 信號完整性與阻抗匹配的關系

基于史密斯圓圖實現天線阻抗匹配

極細同軸線(micro coaxial cable)的阻抗匹配原理

村田貼片電容的阻抗匹配問題如何解決?

村田貼片電容的高頻特性與阻抗匹配

如何確保模擬示波器的輸入阻抗匹配?

BNC 接頭阻抗匹配:接線中的關鍵技術與注意事項

PCB設計之阻抗匹配設計方案

PCB設計之阻抗匹配設計方案

評論