Overlay 簡介

RISC-V-On-PYNQ Overlay實現(xiàn)了在PYNQ-Z2板上的RISC-V處理器及工具鏈集成,并提供了完整的RISC-V源碼與設計流程,得益于PYNQ軟件框架,其支持在Jupyter Notebook對RISC-V進行編譯、調(diào)試與驗證,即可以在Jupyter Notebook上編寫一段C/C++/RISC-V匯編程序,將編譯后的二進制文件放到picoRV32上運行。

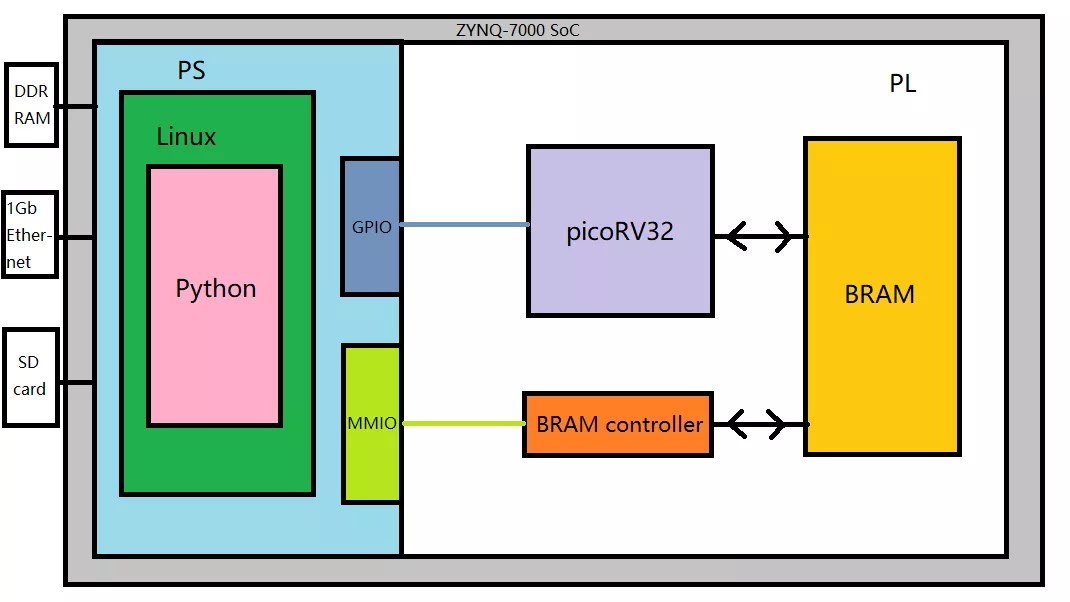

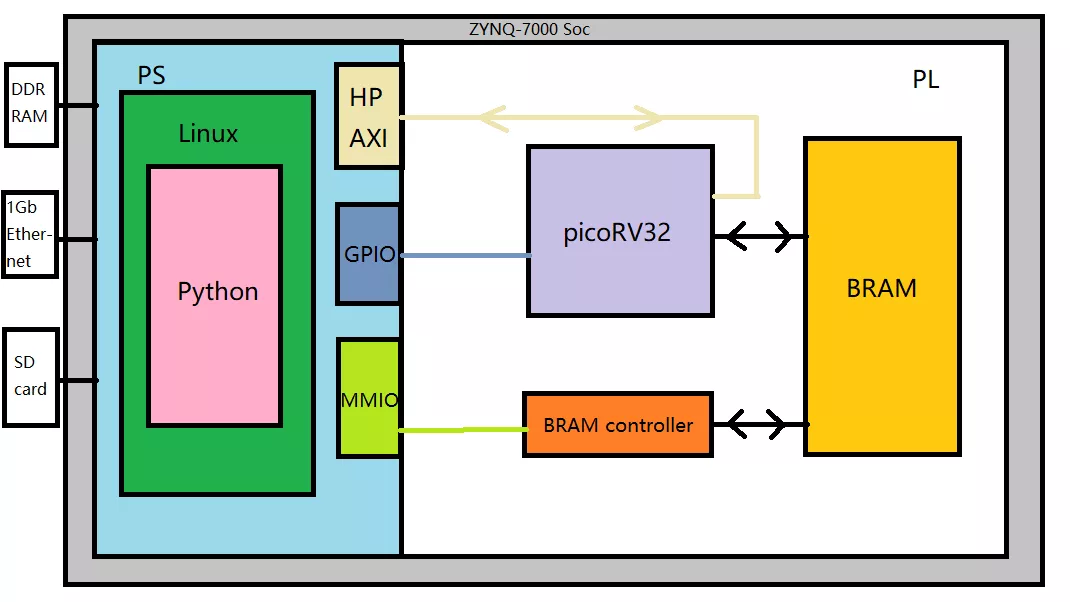

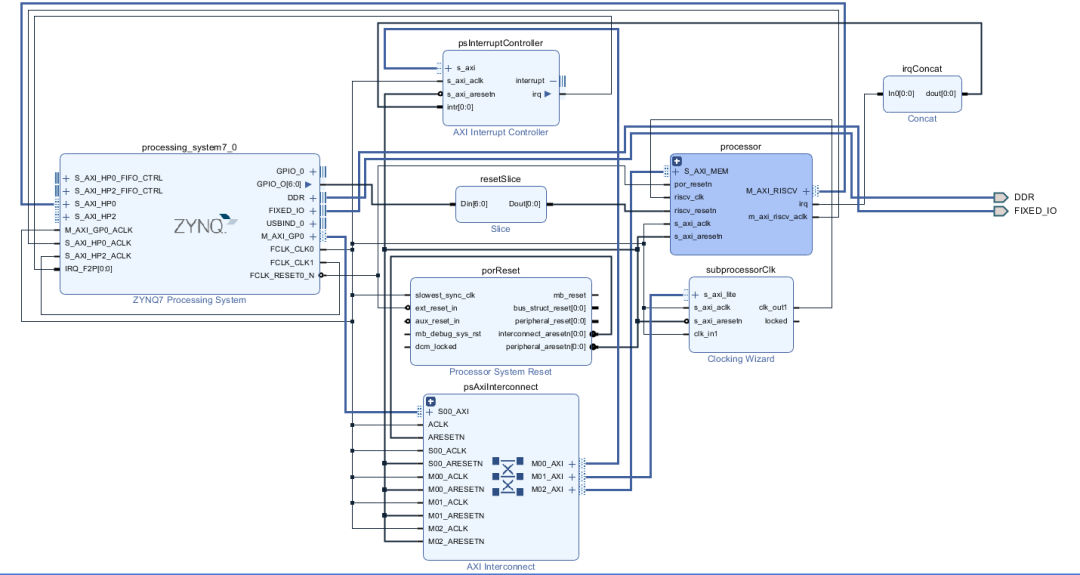

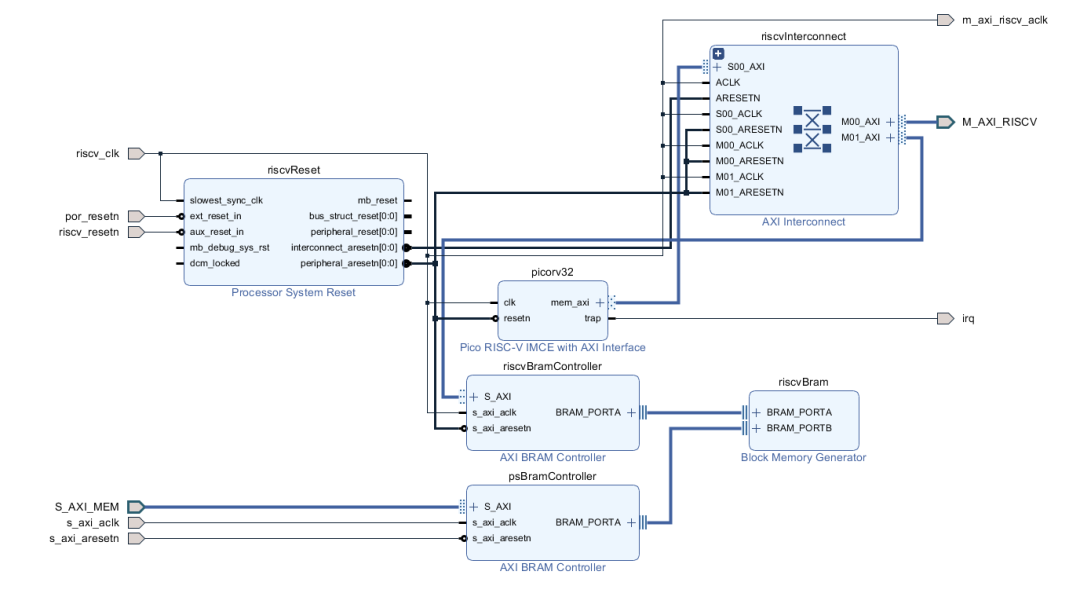

以下兩張圖是本Overlay的系統(tǒng)框圖,其中picoRV32是一個開源的RISC-V核,它具有占用資源少的特點,并且它自帶AXI接口,可以方便地使用Xilinx提供的各種基于AXI總線的IP。本項目有兩個工程,它們的區(qū)別主要是picoRV32接的RAM:上圖只使用BRAM,而下圖同時使用到了BRAM和外部DRAM。

快速開始

- 環(huán)境需求PYNQ V2.4。

- 在PS端,我們需要編譯安裝RISC-V工具鏈和對應的庫。

Github內(nèi)的項目文件Clone到本地。

git clone

https://github.com/Siudya/RISC-V-On-PYNQ.git /home/xilinx/ RISC-V-On-PYNQ

在RISC-V-On-PYNQ/notebooks/tutorial中有5個Notebook,包含了Overlay完整的部署流程。

鑒于從零開始部署的時間會較長,所以我們也提供了完整的鏡像文件,直接燒錄到SD卡就可以運行(注:提供的ext4分區(qū)剩余容量較小,請用戶根據(jù)需要自行調(diào)整)。

在OpenHW的遠程PYNQ實驗平臺上也已經(jīng)為大家安裝好了環(huán)境,可以直接使用。

示例Notebook

裝好Overlay后,打開RISC-V-Examples/PicoRV32 Processor Mixed-Memory Processor Demo.ipynb,這是使用DRAM和BRAM混合儲存器的示例工程。實際上代碼與使用只BRAM的工程類似,只不過使用了不同的bit文件。

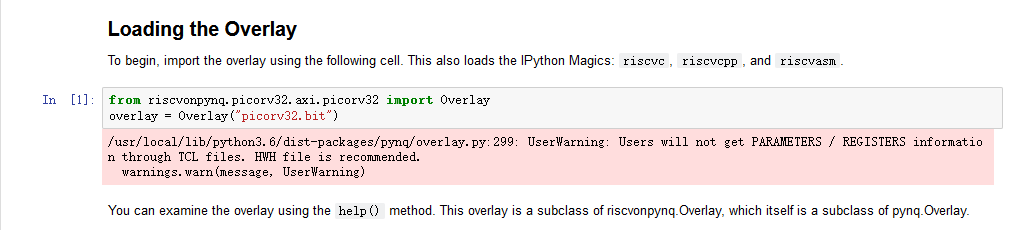

開始時下載bit文件,在這個過程中所有驅(qū)動都會注冊完成。

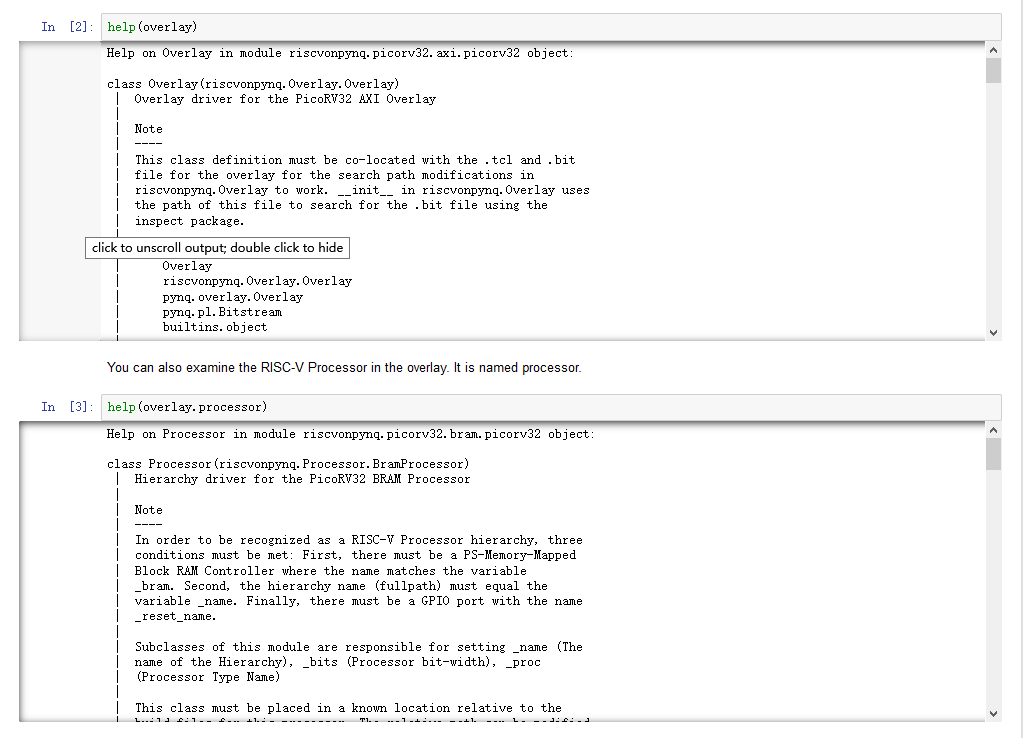

可以用help函數(shù)查看Overlay和processor的有關(guān)信息,可以看到,這里的Overlay和processor使用了本項目設計的驅(qū)動,這說明驅(qū)動注冊成功了。

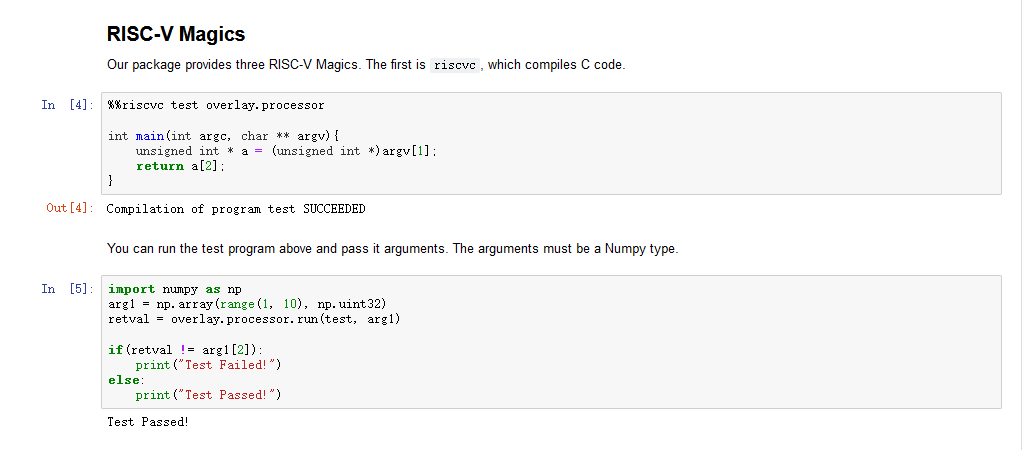

在Notebook中包含了一段C程序,作用是返回一個數(shù)組的第二個元素。可以看到我們使用了python magics來聲明并編譯一段C程序,這和PYNQ本身對Microblaze核的編程方法類似。然后調(diào)用processor的run方法將程序裝載進RAM中來運行picoRV32。

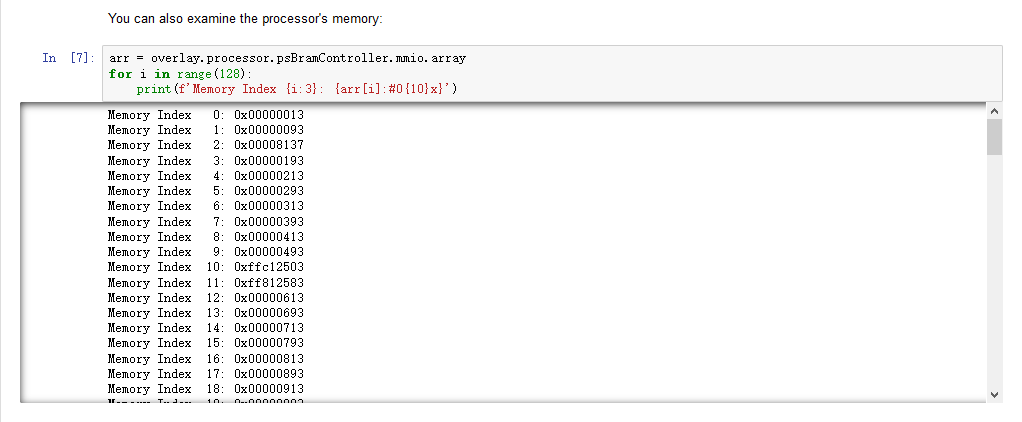

我們也可以調(diào)用BRAM controller的mmio來看看內(nèi)存的情況。在這之后也有使用C++和匯編程序的例子,這里不作贅述,讀者通過執(zhí)行Jupyter Notebook中的代碼來體驗。

Overlay詳解

- PS與PL功能劃分

PS部分主要是用Python通過PYNQ框架控制PL中各IP的運行。

PL部分則例化一個pcioRV32核和和BRAM。

- Vivado工程block design介紹

具體硬件設計是這樣的:

上圖是項目的總體布局,下圖是processor展開后的內(nèi)容。

其中BRAM是一個雙口RAM,它兩端連接的是PS和picoRV32。另外,可以看到PS的GPIO連接的是processor的復位端,當二進制程序裝入BRAM后,復位picoRV32,使它運行程序。picoRV32運行結(jié)束后,會觸發(fā)一個中斷。利用這個設計,可以例化許多RISC-V核心,并讓其運行獨立的程序,實現(xiàn)一個靈活可配置的眾核處理器,事實上已經(jīng)有用這種方法實現(xiàn)了例化超過一千個RISC-V核的項目。

在Processor內(nèi)部,picoRV32通過AXI總線來訪問其他IP,可以使用AXI總線來給它增加各種各樣不同的外設。在這里,本項目只是添加了另一個內(nèi)存(通過PS的HP AXI 0接口訪問內(nèi)存控制器)。

另外,這里的picoRV32核心的運行頻率可以通過利用AXI總線配置時鐘資源來調(diào)整。

注意:RISC-V核的hierarchy名字必須為processor,并且processor中的復位模塊必須為rscvReset。如果改動這些名字,必須修改對應的驅(qū)動源文件,否則不能正確加載驅(qū)動。

Overlay API介紹

在此工程中,通過riscvc、riscvcpp和riscvasm這三個python magics來編譯一段程序。例如:%%riscvcpp test_cpp overlay.processor。其中test_cpp是程序的名字,overlay.processor是想要寫入的RISCV核hierarchy的名字。然后在本cell中編寫代碼,運行后將調(diào)用前面安裝的RISC-V的工具鏈編譯。

編譯成功后,利用processor的run方法運行程序。例如:overlay.processor.run(test_cpp, test_cpp_arg)。其中test_cpp是程序名字,test_cpp_arg是參數(shù)數(shù)組,它兼容numpy的類型。

對于更詳細的解釋,可以參看前面的tutorial中5個notebook和項目中的.py源文件。

編輯:hfy

-

Xilinx

+關(guān)注

關(guān)注

73文章

2205瀏覽量

131752 -

AXI

+關(guān)注

關(guān)注

1文章

145瀏覽量

18003 -

內(nèi)存控制器

+關(guān)注

關(guān)注

0文章

40瀏覽量

9437 -

RISC-V

+關(guān)注

關(guān)注

49文章

2933瀏覽量

53449

發(fā)布評論請先 登錄

RT-Thread 邀您參與“開放?連接”2026玄鐵 RISC-V 生態(tài)大會,攜手共鑄 RISC-V“芯”紀元

RISC-V不支持 Nx嗎?

重磅合作!Quintauris 聯(lián)手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

為什么RISC-V是嵌入式應用的最佳選擇

RISC-V B擴展介紹及實現(xiàn)

大灣區(qū)RISC-V生態(tài)全景展示:RISC-V生態(tài)發(fā)展論壇、開發(fā)者Workshop和生態(tài)應用專區(qū)

普華基礎軟件亮相2025 RISC-V中國峰會

RISC-V 手冊

2025新思科技RISC-V科技日活動圓滿結(jié)束

時擎科技亮相2025 RISC-V中國峰會,深度解析高性能RISC-V SoC技術(shù)挑戰(zhàn)與創(chuàng)新

RISC-V 發(fā)展態(tài)勢與紅帽系統(tǒng)適配進展

RISC-V 的平臺思維和生態(tài)思維

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

RISC-V和ARM有何區(qū)別?

RISC-V賽道的“硬核”突圍之路

自制RISC-V源碼與設計流程案例分析

自制RISC-V源碼與設計流程案例分析

評論