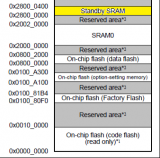

SRAM是隨機存取存儲器的一種。“靜態”是指這種存儲器只要保持通電,里面儲存的數據就可以恒常保持。SRAM不需要刷新電路即能保存它內部存儲的數據。SRAM功耗取決于它的訪問頻率。如果用高頻率訪問SRAM,其功耗比DRAM大得多。有的SRAM在全帶寬時功耗達到幾個瓦特量級。另一方面,SRAM如果用于溫和的時鐘頻率的微處理器,其功耗將非常小,在空閑狀態時功耗可以忽略不計—幾個微瓦特級別。本篇內容要介紹的是關于SRAM的基礎模塊存有三種情況:standby(空余),read(讀)和write(寫)。

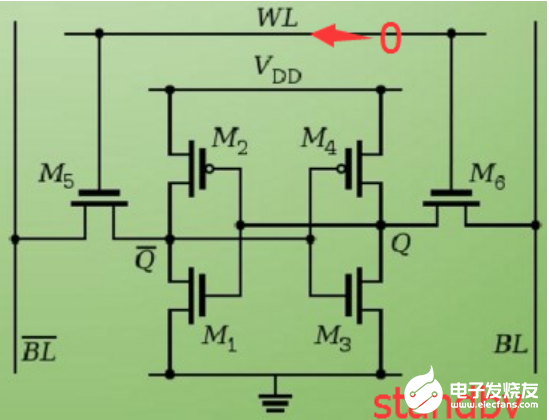

第一種情況:standby

假如WL沒有選為上拉電阻,那么M5和M62個做為操縱用的晶體三極管處在短路情況,也就是基礎模塊與基準線BL防護。而M1-M4構成的2個反相器持續保持其情況。

第二種情況:read

最先,假定儲存的內容為1,也就是Q處為上拉電阻。讀周期時間原始,二根基準線BL,BL#預在線充值為上拉電阻,由于讀寫能力情況時,WL也會為上拉電阻,促使讓做為自動開關的2個晶體三極管M5,M6通斷。

隨后,讓Q的值傳送給基準線BL只到預充的電位差,另外泄排掉BL#預充的電。從總體上,運用M1和M5的通道立即連到低電頻使其數值低電頻,即BL#為低;另一方面,在BL一側,M4和M6通斷,把BL立即拉升。

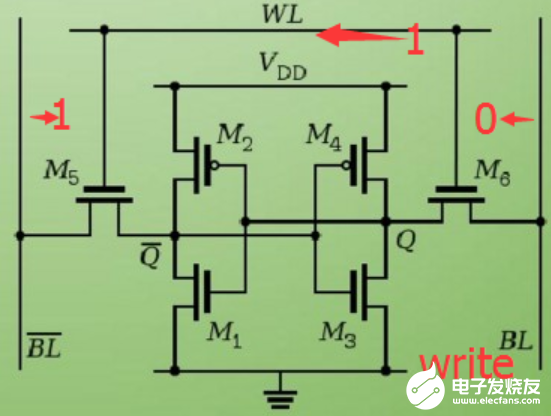

第三種情況:write

寫周期時間剛開始,最先把要載入的情況載入及時線BL,假定要載入0,那么就設定BL為0且BL#為1。隨后,WL設定為上拉電阻,這般,基準線的情況就被加載sram芯片的基礎模塊了。深入分析全過程,能夠自身畫一下。

-

sram

+關注

關注

6文章

820瀏覽量

117469 -

儲存器

+關注

關注

1文章

94瀏覽量

18121

發布評論請先 登錄

并行sram芯片介紹,并行sram芯片應用場景

基于FPGA的I2C控制模塊設計

高速數據存取同步SRAM與異步SRAM的區別

如何檢查EZ-USB? CX3 上的 SRAM 使用情況(JTAG 不可用)?

AT32F系列 PWC待機喚醒腳喚醒Standby

蜂鳥e203移植開發分享(一):無下載器的情況下固化程序

外置SRAM與芯片設計之間的平衡

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

對ringbuffer中rt_ringbuffer_put_force函數的疑問求解

緩解高性能存算一體芯片IR-drop問題的軟硬件協同設計

三大開發環境下的Standby RAM變量配置教程

SRAM的基礎模塊存的情況:standby read write

SRAM的基礎模塊存的情況:standby read write

評論