像許多其他進入系統(tǒng)硬件的商品一樣,印刷電路板(PCB)多年來發(fā)展迅速。自從大約1936年保羅·埃斯勒(Paul Eisler)發(fā)明這項發(fā)明以來,PCB已成為大多數(shù)電子組件的中樞神經(jīng)系統(tǒng)。

在此過程中,PCB變得更加復(fù)雜,這很大程度上取決于它們所容納的設(shè)備的性質(zhì)。EDA行業(yè)主要是由不斷增長的復(fù)雜性和自動化流程的需求所承擔(dān)。

在相當(dāng)長的一段時間內(nèi),電路設(shè)計師可以獨立完成工作,然后將成品扔給PCB設(shè)計者。然后,該設(shè)計師將Gerber布局文件在扔給制造商。

隨著大型球柵陣列(BGA)可編程設(shè)備,高密度互連(HDI)和對時序至關(guān)重要的差分對信號鏈路的普及,這種PCB設(shè)計方法現(xiàn)在已經(jīng)成為走向災(zāi)難的路線圖。不過,一些廣泛的實踐將有助于確保成功的設(shè)計而不會造成延誤,費用和重新設(shè)計的繁瑣性。

概念階段

PCB設(shè)計的第一要素是概念階段。此時,電路設(shè)計師可以并且應(yīng)該與PCB設(shè)計師合作進行技術(shù)評估。該評估將考慮以下問題:

l使用哪些組件?

l它們將容納在什么包裝中,它們將具有哪些引腳數(shù)和引腳排列?

lPCB的層堆疊將由什么組成;即基于成本/性能折衷,它應(yīng)該具有幾層?

l參數(shù)的性能目標(biāo)是什么,例如時鐘頻率和信令速度?

在此階段,設(shè)計人員還必須考慮諸如電路板總線架構(gòu)之類的元素,以及它是串行還是并行的。如果阻抗不匹配會引起反射,振鈴和其他不良影響,他們還必須考慮其阻抗匹配策略。

溝通與交流

成功進行電路板設(shè)計的關(guān)鍵,就是溝通。如今PCB設(shè)計不再是單人工作,而是工程師團隊之間的協(xié)作團隊工作。

交流貫穿PCB設(shè)計過程。電路設(shè)計團隊必須與PCB設(shè)計團隊明確交流其設(shè)計意圖。他們還必須清楚地了解其PCB設(shè)計工具可以實現(xiàn)和不能實現(xiàn)的功能。

電路設(shè)計人員對工具的功能和理解,將決定下游操作的工作是輕松還是艱難。

此外,由于電路板布線的復(fù)雜性不斷提高和信令速率提高,與傳統(tǒng)的串行流程相反,最好同時進行PCB設(shè)計。

部件的研究和選擇通常與流程的其余部分相獨立,同樣的,方案捕獲、模擬和布局階段也要獨立進行。

設(shè)計創(chuàng)建

在設(shè)計創(chuàng)建階段,工程師將進入最終組件的選擇和庫的創(chuàng)建,這反過來又有利于原理圖的創(chuàng)建。他們還將承擔(dān)約束定義和采集的任務(wù)。

在這個階段,設(shè)計師正在評估和選擇構(gòu)建模塊,他們還將前往制造商的網(wǎng)站,搜索數(shù)據(jù)表和規(guī)格。解決此問題的一種更有利的方法是將零件選擇直接轉(zhuǎn)移到原理圖采集過程中。通過以這種方式執(zhí)行示意圖采集,該過程可以用作各種實驗畫布。

在原理圖采集中,設(shè)計人員必須能夠快速添加,減去或更改組件,甚至整個設(shè)計拓?fù)洌@一點很重要。例如,正在為手機開發(fā)速度濾波器的設(shè)計人員應(yīng)在原理圖采集期間通過試驗各種電容或電感值來設(shè)置通帶和其他濾波器參數(shù)。

在創(chuàng)建原理圖時,PCB設(shè)計工具還會在后臺為電路自動創(chuàng)建網(wǎng)表。該網(wǎng)表描述了電路組件如何互連以及下游放置和布線工具如何將它們用于電路板布局。

這時設(shè)計師將為諸如FPGA或其他可編程設(shè)備之類的所謂“大型組件”創(chuàng)建符號和封裝。這也是捕獲設(shè)計約束的時候,這是一個關(guān)鍵步驟,需要進行大量考慮,尤其是在下游流程方面。

現(xiàn)在,一切都受到PCB設(shè)計的限制,它過去僅限于制造問題。但是現(xiàn)在,當(dāng)我們試圖將電路板壓入狹小空間同時仍使其可制造時,一切都受到了限制。

設(shè)計要求的確可能導(dǎo)致大量約束,但重要的是不要過度約束設(shè)計。最好是更依賴于仿真和分析,而不是僅僅限制設(shè)計。

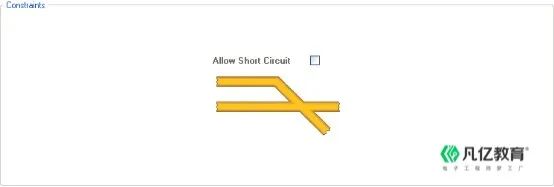

在設(shè)計創(chuàng)建過程中,工程師需要注意信號完整性問題,這些問題會在后續(xù)過程中逐漸出現(xiàn)。信號的完整性要求在設(shè)計捕獲階段以及在電路板布局過程中都要加以解決,設(shè)計流程必須支持該過程。在設(shè)計過程中,你不能忽略阻抗不匹配的問題。

仿真是關(guān)鍵

一旦電路設(shè)計完成并確定了原理圖,然后進行功能驗證。這通常是通過使用仿真工具來完成的。同樣,出于各種原因?qū)﹄娐愤M行全面的仿真。首先,它將為您很好地指示電路的行為。

人們對仿真存在誤解,它并不是要取代物理原型設(shè)計,而是要消除原型設(shè)計中的迭代。這是因為模擬使設(shè)計師能夠發(fā)現(xiàn)設(shè)計上的缺陷,而這些缺陷通常在原型設(shè)計之前是不會被發(fā)現(xiàn)的。

通過仿真,可以輕松地進行“假設(shè)”場景的實驗。您可以試驗各種設(shè)計拓?fù)浜透鞣N供應(yīng)商的替代零件,以檢查它們對電路性能的影響。

然而,與仿真一直存在的摩擦是模型的可用性及其有效性。當(dāng)今所有常用的PCB設(shè)計套件都帶有擴展的模型庫,但有時可能沒有顯示給定的零件。但是,組件供應(yīng)商越來越多地通過在其網(wǎng)站上使用Spice模型來彌補這方面的不足,因此,最好檢查一下它們。

物理原型

仿真運行以解決性能問題后,下一步就是為物理原型設(shè)計電路。布局可確保電路按照設(shè)計規(guī)范執(zhí)行。它還可以驗證電路板輪廓是否與設(shè)計尺寸相匹配。在這里,您可以與機械工程師進行共同設(shè)計。

布局階段是原理圖定義的組件之間的互連的物理表現(xiàn)。該任務(wù)是由許多EDA供應(yīng)商提供的布局布線工具執(zhí)行的。所有這些工具為工作臺帶來了不同程度的自動化,但這是一把雙刃劍。

設(shè)計人員需要判斷何時使用手動布局以及何時使用自動布局。如果要放置關(guān)鍵組件,或者必須將連接器放置在電路板邊緣附近,則無法使自動放置功能具有超越你的決定的能力。

希望在進行布局時可以考慮一些信號完整性問題。這是必須認(rèn)真處理的階段。一般的經(jīng)驗法則是,如果您的信號到達目的地的時間超過上升時間的三分之一,那么在那條路徑上就存在潛在的信號完整性問題。

最終檢查

將PCB投入生產(chǎn)之前的最后一個階段是進行最終驗證。必須檢查信號完整性和定時,以確保信號按時到達并具有足夠的質(zhì)量。這是設(shè)計約束之間的沖突將揭示并進行權(quán)衡的關(guān)頭。

最大的挑戰(zhàn)之一就是試圖將這些最終驗證步驟移至設(shè)計過程的早期階段。能夠做到這一點的關(guān)鍵是具有更好的約束條件。如果在設(shè)計創(chuàng)建過程中指定約束條件的同時進行分析,那么約束條件將得到改善。

在此階段,將最終對設(shè)計規(guī)范與其實際行為進行比較。仔細(xì)評估了物理原型的性能,以便可以很好地理解系統(tǒng)操作環(huán)境的影響并進行必要的修改。

-

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4921瀏覽量

95284 -

PCB布線

+關(guān)注

關(guān)注

22文章

473瀏覽量

43549 -

線路板設(shè)計

+關(guān)注

關(guān)注

0文章

61瀏覽量

8470 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3515瀏覽量

6402

發(fā)布評論請先 登錄

淺談晶振在PCB設(shè)計中的要點

高速PCB設(shè)計EMI避坑指南:5個實戰(zhàn)技巧

PCB設(shè)計師必看!這些‘反常識’操作正在毀掉你的電路板

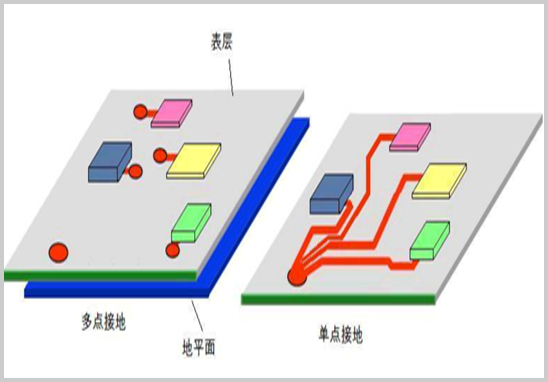

PCB設(shè)計中單點接地與多點接地的區(qū)別與設(shè)計要點

上海圖元軟件國產(chǎn)高端PCB設(shè)計解決方案

PCB設(shè)計,輕松歸檔,效率倍增!

趨勢觀察 高頻通信時代,Dk值為何成了PCB設(shè)計“生命線”?

原理圖和PCB設(shè)計中的常見錯誤

DDR模塊的PCB設(shè)計要點

Altium Designer中PCB設(shè)計規(guī)則設(shè)置

PCB設(shè)計中的通信和常識規(guī)則

PCB設(shè)計中的通信和常識規(guī)則

評論