上篇介紹了如何利用verilog實現4線SPI配置時序,本篇將以AD9249介紹其3線SPI配置的verilog實現。

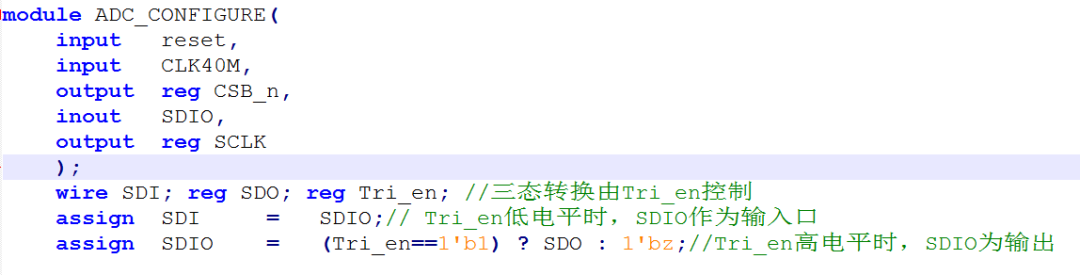

3線SPI的時鐘產生方式和上一篇的4線SPI相同,這里不在敘述。兩者的不同點在于:三線SPI模式需要FPGA管腳三態控制SDIO的輸入/輸出狀態。下圖所示的代碼即為三態控制邏輯。SDI、SDO成為了內部邏輯信號,和上篇的4線SPI配置相同操作即可,而SDIO為三態管腳,需定義為inout類型。

Tri_en信號即為三態控制信號,在寫操作中,該信號必須置高;然而在讀操作中,該信號在寫地址的前半段需置高,當完成寫地址操作后,ADC的SDIO接口由輸入變輸出,此時FPGA控制Tri_en信號拉低,將FPGA端的SDIO管腳由輸出變為輸入,從而正常接收ADC的SDIO口輸出的寄存器數值。

Tri_en到底應該在哪個具體時刻拉低,以便完成FPGA的SDIO三態轉換呢?答案其實在第三篇已經說的很清楚了~~~~

另外,3線SPI讀/寫操作有專門的讀寫標志位,大家務必要留心~~

3線SPI的FPGA實現就介紹到這里了,其實和4線基本一樣,只不過多了個三態轉換而已,大家把上篇的4線SPI的實現過程想清楚了,再加上一個三態轉換控制,3線SPI也就拿下了!

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636222 -

Verilog

+關注

關注

30文章

1374瀏覽量

114520 -

SPI

+關注

關注

17文章

1885瀏覽量

101214

原文標題:FPGA通過SPI對ADC配置簡介(五)--Verilog實現3線SPI配置

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+本書概覽與內容特點介紹

RK?平臺?SPI?開發完全指南(驅動?+?配置?+?測試?+?優化)

請問-88dBm的接收靈敏度是什么個概念?

SPI的缺點介紹

蜂鳥E203在黑金XC7A200T型FPGA上點亮LED并實現流水燈

Hbirdv2在vivado2018.3上的仿真工作

關于系統鏈接腳本的介紹

HbirdV2-SoC自帶pwm配置介紹

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

華源智信大功率PD協議芯片HY5334介紹

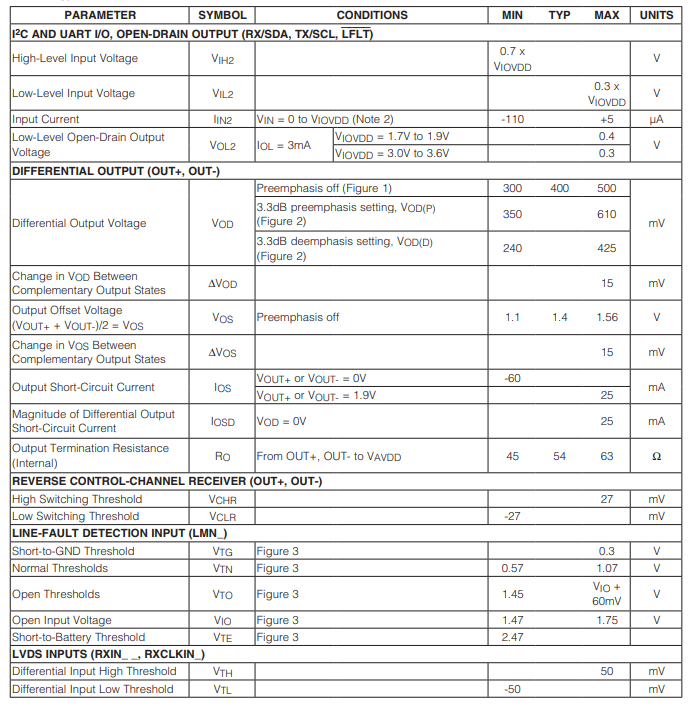

MAX9249多媒體串行鏈路串行器,帶有LVDS系統接口技術手冊

Melexis霍爾效應磁位置傳感芯片MLX90427介紹

中微愛芯微控制器AiP8F3232介紹

以AD9249介紹其3線SPI配置的verilog實現

以AD9249介紹其3線SPI配置的verilog實現

評論