本篇博文主要講解了動態更改 UltraScale/UltraScale+ GTH/GTY 收發器線速率設置的方法。

您是否曾想過要使用 UltraScale/UltraScale+ GTH/GTY 收發器來動態更改線速率設置?

有許多客戶會將 GTH/GTY 收發器用于其自己的通信協議,因此詢問我們如何才能使用收發器來更改線速率。

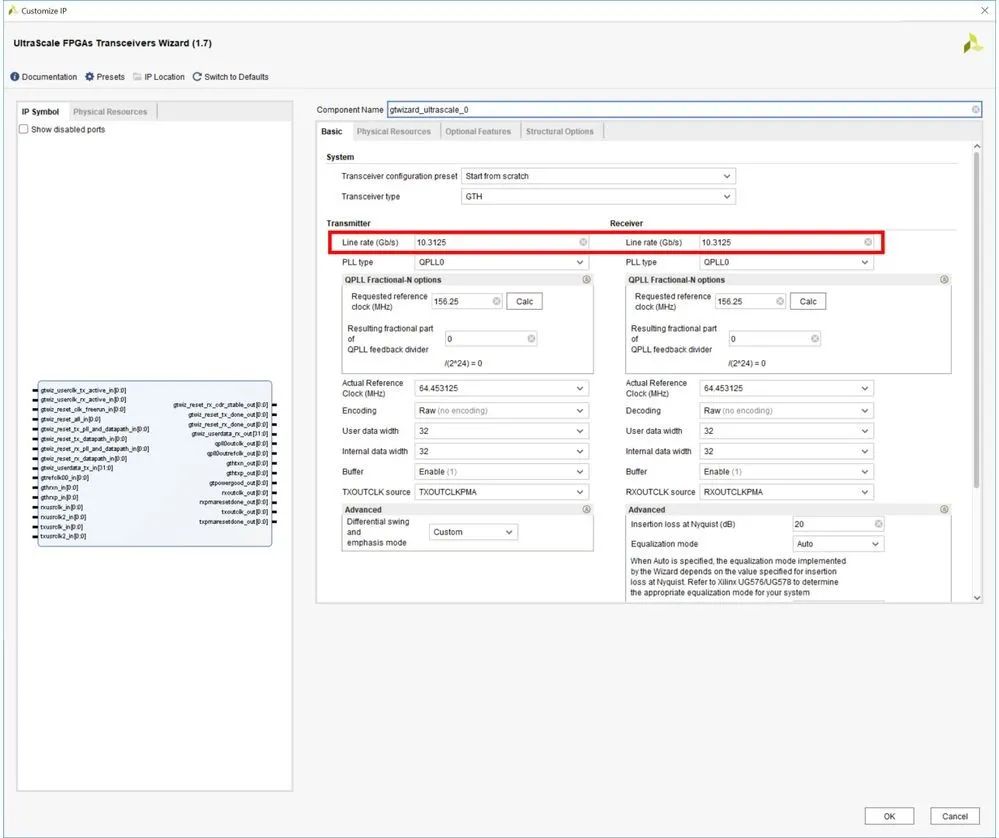

在 Vivado IP Catalog 的 UltraScale FPGAs TransceiversWizard 中僅含一項線速率設置。

由于 UltraScale/UltraScale+ GTH/GTYTransceiver Wizard 不允許更改線速率設置,因此必須由收發器用戶手動執行更改。

1.如何通過 DRP 接口更改線速率

(a) 生成收發器 IP

使用要實現的線速率配置生成收發器 IP。

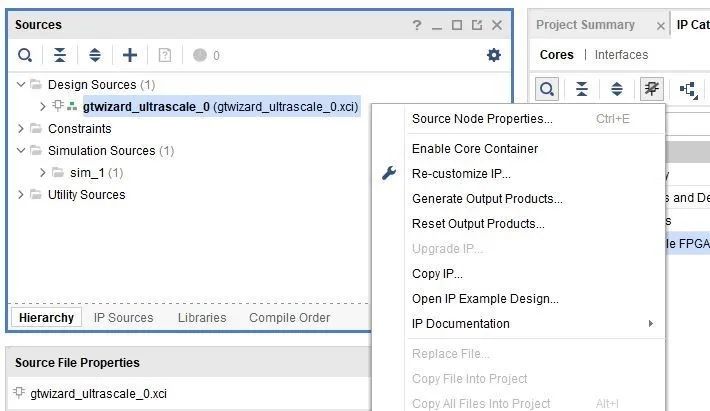

(b) 生成設計樣本

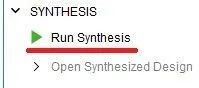

(c) 對設計樣本執行邏輯綜合

單擊 Flow Navigator 中的“運行綜合 (Run Synthesis)”:

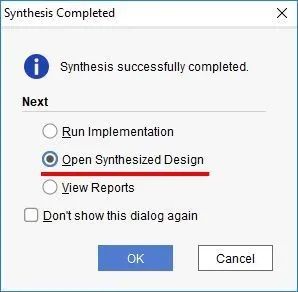

綜合完成后,選擇“打開已綜合的設計 (Open Synthesized Design)”以打開網表。

(d) 運行隨附的腳本

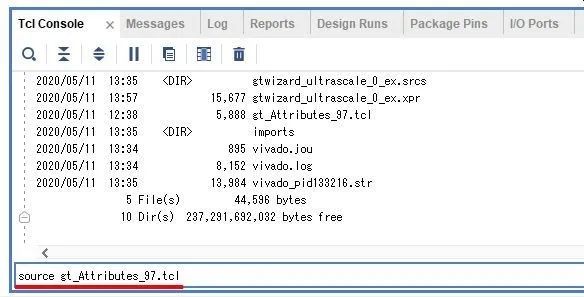

在 Tcl 控制臺 (Tcl console) 中運行gt_Attributes_97.tcl腳本:

執行此腳本即可將“Channel/Common”屬性輸出到gtParams.txt文件。

并且,GTH/GTY 中的屬性和修復后的 GTH/GTY 端口也都將包含在同一個文件中輸出,以便于您進行比較。

針對要實現的每項 GTH/GTY 配置重復上述步驟 (a) 到 (d)。

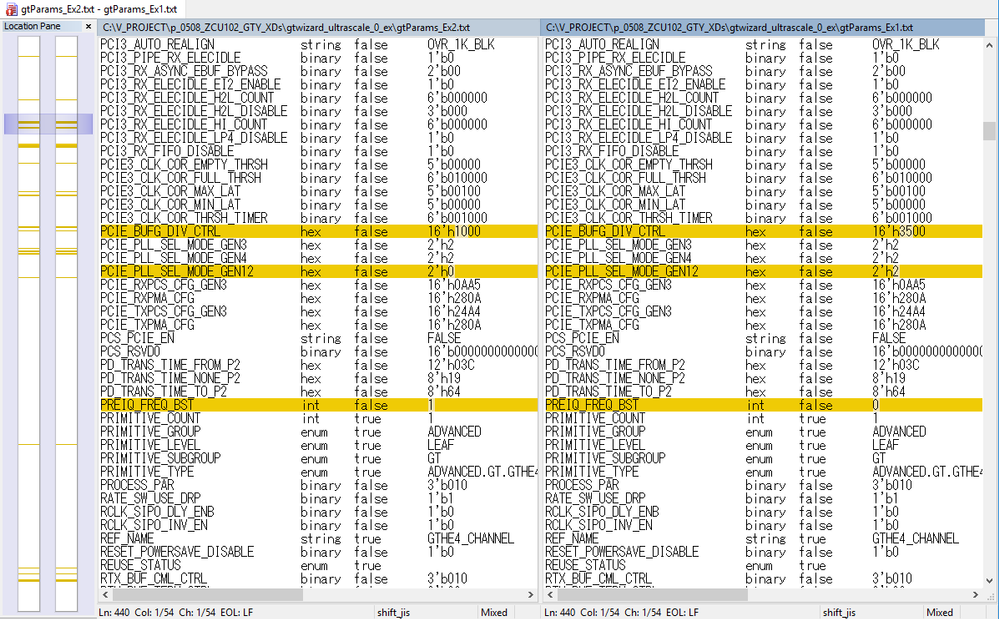

(e) 比較輸出

通過比較來自 GTH/GTY 配置的gtParams.txt輸出,即可立即查看不同的屬性。

(f) 動態重配置端口接口 (DRP I/F)

所需屬性必須通過 DRP I/F 來設置。

在 (UG576)/(UG578) 的附錄 B/C 中詳列了每個屬性的地址。

如果您不熟悉 DRP I/F,請參閱 (UG576)/(UG578) 的第 2 章,以獲取更多信息。

(g) 復位

在 DRP I/F 上設置完屬性后,必須先再次執行復位,然后才能使用 GTH/GTY。

注:建議最好使用此腳本生成gtParams.txt,然后再進行比較,而不是直接比較封裝器 RTL。

由于除 Channel 和 Common 屬性外,還可比較修復后的外部端口,因此您可放心更改這些屬性。

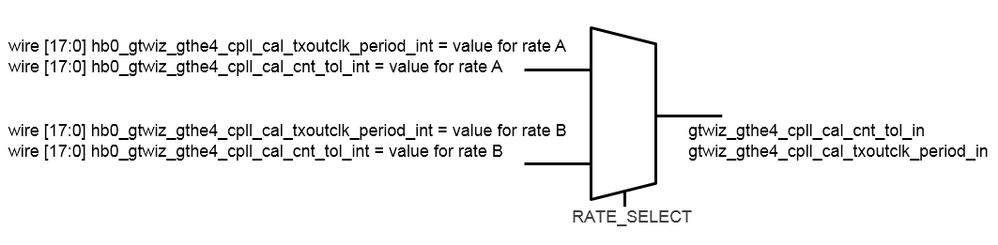

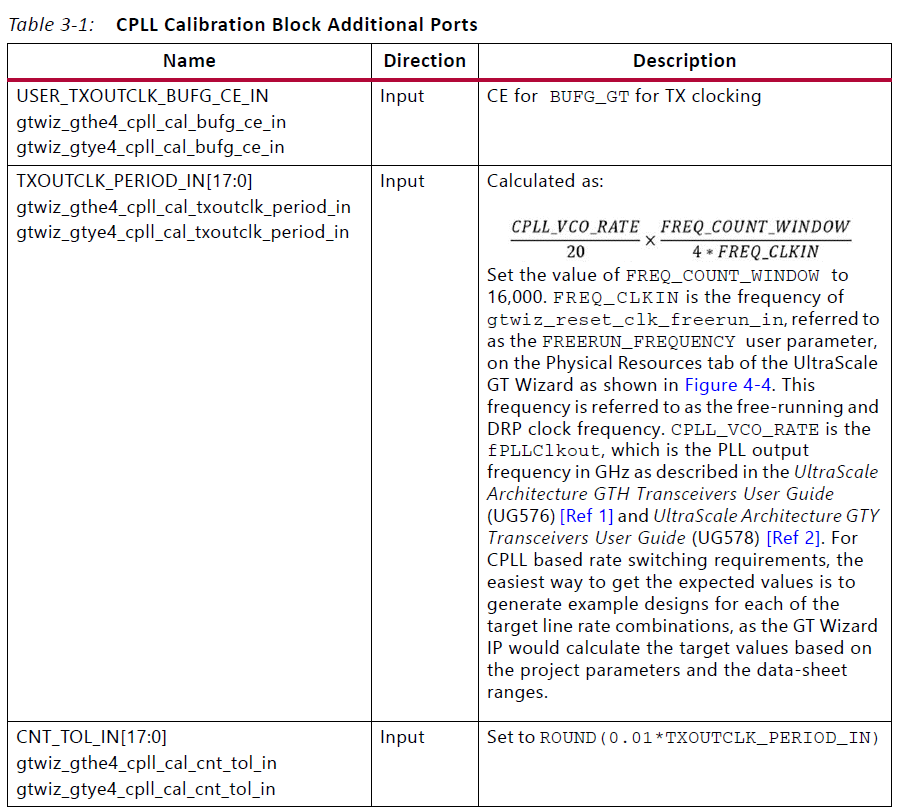

2.更改 CPLL 校準模塊的設置

如果在設計中使用了 CPLL,那么必須在 CPLL 校準模塊中更改信號。

請參閱(賽靈思答復記錄 70485),以獲取有關更改信號所需的設置更改的信息

【答復記錄70485,https://china.xilinx.com/support/answers/70485.html】

綜上,如需動態更改UltraScale/UltraScale+ GTH/GTY 的線速率,請遵循上述步驟 (1) 和 (2) 進行操作。

-

收發器

+關注

關注

10文章

3835瀏覽量

111386 -

IP

+關注

關注

5文章

1875瀏覽量

156363 -

UltraScale

+關注

關注

0文章

126瀏覽量

32397

原文標題:開發者分享 | 如何動態更改 UltraScale/UltraScale+ GTH/GTY 線速率

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

第二代AMD Kintex UltraScale+ FPGA的亮點

探索TLK3131單通道多速率收發器:特性、應用與設計要點

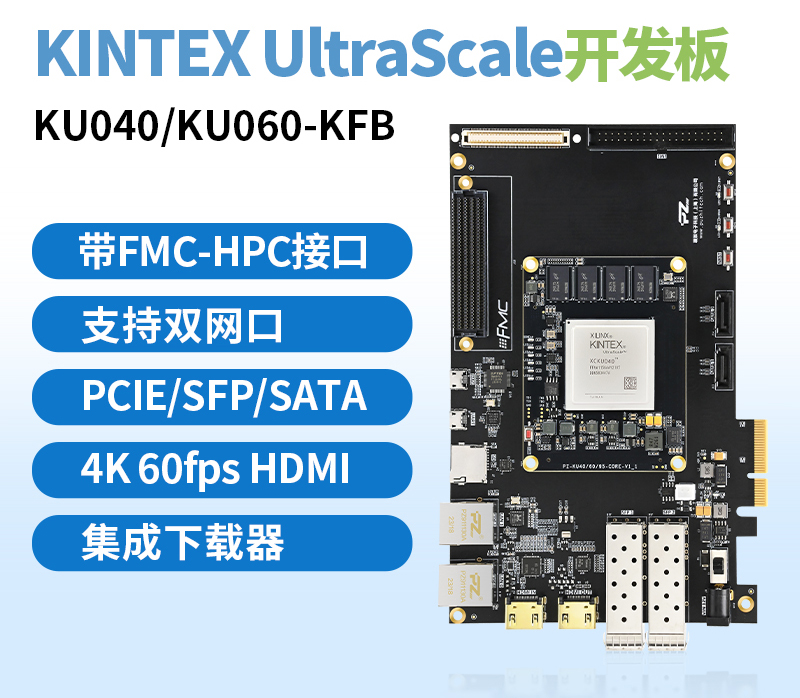

【ALINX選型】AMD Kintex UltraScale+ 系列 FPGA 開發板速選

使用Aurora 6466b協議實現AMD UltraScale+ FPGA與AMD Versal自適應SoC的對接

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

深入剖析TLK6002:高性能多速率收發器的技術詳解

深入解析TLK6002:高性能多速率收發器的技術洞察

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

現已上市:AMD Spartan UltraScale+ FPGA SCU35 評估套件——面向所有開發人員的經濟實惠平臺

AMD Spartan UltraScale+ FPGA的優勢和亮點

Kintex UltraScale 純 FPGA 開發平臺,釋放高速并行計算潛能,高性價比的 FPGA 解決方案

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

AMD FPGA異步模式與同步模式的對比

AMD Spartan UltraScale+ FPGA 開始量產出貨

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

動態更改UltraScale/UltraScale+ GTH/GTY收發器線速率設置的方法

動態更改UltraScale/UltraScale+ GTH/GTY收發器線速率設置的方法

評論