精簡指令集的特點

精簡指令集計算機RISC的特點是指令及其格式精少,操作和控制簡捷。具體有下列幾個方面。

精簡指令集

RISC結構采用精簡的,長短劃一的指令集,使大多數的操作獲得了盡可能高的效率。某些在傳統結構中要用多周期指令實現的操作,在RISC結構中,通過機器語言編程,就代之以多條單周期指令了。精簡的指令集大大改善了處理器的性能,并推動了RISC的設計。對于到底精簡到什么程度的問題,沒有一定的回答。將現有RISC系統與CISC系統作一對比,便可見大概。通常,對RISC而言:

指令數少,不超過128條。

尋址方式少,不超過4種。

指令格式少,不超過4種。

處理關于擴充指令集的建議是非常慎重的,要經過認真的權衡,驗證,在看它們是否真正提高計算機的性能。例如,MIPS采用了一條規則:增加一條指令必須使性能在一定的應用范圍內得到1%的增益,否則這條指令將被拒絕。

指令時鐘周期,指令長度相等

如果每一條指令要執行的任務既簡單又明了,則執行每一條指令所的時間可以被壓縮周期數也可減少。RISC的設計目標是實現一個機器周期執行一條指令,使得系統操作更加有效。接近這個目標的技術包括指令流水線及特定的裝/存結構等。典型的指令可包括取指、譯碼、執行和存裝果等階段。單周期指可通過讓所有指令為標準長短來實現。標準指令長短應與計算機系統的基本字長相等,通常與系統中數據線數相等。

在任何取指周期,完整的單個指令要傳給CPU。例如,如果基字長是32位,且系統總線的數據部分是32線,則標準指令長度是32位。要讓所有指令的執行時間一致較困難。有些指令,包含簡單的在CPU寄存器上的邏輯操作(清寄存器等),則可容易地在一個CPU時鐘周期內執行;其它指令可能包含內存存取(對內存的讀寫、取數等)或多周期操作(乘、除等),可能無法在單周期內執行。這給設計者提出了這樣的要求;讓大多數經常使用的指令得以在一個單周期內執行。

指令流水線

減少執行一條指令所需周期數的方法是重疊執行多條指令。指令流水線采用這樣的工作方式:將每條指令的執行分為幾個離散部分,然后同時執行多條指令。任何指令的取指和執行階段占據相同時間,理想的是一個單周期。這可說是RISC最重要的一條設計原則。所有從內存到CPU執行的指令,都遵循一種恒定的流的形式。每條指令都以同樣的步調執行,無等待的指令。CPU始終是忙的。達到流水線操作的必要條件是:

標準的,固定長短的指令,它與計算機字長和數據線的字長相等。

所有指令的標準執行時間,最好在一個單CPU周期內。

例SPARC芯片等采用了取指、譯碼、執行和寫入結果四級流水線結構,以最大限度來提高處理器性能。在每一個時鐘周期的頭上,都可以開始執行一條新的指令,這就保證了每個機器周期從存貯器平均取出一條新的指令,從而,總體看,大多數指令能在單周期內實現。指令流水線技術可以比作一條裝配線—指令象是被加工的產品一樣,從一道工序流到下一道工序,一直到它執行完為止。

因此,指令流水線利用一個等于其流水線深度的因子,來減少指令周期數是可能的,但這樣的話,要求流水線始終充滿有用指令且沒有任何東西阻礙指令通過流水線,這樣的需求給結構增加了一定的負擔。例如,對于ALU等資源的競爭,阻止了流水線中指令的流動。長短不一的執行時間所引起的不良后果更是顯而易見,這也是為什么RISC要定義一個有前面所述特點的指令集的原因。

裝入和存數(LOAD/Store)結構

執行與內存有關的操作指令,不是要求增加每個周期的時間,就是要求增加指令的周期數,二者必取其一。因為這些指令要計算操作數的地址,將所需的操作數從內存中讀出,計算得出結果,再把結果送回內存,所以它們執行的時間就長得多。為了消除這種指令的負作用,RISC采用了這樣的裝入和存數結構:只有裝入(Load)和存數(Store)指令才去訪間內存,所有其它操作只訪問保存在處理器寄存器中的操作數。其優點在于:

減少訪問內存的次數,降低了對內存帶寬的要求。

將所有的操作限制于只針對寄存器,幫助了指令集的簡化。

取消內存操作可使編釋器優化寄存的分配更容易—這種特性減少對內存的存取,同時也減少了每一任務的指令數。

所有這些都有助于RISC實現的每個周期執行一條指令的目標。盡管如此,裝入和存數指令仍阻礙著IRSC設計目標的實現。用優化編譯技術處理裝入指令和分支指令的延遲,有助問題的解決。優化編譯技術雖不是專門面向RISC結構的,但優化編譯器依賴于RISC結構完成其出色的任務,RISC結構又依賴于優化編譯器得到它們更完善的性能。編釋器要能分析數據和控制流,并在此基礎上調整指令的執行順序,巧妙安排寄存器的用法。前一種作用可減少CPU的空閑時間,后一種作用可以提高寄存器中所保存的數據的可再用率,減少訪存次數,縮短數據通路的長度。

擁有較大寄存器組

為了便于實現多數指令在寄存器之間的操作,即所謂的寄存器到寄存器操作,必須有足夠量的CPU通用寄存器。足量的寄存器使得在隨后操作中需作為操作用的中間結果暫存在CPU寄存器中,因而就減少了對內存的裝入和存數,加快了運行速度。工業化RISC系統中至少采用32個通用CPU寄存器。

采用硬連線控制

由于微程序設計給設計者提供的靈活性,許多CISC系統是微程序控制的。不同的指令通常具有不同長度的微程序,這意味著每條指令執行的周期數不一樣,這與所有指令一致的、流線的處理原則相矛盾。但這可由硬連線控制來解決,而且速度會更快。因此RISC應該是硬連接線控制的。當每條指令與一單條微指令有一對一相相符合的關系時可有例外,也就是每個微程序由一單個控制字組成。這種設計可與用硬連線控制一樣快,一樣高效,并使設計者得益于微程序設計的優越性。采用硬連線控制,可使RISC系統控制器簡單。設計的簡單又使機器的布局更加合理,使得設計者可以集中精力去優化那些剩下的,為數不多的,但又很關鍵的處理器特性。簡化的結構使芯片上面積資源緊張的狀態得以緩解,一些對性能至關重要的結構,象大的寄存器元件,轉換查找緩存(TLB)S協處理器和乘除單元都可以裝在同一塊芯片上。這些附加的資源又使處理器增加了很大的性能優勢。事實上,RISC并非一定嚴格地完全具備上述特點,有些稱作RISC型的系統甚至違背了上述某方面。上述特點應被當作一種指導原則來解釋RISC的性質。放寬點講,滿足大部分這些特點的系統就能被看作RISC。

精簡指令集有哪些指令

精簡指令集 精簡指令集,計算機CPU的一種設計模式,也被稱為RISC(Reduced Instruction Set Computing 的縮寫)。常見的精簡指令集微處理器包括AVR、PIC、ARM、DEC Alpha、PA-RISC、SPARC、MIPS、Power架構等。早期,這種CPU指令集的特點是指令數目少,每條指令都采用標準字長、執行時間短、CPU的實現細節對于機器級程序是可見的等等。

-

RISC

+關注

關注

6文章

485瀏覽量

86598 -

精簡指令集

+關注

關注

0文章

4瀏覽量

2544

發布評論請先 登錄

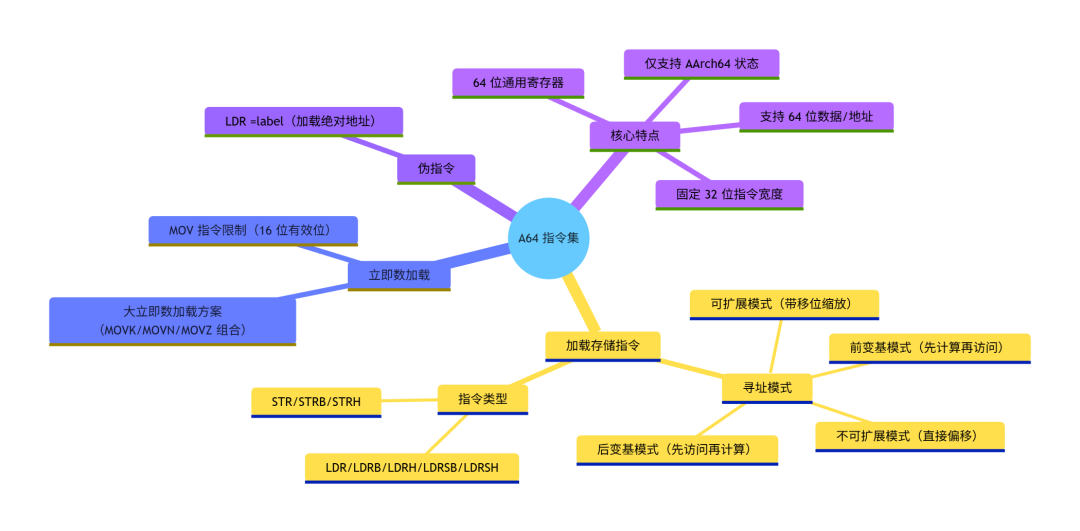

A64指令集通關筆記:加載與存儲指令全解析

【「龍芯之光 自主可控處理器設計解析」閱讀體驗】+本書概覽與龍芯指令集基礎了解.docx

指令集測試的一種糾錯方法

蜂鳥E203的浮點指令集拓展(F拓展)

Vector向量指令集簡介(一)

risc-v P擴展(一) P指令集簡介

RISCV-K指令集擴展分享

RVB 位操作指令集擴展(一)

RVF單精度浮點指令集擴展介紹(2)

RVF單精度浮點指令集擴展介紹(1)

基于蜂鳥E203架構的指令集K擴展

RISC-V和ARM有何區別?

精簡指令集的特點_精簡指令集有哪些指令

精簡指令集的特點_精簡指令集有哪些指令

評論