5月14日, Cadence宣布基于中芯國際14nm工藝的10Gbps多協議PHY研發成功,這是行業首個SMIC FinFET工藝上有成功測試芯片的多協議SerDes PHY IP。

據介紹,該多協議SerDes PHY IP具有很強的靈活性,在保證PPA不損失的情況下對設計進行了簡化。它采用了Cadence經過大量量產驗證的Torrent架構,可以有效的幫助客戶降低產品風險,縮短產品上市時間。

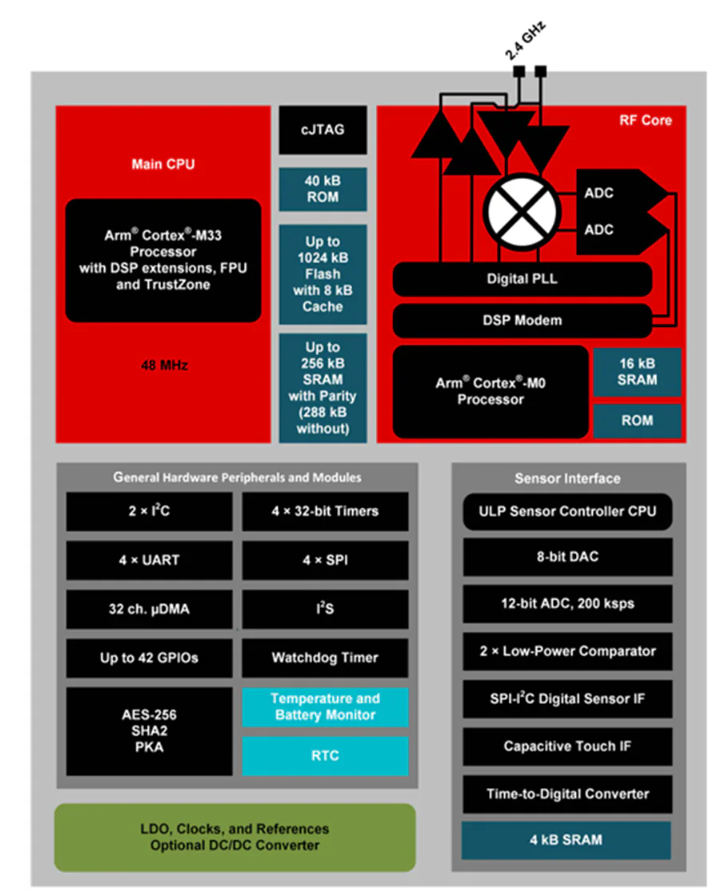

圖 1 測試芯片和實際運用場景模擬演示

這個PHY IP可以在單個macro上運行多種協議,支持從 1Gbps 到 10.3125Gbps的連續速率,適用于PCIe (Gen 1/2/3),USB 3.1 (Gen1/2),Display Port Tx v1.4,Embedded DisplayPort Tx v1.4b,JESD204b(max 10.3215Gbps),10GBase-R,XFI,SFP+,RXAUI,XAUI,QSGMII/SGMII,以及 SATA 3 (Gen 1/2/3) 等協議。PCS支持PIPE 4.2接口。

Cadence多協議SerDes PHY IP的主要特性包括,獨立鏈路的多協議支持、支持PCIe L1 sub-states、片上終端電阻自動校準、支持SRIS和內部SSC生成、支持多達16 通道(lanes)、支持分叉模式(bifurcation)、支持內外部時鐘源動態檢測、SCAN,BIST,串/并行環回功能。

這個多協議SerDes PHY IP可以快速、輕松地集成到SoC系統中,可以與Cadence 或第三方PIPE兼容的控制器進行無縫對接。多協議SerDes PHY IP為高要求運用的客戶提供了一個低成本、多功能、低功耗的解決方案。不僅為SoC集成商提供卓越的性能與靈活性,同時能夠滿足高性能的設計要求。

除了10G多協議 SerDesPHY IP,Cadence 在2019年9月還發布了SMIC14nm工藝的DDR PHY IP,它采用SMIC自有標準庫單元,支持DDR3/4/LPDDR3/4/X協議,最高速度可達4266Mbps。SMIC14nm DDR PHY IP 已經通過了各項功能和性能的驗證,并且已經運用在多個客戶的產品設計上。

Cadence表示,未來還會推出更多SMIC先進工藝的IP,以滿足客戶多樣化的需求。

責任編輯:gt

-

芯片

+關注

關注

463文章

54010瀏覽量

465978 -

控制器

+關注

關注

114文章

17788瀏覽量

193113 -

多協議

+關注

關注

0文章

34瀏覽量

10660 -

PCB打樣

+關注

關注

17文章

2981瀏覽量

23592 -

可制造性設計

+關注

關注

10文章

2066瀏覽量

16457 -

可制造性設計分析

+關注

關注

4文章

866瀏覽量

6336

發布評論請先 登錄

威鋒電子攜全新工業級 USB 5/10Gbps集線器產品,亮相 Embedded World 2026

PL27A1 超高速USB3.0主機到主機橋接控制器技術手冊

TLK10081:10Gbps 1 - 8 通道多速率串行鏈路聚合器的深度解析

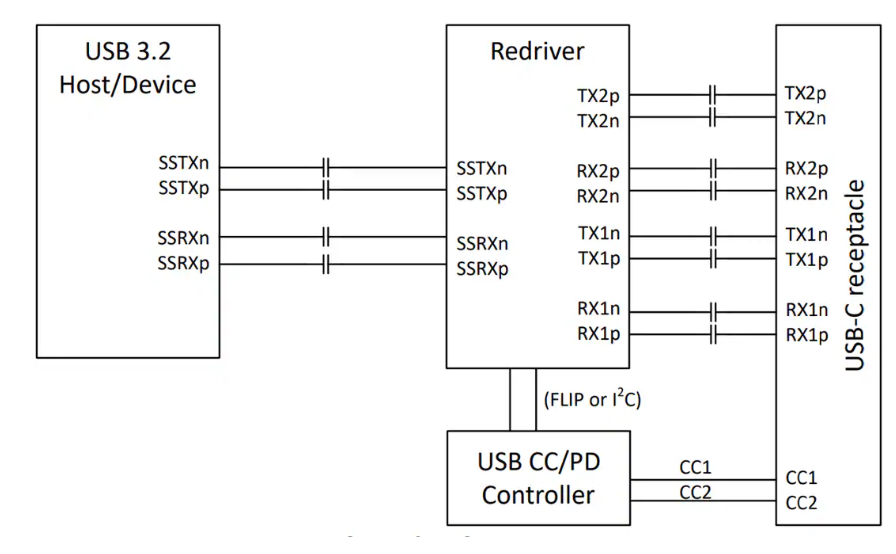

TUSB1002:USB3.1 10Gbps 雙通道線性轉接驅動器深度解析

TUSB1004 USB 3.2 10Gbps 四通道自適應線性轉接驅動器:設計與應用全解析

TUSB1044A:USB Type-C 10Gbps 多協議雙向線性轉接驅動器解析

應用案例分享:西門子ATEC控制器BACnet MSTP轉MQTT對接平臺鋇錸技術BA113網關

CC2674R10無線微控制器技術解析:高性能多協議2.4GHz解決方案

?TUSB1044 USB Type-C? 10Gbps多協議雙向線性重驅動器芯片總結

如何測試協議分析儀的實時響應效率?

協議分析儀需要支持哪些常見協議?

Texas Instruments TUSB1021-Q1 10Gbps線性轉接驅動器多路復用器和多路解復用器數據手冊

Cadence的10Gbps多協議PHY研發成功,可與控制器進行無縫對接

Cadence的10Gbps多協議PHY研發成功,可與控制器進行無縫對接

評論