(文章來源:網絡整理)

我們經常看到報道上說芯片制程達到了14nm、7nm、5nm,最近中芯國際在沒有ASML的EUV光刻機的情況下,實現了7nm的制程,有很多人對此感到很興奮。同時也有人問,半導體的多少納米制程,到底是指晶體管間距多少納米,還是晶體管的大小是多少納米?要回答這個問題,我們得從一個晶體管單位的組成說起。

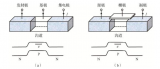

晶體管工作的時候,電流從源極(Source)流入漏極(Drain),中間綠色的那堵墻叫作柵極(Gate),相當于一個閘門,它負責控制源極和漏極之間電流的通斷。而電流通過柵極(Gate)時會損耗,柵極的寬度就決定了損耗的大小。表現在芯片上,就是芯片的發熱和功耗,柵極越窄,芯片的功耗就越小。

柵極的最小寬度(柵長,就是上面右圖Gate的寬度)就是多少nm工藝中的數值了。在實際芯片制程工藝中,越小的制程工藝,不但對制造工藝和設備有更高的要求,其芯片性能也會受到極大的影響。當寬度逼近20nm的時候,柵極對電流的控制能力就會急劇下降,從而發生“漏電”的問題。

漏電會導致芯片的功耗上升,更會使電路發生錯誤,信號模糊。為了解決信號模糊的問題,芯片又不得不提高核心電壓,使得功耗更大。這對于更小工藝制程來說,是一個矛盾。

為了解決這個問題,臺積電和三星等芯片制造企業,提出了FinFET工藝。這種工藝,簡單來說,就是將芯片內部平面的結構,變成了立體的,把柵極形狀改制,增大接觸面積,減少柵極寬度的同時降低漏電率,而晶體管空間利用率大大增加。

FinFET(鰭式場效應晶體管),是一種新型的晶體管,這種被稱為CMOS的工藝優勢很明顯,很快就被大規模應用于手機芯片上。

然而,在5nm以下的制程芯片中,影響芯片性能的除了漏電問題之外,更大的是量子效應的影響,這時芯片的特性更難控制,科學家們要尋求新工藝才能使芯片更進一步。

業內正在發展的一種新技術叫做環繞式柵極技術(Gate-All-Around),簡稱為GAA橫向晶體管技術(GAAFET)。這項技術的特點是實現了柵極對溝道的四面包裹,源極和漏極不再和基底接觸,而是利用線狀(可以理解為棍狀)或者平板狀、片狀等多個源極和漏極橫向垂直于柵極分布后,實現MOSFET的基本結構和功能。

(責任編輯:fqj)

-

芯片

+關注

關注

463文章

54010瀏覽量

466151 -

晶體管

+關注

關注

78文章

10396瀏覽量

147772

發布評論請先 登錄

揭秘芯片測試:如何驗證數十億個晶體管

MUN5136數字晶體管技術解析與應用指南

電壓選擇晶體管應用電路第二期

晶體管的定義,晶體管測量參數和參數測量儀器

晶體管的基本結構和發展歷程

0.45-6.0 GHz 低噪聲晶體管 skyworksinc

多值電場型電壓選擇晶體管結構

晶體管光耦的工作原理

無結場效應晶體管詳解

芯片7納米制程指的是晶體管間距還是晶體管大小7納米

芯片7納米制程指的是晶體管間距還是晶體管大小7納米

評論