(文章來源:網絡整理)

如今隨著芯片制程的不斷提升,芯片中可以有100多億個晶體管,如此之多的晶體管,究竟是如何安上去的呢?

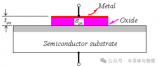

Mos管在芯片中放大可以看到像一個“講臺”的三維結構,晶體管是沒有電感、電阻這些容易產生熱量的器件的。最上面的一層是一個低電阻的電極,通過絕緣體與下面的平臺隔開,它一般是采用了P型或N型的多晶硅用作柵極的原材料,下面的絕緣體就是二氧化硅。平臺的兩側通過加入雜質就是源極和漏極,它們的位置可以互換,兩者之間的距離就是溝道,就是這個距離決定了芯片的特性。

當然,芯片中的晶體管不僅僅只有Mos管這一種類,還有三柵極晶體管等,晶體管不是安裝上去的,而是在芯片制造的時候雕刻上去的。在進行芯片設計的時候,芯片設計師就會利用EDA工具,對芯片進行布局規劃,然后走線、布線。如果我們將設計的門電路放大,白色的點就是襯底, 還有一些綠色的邊框就是摻雜層。晶圓代工廠就是根據芯片設計師設計好的物理版圖進行制造。

芯片制造的兩個趨勢,一個是晶圓越來越大,這樣就可以切割出更多的芯片,節省效率,另外就一個就是芯片制程,制程這個概念,其實就是柵極的大小,也可以稱為柵長,在晶體管結構中,電流從Source流入Drain,柵極(Gate)相當于閘門,主要負責控制兩端源極和漏級的通斷。

電流會損耗,而柵極的寬度則決定了電流通過時的損耗,表現出來就是手機常見的發熱和功耗,寬度越窄,功耗越低。而柵極的最小寬度(柵長),也就是制程。縮小納米制程的用意,就是可以在更小的芯片中塞入更多的電晶體,讓芯片不會因技術提升而變得更大。

但是我們如果將柵極變更小,源極和漏極之間流過的電流就會越快,工藝難度會更大。芯片制造過程共分為七大生產區域,分別是擴散、光刻、刻蝕、離子注入、薄膜生長、拋光、金屬化,光刻和刻蝕是其中最為核心的兩個步驟。

而晶體管就是通過光刻和蝕刻雕刻出來的,光刻就是把芯片制作所需要的線路與功能區做出來。利用光刻機發出的光通過具有圖形的光罩對涂有光刻膠的薄片曝光,光刻膠見光后會發生性質變化,從而使光罩上得圖形復印到薄片上,從而使薄片具有電子線路圖的作用。這就是光刻的作用,類似照相機照相。照相機拍攝的照片是印在底片上,而光刻刻的不是照片,而是電路圖和其他電子元件。

刻蝕是使用化學或者物理方法有選擇地從硅片表面去除不需要材料的過程。通常的晶圓加工流程中,刻蝕工藝位于光刻工藝之后,有圖形的光刻膠層在刻蝕中不會受到腐蝕源的顯著侵蝕,從而完成圖形轉移的工藝步驟。刻蝕環節是復制掩膜圖案的關鍵步驟.

而其中,還涉及到的材料就是光刻膠,我們要知道電路設計圖首先通過激光寫在光掩模板上,然后光源通過掩模板照射到附有光刻膠的硅片表面,引起曝光區域的光刻膠發生化學效應,再通過顯影技術溶解去除曝光區域或未曝光區域,使掩模板上的電路圖轉移到光刻膠上,最后利用刻蝕技術將圖形轉移到硅片上。

而光刻根據所采用正膠與負膠之分,劃分為正性光刻和負性光刻兩種基本工藝。 在正性光刻中,正膠的曝光部分結構被破壞,被溶劑洗掉,使得光刻膠上的圖形與掩模版上圖形相同。相反地,在負性光刻中,負膠的曝光部分會因硬化變得不可溶解,掩模部分則會被溶劑洗掉,使得光刻膠上的圖形與掩模版上圖形相反。我們可以簡單地從微觀上講解這個步驟。

在涂滿光刻膠的晶圓(或者叫硅片)上蓋上事先做好的光刻板,然后用紫外線隔著光刻板對晶圓進行一定時間的照射。原理就是利用紫外線使部分光刻膠變質,易于腐蝕。溶解光刻膠:光刻過程中曝光在紫外線下的光刻膠被溶解掉,清除后留下的圖案和掩模上的一致。

“刻蝕”是光刻后,用腐蝕液將變質的那部分光刻膠腐蝕掉(正膠),晶圓表面就顯出半導體器件及其連接的圖形。然后用另一種腐蝕液對晶圓腐蝕,形成半導體器件及其電路。清除光刻膠:蝕刻完成后,光刻膠的使命宣告完成,全部清除后就可以看到設計好的電路圖案。而100多億個晶體管就是通過這樣的方式雕刻出來的,晶體管可用于各種各樣的數字和模擬功能,包括放大,開關,穩壓,信號調制和振蕩器。

晶體管越多就可以增加處理器的運算效率;再者,減少體積也可以降低耗電量;最后,芯片體積縮小后,更容易塞入行動裝置中,滿足未來輕薄化的需求。到了3nm之后,目前的晶體管已經不再適用,目前,半導體行業正在研發nanosheet FET(GAA FET)和nanowire FET(MBCFET),它們被認為是當今finFET的前進之路。

三星押注的是GAA環繞柵極晶體管技術,臺積電目前還沒有公布其具體工藝細節。三星在2019年搶先公布了GAA環繞柵極晶體管,根據三星官方的說法,基于全新的GAA晶體管結構,三星通過使用納米片設備制造出MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,取代FinFET晶體管技術。此外,MBCFET技術還能兼容現有的FinFET制造工藝的技術及設備,從而加速工藝開發及生產。

(責任編輯:fqj)

-

芯片

+關注

關注

463文章

54010瀏覽量

465978 -

晶體管

+關注

關注

78文章

10396瀏覽量

147733

發布評論請先 登錄

揭秘芯片測試:如何驗證數十億個晶體管

探索 onsemi NST1602CL 雙極晶體管:高性能與可靠性的完美結合

基于偏置電阻晶體管(BRT)的數字晶體管系列MUN2231等產品解析

深入解析 onsemi BCP56M 通用晶體管:特性、參數與應用考量

NSVT5551M雙極晶體管技術深度解析與應用指南

MUN5136數字晶體管技術解析與應用指南

多值電場型電壓選擇晶體管結構

晶體管光耦的工作原理

下一代高速芯片晶體管解制造問題解決了!

無結場效應晶體管詳解

詳細解析芯片里的眾多晶體管是如何實現的

詳細解析芯片里的眾多晶體管是如何實現的

評論