捷捷微電的此項發明提供的快速軟恢復二極管芯片的制造方法,成本低,工藝簡單可靠,也更易于形成局域少子壽命控制區。

集微網消息,捷捷微電自1995年創辦以來,歷經了25年的發展,漸漸成長為國內專門從事功率半導體器件的龍頭企業。近年來,捷捷微電的營業收入和凈利潤保持持續增長,領先同業其他公司。同時,捷捷微電的產品正在逐步實現以國產替代進口,降低中國晶閘管、二極管等器件市場對進口的依賴。

現代電力電子技術廣泛使用IGBT、功率MOSFET等開關器件,對與之配套使用的快恢復二極管提出了更高的要求,不僅要求其反向阻斷電壓高、正向瞬態壓降小、反向恢復時間短,還要求其具有軟恢復特性,對具備這種特性的快恢復二極管稱為快速軟恢復二極管(Fast Soft Recovery Diode,簡稱FSRD)。

目前的制造工藝中,更多的是采用局部壽命控制與發射極注入效率相結合的方法,在載流子壽命控制方面,雖然人們也做出了大量的研究工作,但無外乎采用重金屬摻雜、電子、質子輻照中的一種或幾種組合的方法。這些方法需要很高能量的離子注入機設備或者高能粒子加速器設備,由于設備的造價太高,造成產品成本極大的提升,生產的工藝難度也極大。

為了解決上述問題,捷捷微電申請了一項名為“一種快速軟恢復二極管芯片的制造方法”(申請號:201711095076.7)的發明專利,申請人為江蘇捷捷微電子股份有限公司。

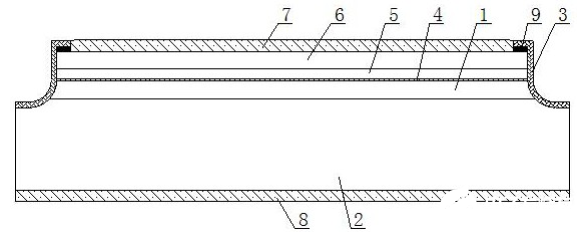

圖1 FSRD芯片的結構示意圖

上圖是該專利提出的快速軟恢復二極管芯片的結構示意圖。為了制造此FSRD芯片,需要執行以下幾個步驟:

首先,我們選用電阻率在15~150Ω·cm 之間的N-型硅單晶片1作為原材料,通過三氯氧磷擴散源,對其正面和背面實施高濃度磷予沉積擴散。經過2.5~10h的高溫處理后,可以得到N+予沉積層。繼續在高溫中進行高達100~240h的推結擴散,這樣就會形成深度為100~220μm的N+型襯底層2。

然后我們采用機械磨削方式,去除正面的N+型襯底層2,同時通過磨削量控制N-型硅單晶片1的厚度為50~130μm。接著再對N-型硅單晶片1的正面實施化學機械拋光,并通過拋光量來控制N-型硅單晶片1的剩余厚度為20~100μm,這樣就能得到拋光基片。

在拋光基片的拋光面上外延生長N-型外延層5,其厚度為15~40μm。這里需要注意的一點是,在N-型外延層5初始生長0 .5~3μm的厚度時,其摻雜濃度為N-型硅單晶片1雜質濃度的2~5倍,形成一個摻雜高峰,以達到較好的損傷效果,然后降低摻雜濃度至N-型硅單晶片1雜質濃度的0 .8~1 .25倍繼續外延生長到規定厚度,得到由N-型外延層5、N-型硅單晶片1和N+型襯底層2構成的雙基區硅片,并在N-型外延層5初始生長部分與N-型硅單晶片1之間形成的損傷層作為局域少子壽命控制區4。

接下來,在雙基區硅片的正面擴散形成P型發射區6, 并在P型發射區6的正面濺射0 .2~0 .5μm厚的鉑或金,經過一小時的退火處理后,會形成合金層。然后進行重金屬擴散,使鉑或金沉積在局域少子壽命控制區4內,并用腐蝕法除去多余的鉑或金。

然后在生成的氧化硅膜9中,用光刻法蝕刻出溝槽。再采用混酸對溝槽進行腐蝕,形成臺面,之后經過燒結鈍化,得到鈍化膜3。通過光刻可以得到蒸鍍鋁所需的窗口,再對其進行反刻以生成陽極金屬膜7。同時,在N+型襯底層2的背面蒸鍍Ti-Ni-Ag,形成陰極金屬膜8。最后再經過真空合金,即可得到圖1所示的FSRD芯片結構。

捷捷微電此項發明提供了一種快速軟恢復二極管芯片的制造方法,該制造方法成本低,工藝簡單可靠,也更易于形成局域少子壽命控制區。此外,捷捷微電的產品已出口至韓國、日本、西班牙等國家和地區,公司的中高端產品實現替代進口及對外出口上升的趨勢,打破了中國電子元器件領域受遏于國外技術制約局面。

-

芯片

+關注

關注

463文章

54010瀏覽量

466181 -

二極管

+關注

關注

149文章

10410瀏覽量

178474

發布評論請先 登錄

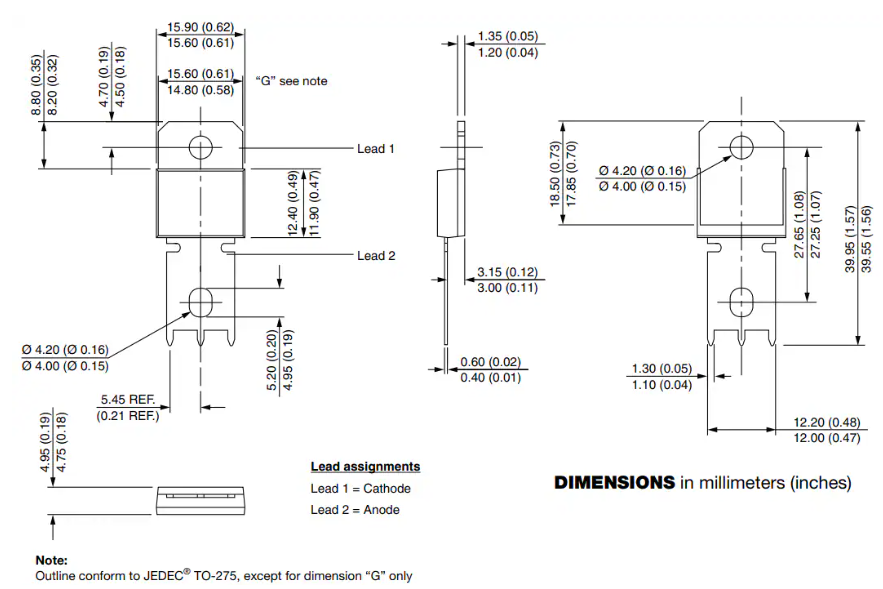

高性能快速恢復二極管DPF120C600HB的特性與應用解析

超快軟恢復二極管VS-EBU15006HN4技術深度解析

淺談二極管的反向恢復時間

在薄膜框架上提供的 PIN 二極管芯片 skyworksinc

硅肖特基二極管芯片 skyworksinc

Silicon PIN 二極管、封裝和可鍵合芯片 skyworksinc

Hyperabrupt Junction Tuning 變容二極管芯片 skyworksinc

硅限幅器二極管、封裝和可鍵合芯片 skyworksinc

芯片揭秘采訪 | 歷經30年的IDM—捷捷微電,是如何建立起防卷壁壘的?

PI超快速Qspeed H系列二極管可替代碳化硅元件

MDD快恢復二極管在開關電源中的應用:如何提高轉換效率?

揭秘捷捷微電可快速軟恢復二極管芯片的專利

揭秘捷捷微電可快速軟恢復二極管芯片的專利

評論