PCIe無疑是最為流行的傳輸總線標準,這幾年的更新換代也十分頻繁:PCIe 3.0目前還是最普及的,PCIe 4.0正在快速崛起,PCIe 5.0即將和大家見面,PCIe 6.0也正在快速推進制定中。

PCI-SIG組織今天宣布,PCIe 6.0規范已經完成了0.5版本,并提供給組織成員,將在明年按期發布最終正式版。

PCIe每版規范的制定都要經歷五個不同版本/階段:

0.3版本:初步概念,提出新規范的關鍵特性和架構。

0.5版本:初始草案規范,確定新架構的所有層面,并吸收0.3版本基礎上組織成員的反饋意見,并加入成員需求的新特性加的新特性。

0.7版本:完成版草案,新規范的方方面面都完全確定,電氣規范也必須通過測試芯片完成驗證。之后不會再加入新功能。

0.9版本:最終版草案,組織成員可以據此設計、開發自己的技術和產品。

1.0版本:最終正式版,公開發布。

事實上,0.5版本發布之后,廠商們已經可以開始設計測試芯片,為后續工作提前做好準備。

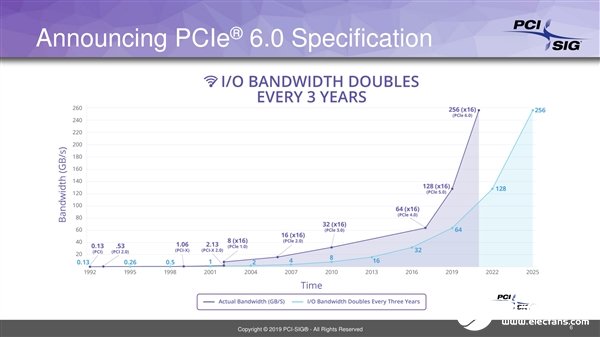

盡管升級速度加快,但是每一代PCIe規范的變化都相當大,尤其是帶寬每次都翻一番,并兼容所有前代規范。

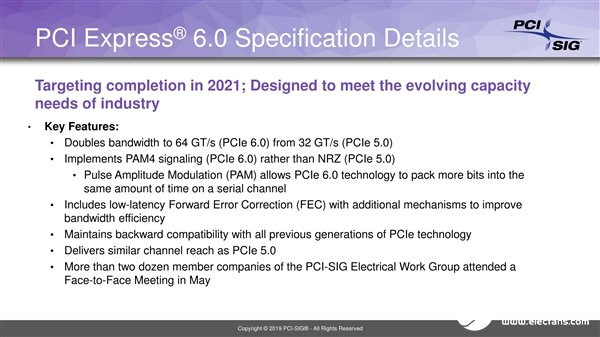

PCIe 6.0也不例外,向下兼容PCIe 5.0/4.0/3.0/2.0/1.0的同時,數據率或者說I/O帶寬會再次加倍來到64GT/s,PCIe 6.0 x1單向實際帶寬8GB/s,PCIe 6.0 x16單向帶寬128GB/s、雙向帶寬256GB/s。

PCIe 6.0將延續PCIe 3.0時代引入的128b/130b編碼方式,但加入全新的脈沖幅度調制PAM4,取代PCIe 5.0 NRZ,可以在單個通道、同樣時間內封包更多數據,以及低延遲前向糾錯(FEC)和相關機制,以改進帶寬效率。

今年的PCI-SIG開發者大會將于6月初舉行,屆時會有超過25家組織成員對PCIe 6.0規范進行面對面討論,更多細節也會對外公布。

大家可能會感到疑惑:PCIe規范更新換代如此迅速,我該買哪個版本的產品最好?是不是現在入手PCIe 4.0的很快就會過時呢?

其實大可不必有此擔憂,因為任何科技都是在不斷發展演進的,永遠都會有更好的出現,自己有需要的時候就上,“等等黨”是沒有盡頭的……

責任編輯:wv

-

PCIe

+關注

關注

16文章

1461瀏覽量

88428

發布評論請先 登錄

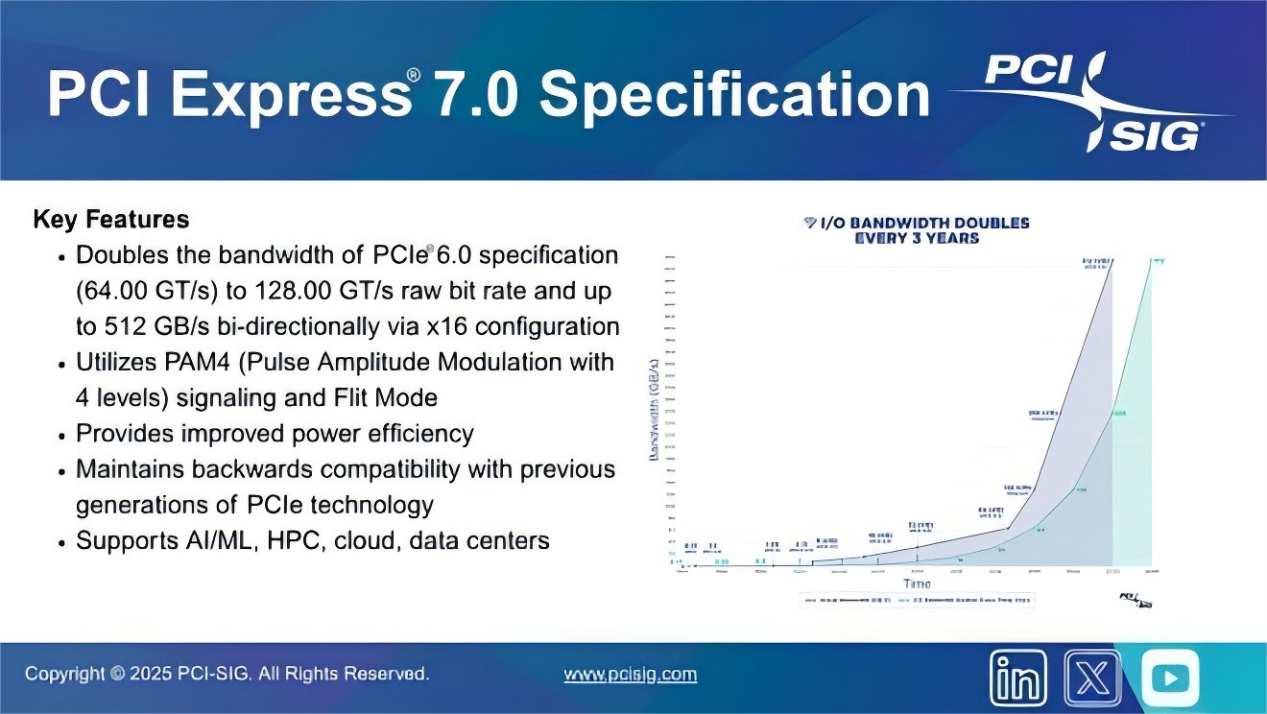

PCIe 7.0發布:16通道雙向512GB/s,擁抱光纖未來

羅德與施瓦茨矢量網絡分析儀PCB插損和阻抗測試方案

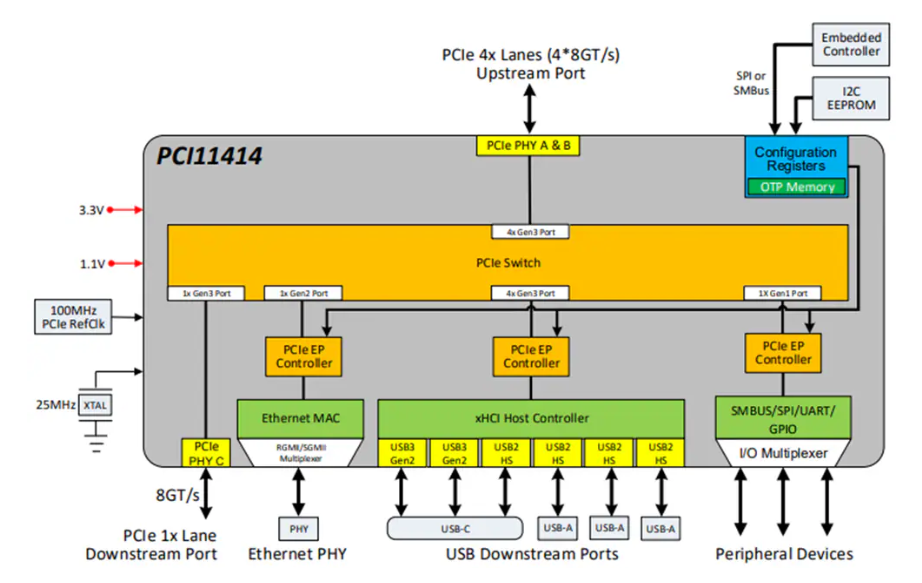

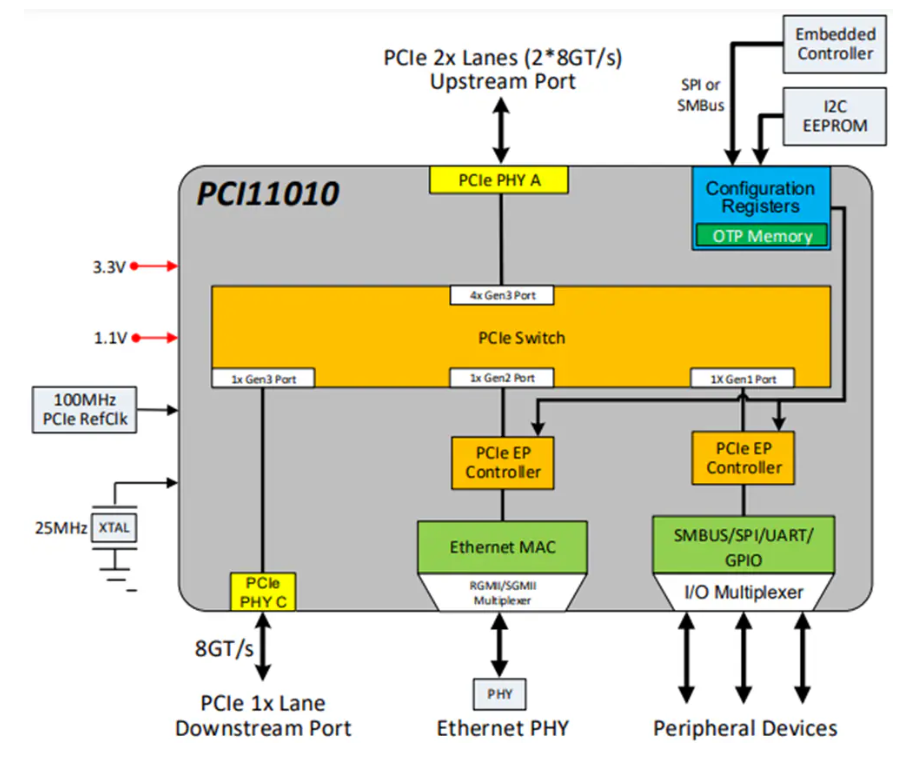

PCI11414 PCIe交換機技術解析與應用設計指南

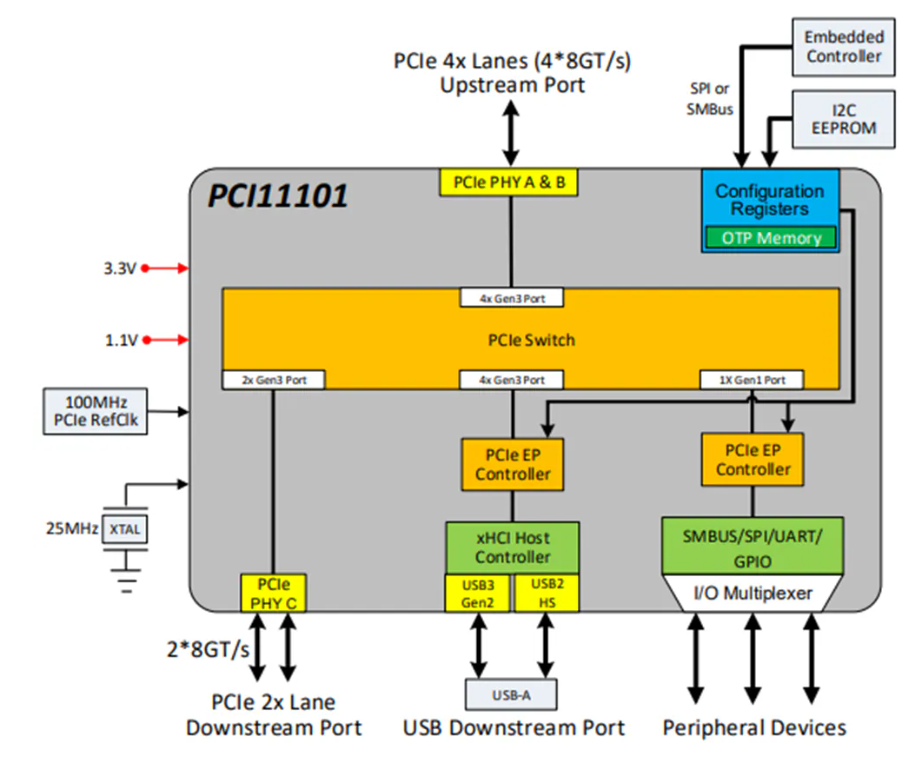

PCI11101 PCIe交換機集成USB3.2主機控制器技術解析

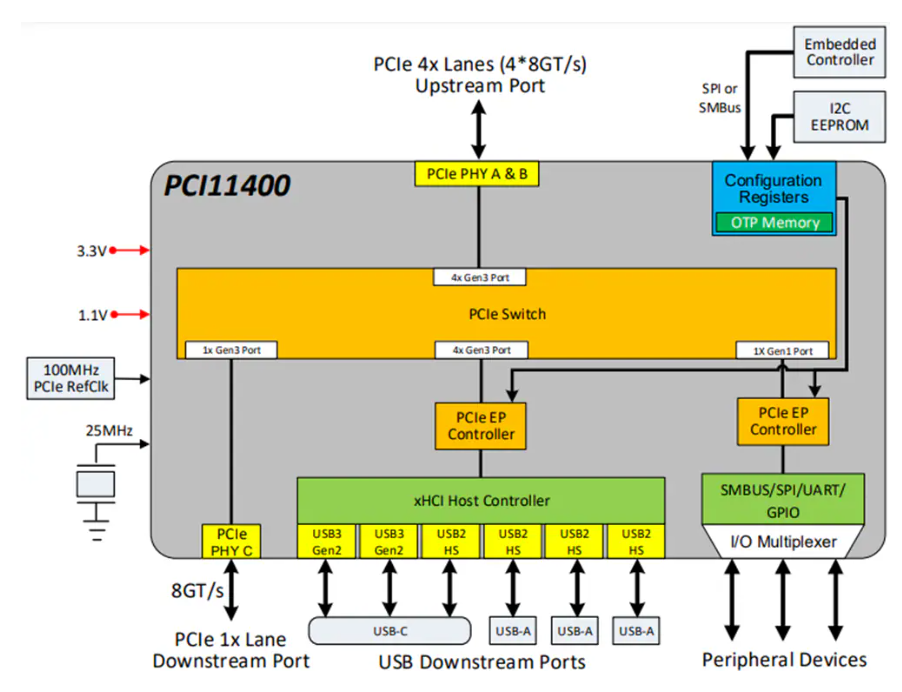

?Microchip PCI11400 PCIe交換機技術解析與應用指南

PCIe 7.0 Samtec已為您準備好N種互連解決方案

PCIe 8.0 規范公布:1TB/s 帶寬、256GT/s 速率

PCIe協議分析儀在數據中心中有何作用?

PCB插損和阻抗測試方案

Diodes公司PCIe 6.0時鐘緩沖器介紹

PCIe 6.0將于明年發布最終正式版 I/O帶寬再次加倍來到64GT/s

PCIe 6.0將于明年發布最終正式版 I/O帶寬再次加倍來到64GT/s

評論