電氣(Electrical)規(guī)則設(shè)置是設(shè)置電路板在布線時(shí)必須遵守的規(guī)則,包括安全距離、開路、短路方面的設(shè)置。這幾個(gè)參數(shù)的設(shè)置會(huì)影響所設(shè)計(jì)PCB的生產(chǎn)成本、設(shè)計(jì)難度及設(shè)計(jì)的準(zhǔn)確性,應(yīng)嚴(yán)謹(jǐn)對(duì)待。

1.安全距離(間距)規(guī)則設(shè)置

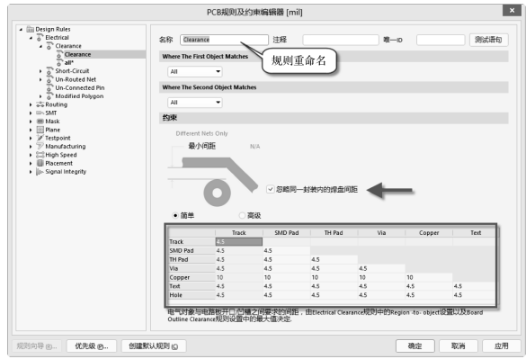

(1)在“Clearance”上單擊鼠標(biāo)右鍵,從彈出的菜單中選擇“新規(guī)則...”選項(xiàng),新建一個(gè)間距規(guī)則,如圖10-10所示。系統(tǒng)將自動(dòng)以當(dāng)前設(shè)計(jì)規(guī)則為準(zhǔn),生成名為“Clearance_1”的新設(shè)計(jì)規(guī)則,不過(guò)可以對(duì)規(guī)則進(jìn)行重命名,如圖10-11所示。

(2)對(duì)網(wǎng)絡(luò)適配范圍進(jìn)行選擇,Altiumdesigner提供5種范圍。

① Different Nets Only:設(shè)置規(guī)則僅對(duì)不同網(wǎng)絡(luò)起作用。

② Same Nets Only:設(shè)置規(guī)則僅對(duì)相同網(wǎng)絡(luò)起作用。

③ Any Net:設(shè)置規(guī)則對(duì)所有網(wǎng)絡(luò)都起作用。

④ Different Differential Pairs:設(shè)置規(guī)則對(duì)不同的差分對(duì)起作用。

⑤ Same Differential Pairs:設(shè)置規(guī)則對(duì)相同的差分對(duì)起作用。

圖10-10規(guī)則的新建

圖10-11規(guī)則設(shè)置界面

(3)在“約束”選項(xiàng)區(qū)域中的“最小間距”文本框里輸入需要設(shè)置的參數(shù)值,這個(gè)參數(shù)值就是需要設(shè)置的間距參數(shù)。

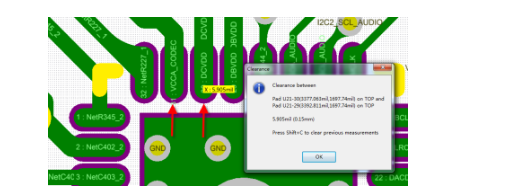

(4)“忽略同一封裝內(nèi)的焊盤間距”指對(duì)于封裝本身的間距不計(jì)算到設(shè)計(jì)的規(guī)則當(dāng)中。這是為什么呢?因?yàn)槿鐖D10-12所示,我們創(chuàng)建的封裝因?yàn)?a href="http://www.3532n.com/tags/pi/" target="_blank">Pitch間距比較小,焊盤和焊盤之間的間距是5.905mil,如果設(shè)計(jì)規(guī)則為6mil的話,按理這個(gè)封裝是不滿足設(shè)計(jì)規(guī)則的,但是因?yàn)榉庋b規(guī)格就是如此,我們就不想這個(gè)封裝自身進(jìn)行報(bào)錯(cuò)提示,這時(shí)可以勾選這個(gè)選項(xiàng),就不會(huì)再進(jìn)行報(bào)錯(cuò)提示了。

圖10-12忽略元件封裝本身的間距報(bào)錯(cuò)

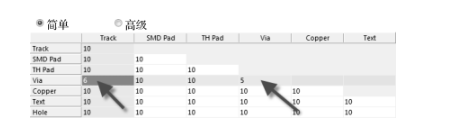

(5)Altium Designer 19提供“簡(jiǎn)單”和“高級(jí)”兩種對(duì)象與對(duì)象的間距設(shè)置,不再像低版本那樣對(duì)每一個(gè)對(duì)象與對(duì)象的間距設(shè)置規(guī)則進(jìn)行疊加。

① 簡(jiǎn)單:這個(gè)選項(xiàng)主要是pcb設(shè)計(jì)當(dāng)中最常用規(guī)則之間的對(duì)象配對(duì)。例如,想設(shè)置Via和Via之間的間距為5mil,只需要在十字交叉處更改自己想用的數(shù)據(jù)即可;又如,想設(shè)置Via和Track之間的間距為6mil,同樣在十字交叉處更改自己想用的數(shù)據(jù)即可,如圖10-13所示。“簡(jiǎn)單”規(guī)則提供常用的對(duì)象規(guī)則,“簡(jiǎn)單”規(guī)則對(duì)象釋義如表10-1所示。

圖10-13 “簡(jiǎn)單”規(guī)則設(shè)置

表10-1 “簡(jiǎn)單”規(guī)則對(duì)象釋義

② 高級(jí):和“簡(jiǎn)單”規(guī)則基本相同,只是增加了更多的對(duì)象選擇,如表10-2所示。

表10-2 “高級(jí)”規(guī)則對(duì)象釋義

(1)個(gè)人經(jīng)驗(yàn)理解是Copper=Polygon+Region+Fill。

(2)板框和電氣對(duì)象之間的間距怎么設(shè)置?它是由Region to Object及Board Outline Clearance規(guī)則設(shè)置中最大值決定的。

(3)常用對(duì)象推薦間距設(shè)置如表10-3所示。

表10-3常用對(duì)象推薦間距設(shè)置

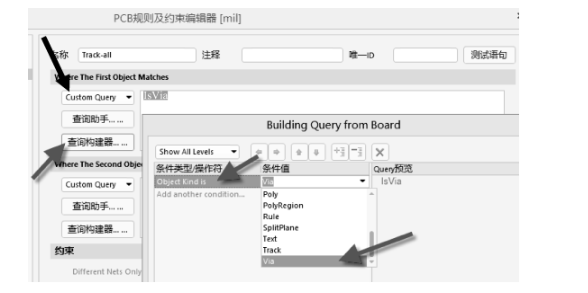

(6)Altium Designer 19也提供類似低版本那樣的多個(gè)間距規(guī)則疊加的方法設(shè)置,通過(guò)選擇第一個(gè)適配對(duì)象和第二個(gè)適配對(duì)象來(lái)篩選規(guī)則應(yīng)用對(duì)象和范圍。

① Where The First Object Matches:選擇規(guī)則第一個(gè)適配對(duì)象。

- All:針對(duì)所有對(duì)象。

- Net:針對(duì)單個(gè)網(wǎng)絡(luò)。

- Net Class:針對(duì)所設(shè)置的網(wǎng)絡(luò)類。

- Net and Layer:針對(duì)網(wǎng)絡(luò)與層。

- Custom Query:自定義適配項(xiàng)。

② Where The Second Object Matches:選擇規(guī)則第二個(gè)適配對(duì)象,與第一個(gè)適配對(duì)象勾選對(duì)象的篩選,即完成規(guī)則定義的范圍。

下面通過(guò)幾個(gè)例子來(lái)說(shuō)明。

A.過(guò)孔與走線的間距規(guī)則設(shè)置

(a)如圖10-14所示,在“Where The First Object Matches”欄中,單擊“Custom Query”。

圖10-14自定義選擇對(duì)象

(b)再單擊“查詢構(gòu)建器......”,在彈出的復(fù)選框中選擇“Object Kind is”。

(c)在彈出的復(fù)選框中選擇對(duì)象“Via”,這時(shí)可以看到自定義對(duì)象出現(xiàn)一個(gè)代碼“IsVia”。

(d)在“Where The Second Object Matches”欄中,進(jìn)行同樣操作選擇規(guī)則對(duì)象“IsTrack”。

(e)在“約束”選項(xiàng)區(qū)域中的“最小間距”文本框里輸入需要設(shè)置的參數(shù)值,如5mil。

后期如果對(duì)規(guī)則代碼比較熟悉了,可以在“Custom Query”窗口中直接輸入相關(guān)規(guī)則代碼,在輸入過(guò)程中,一般會(huì)提示,直接選擇即可,如圖10-15所示。

圖10-15過(guò)孔與走線的間距規(guī)則設(shè)置

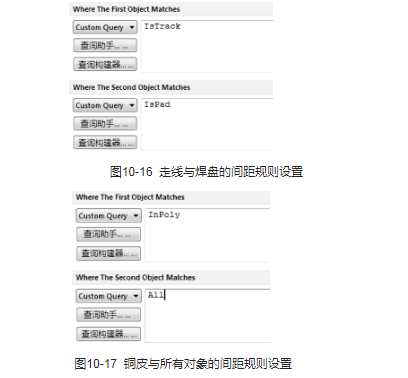

B.走線與焊盤的間距規(guī)則設(shè)置

參考上述方法,可以設(shè)置走線與焊盤的間距規(guī)則,如圖10-16所示。

C.銅皮與所有對(duì)象的間距規(guī)則設(shè)置

參考上述方法,可以設(shè)置銅皮與所有對(duì)象的間距規(guī)則,如圖10-17所示。值得注意的是,對(duì)應(yīng)銅皮前綴不再是“Is”而是“In”,在選擇時(shí)注意代碼的變化。

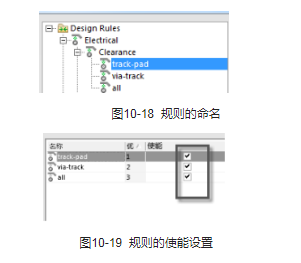

規(guī)則設(shè)置好之后,可以對(duì)所創(chuàng)建的規(guī)則進(jìn)行命名,方便對(duì)規(guī)則的識(shí)別讀取,如圖10-18所示。

2.規(guī)則的使能及優(yōu)先級(jí)設(shè)置

?1)規(guī)則的使能設(shè)置

規(guī)則設(shè)計(jì)好之后,需要對(duì)規(guī)則進(jìn)行使能,否則設(shè)計(jì)的規(guī)則不會(huì)起作用。具體設(shè)計(jì)當(dāng)中很多網(wǎng)友反饋?zhàn)约好髅髟O(shè)計(jì)好了規(guī)則,但是就是不起作用,一般就是這種問(wèn)題引起的。如圖10-19所示,勾選“使能”選項(xiàng)以便啟用設(shè)計(jì)的規(guī)則。

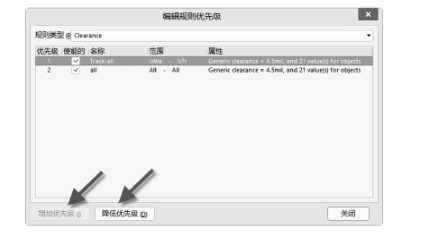

2)規(guī)則的優(yōu)先級(jí)設(shè)置

如果利用了規(guī)則疊加的方法進(jìn)行規(guī)則設(shè)置,因?yàn)榭紤]到有些對(duì)象是包含與被包含的關(guān)系,需要設(shè)置規(guī)則的優(yōu)先級(jí)來(lái)進(jìn)行適配對(duì)象的區(qū)分。比如“All”,這個(gè)代碼是包含“IsTrack”“IsVia”等對(duì)象的,假如設(shè)置了“IsTrack-All”的間距為6mil,“All-All”的間距為5mil,這時(shí)必須把“IsTrack-All”間距規(guī)則放在“All-All”的前面,否則系統(tǒng)無(wú)法識(shí)別。

單擊規(guī)則設(shè)置界面中的“優(yōu)先級(jí)”按鈕,進(jìn)入“編輯規(guī)則優(yōu)先級(jí)”窗口,如圖10-20所示,可以通過(guò)“增加優(yōu)先級(jí)”和“降低優(yōu)先級(jí)”按鈕來(lái)進(jìn)行優(yōu)先級(jí)的調(diào)整。優(yōu)先的規(guī)則,其前面的“優(yōu)先級(jí)”序號(hào)必須更小。

圖10-20 “編輯規(guī)則優(yōu)先級(jí)”窗口

3.短路規(guī)則設(shè)置

在電路設(shè)計(jì)中,是不允許出現(xiàn)短路的板卡的,因?yàn)槎搪肪鸵馕吨锌赡芩O(shè)計(jì)的電路板會(huì)報(bào)廢。所以,一般設(shè)計(jì)當(dāng)中,不要去勾選“允許短路”選項(xiàng),如圖10-21所示。

4.開路規(guī)則設(shè)置

和短路規(guī)則一樣,也不允許開路的存在。對(duì)于這個(gè)開路規(guī)則的選項(xiàng),適配“All”,對(duì)所有的選項(xiàng)都不允許開路的存在。勾選“檢查不完全連接”選項(xiàng),對(duì)連接不完善或者說(shuō)“接觸不良”的線段進(jìn)行開路檢查,如圖10-22所示。

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424215 -

電路板

+關(guān)注

關(guān)注

140文章

5317瀏覽量

108120 -

altium

+關(guān)注

關(guān)注

48文章

1006瀏覽量

122156 -

走線

+關(guān)注

關(guān)注

3文章

120瀏覽量

24619

發(fā)布評(píng)論請(qǐng)先 登錄

從設(shè)計(jì)階段排查預(yù)防PCB短路

PCB設(shè)計(jì)與打樣的6大核心區(qū)別,看完少走3個(gè)月彎路!

高速PCB設(shè)計(jì)EMI避坑指南:5個(gè)實(shí)戰(zhàn)技巧

深度解讀PCB設(shè)計(jì)布局準(zhǔn)則

PCB設(shè)計(jì)中過(guò)孔為什么要錯(cuò)開焊盤位置?

網(wǎng)課回放 I 升級(jí)版“一站式” PCB 設(shè)計(jì)第四期:規(guī)則設(shè)置

開關(guān)電源PCB設(shè)計(jì)技巧和電氣安全規(guī)范

PCB設(shè)計(jì),輕松歸檔,效率倍增!

開關(guān)電源的PCB設(shè)計(jì)

原理圖和PCB設(shè)計(jì)中的常見(jiàn)錯(cuò)誤

Altium Designer中PCB設(shè)計(jì)規(guī)則設(shè)置

PCB設(shè)計(jì)之電氣(Electrical)規(guī)則設(shè)置

PCB設(shè)計(jì)之電氣(Electrical)規(guī)則設(shè)置

評(píng)論