用于計(jì)算機(jī)處理器的硅集成電路正在接近單芯片上晶體管的最大可行密度,至少在二維陣列中情況是這樣的。現(xiàn)在,密歇根大學(xué)的一個(gè)工程師團(tuán)隊(duì)已經(jīng)將第二層晶體管直接堆疊在最先進(jìn)的硅芯片上。研究人員表示,他們的設(shè)計(jì)可以消除對第二個(gè)芯片的需求,該芯片可以在高低電壓信號之間轉(zhuǎn)換。

該項(xiàng)目的負(fù)責(zé)人,電氣工程和計(jì)算機(jī)科學(xué)副教授貝基 · 彼得森說道:“ 我們的方法可以在一個(gè)更小、更輕的硬件中實(shí)現(xiàn)更好的性能。”。摩爾定律認(rèn)為,每一美元所能購買到的計(jì)算能力大約每兩年翻一番。隨著硅晶體管體積縮小,變得更便宜,更省電,它們的工作電壓也下降了。更高的電壓會(huì)損壞越來越小的晶體管,因此,最先進(jìn)的處理芯片與高壓用戶界面組件 ( 如觸摸屏和顯示驅(qū)動(dòng)器 ) 是不兼容的。這些硬件需要更高的電壓運(yùn)行,以避免其正常使用受影響,如錯(cuò)誤的接觸信號或過低的亮度設(shè)置。

彼得森表示:“ 為了解決這個(gè)問題,我們正在將不同類型的設(shè)備與 3D 的硅電路集成在一起,這些設(shè)備允許你做一些硅晶體管做不到的事情。”。由于第二層晶體管可以處理更高的電壓,這實(shí)際上給每個(gè)硅晶體管提供了調(diào)解器,以便與外界交流。這就避免了目前使用最先進(jìn)的處理器和一個(gè)額外的芯片在處理器和接口設(shè)備之間轉(zhuǎn)換信號的弊端。

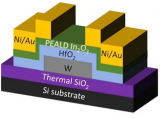

該論文的第一作者,密歇根大學(xué)電子與計(jì)算機(jī)工程學(xué)博士生楊森表示:“ 這使得芯片更加緊湊,功能也比單純使用硅芯片更加強(qiáng)大。”。彼得森的團(tuán)隊(duì)通過使用一種不同的半導(dǎo)體 ( 非晶態(tài)金屬氧化物 ) 來實(shí)現(xiàn)這一目標(biāo),為了在不損壞硅芯片的情況下將這一半導(dǎo)體層應(yīng)用到硅芯片上,他們在芯片上覆蓋了一層含有鋅和錫的溶液,然后將其旋轉(zhuǎn)以形成一層均勻的涂層。

接下來,他們將芯片烘干并重復(fù)這個(gè)過程,在最后的烘烤過程中,金屬與空氣中的氧氣結(jié)合,形成一層鋅錫氧化物。研究小組利用氧化鋅錫薄膜制作薄膜晶體管,這些晶體管可以處理比底層硅更高的電壓。然后,研究小組測試了底層的硅芯片,并確認(rèn)它仍然有效。為了用硅芯片制作有用的電路,鋅錫氧化物晶體管需要與底層的硅晶體管完全通信。這個(gè)團(tuán)隊(duì)通過使用鋅錫氧化物添加兩個(gè)電路元件來實(shí)現(xiàn)這一點(diǎn):一個(gè)垂直薄膜二極管和一個(gè)肖特基門控晶體管。這兩種鋅錫氧化物晶體管連接在一起形成一個(gè)逆變器,在硅芯片使用的低電壓和其他元件使用的高電壓之間進(jìn)行轉(zhuǎn)換。

-

晶體管

+關(guān)注

關(guān)注

78文章

10396瀏覽量

147757 -

硅芯片

+關(guān)注

關(guān)注

0文章

93瀏覽量

17656

發(fā)布評論請先 登錄

揭秘芯片測試:如何驗(yàn)證數(shù)十億個(gè)晶體管

MIT團(tuán)隊(duì)提出一種垂直集成的BEOL堆疊架構(gòu)

探索BFU520Y:雙NPN寬帶硅射頻晶體管的卓越性能

探索Broadcom HLPT-B3x0-00000硅NPN光電晶體管的卓越性能

多值電場型電壓選擇晶體管結(jié)構(gòu)

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

東京大學(xué)開發(fā)氧化銦(InGaOx)新型晶體管,延續(xù)摩爾定律提供新思路

下一代高速芯片晶體管解制造問題解決了!

薄膜晶體管技術(shù)架構(gòu)與主流工藝路線

密歇根大學(xué)團(tuán)隊(duì)將晶體管陣列直接堆疊在硅芯片

密歇根大學(xué)團(tuán)隊(duì)將晶體管陣列直接堆疊在硅芯片

評論