(文章來源:快科技)

今年9月份,半導體企業(yè)Cerebras Systems發(fā)布的世界最大芯片“WSE”震撼行業(yè),臺積電16nm工藝制造的它擁有46225平方毫米面積、1.2萬億個晶體管、40萬個AI核心、18GB SRAM緩存、9PB/s內存帶寬、100Pb/s互連帶寬,而功耗也高達15千瓦。

如此史無前例超大規(guī)模的芯片開發(fā)起來難,應用起來更難,尤其是如何喂飽它的計算能力,還得保證散熱。在此之前,Cerabras已經(jīng)宣布和美國能源部達成合作,如今終于拿出了與美國能源部下屬阿貢國家實驗室合作、基于WSE芯片打造的一套系統(tǒng)“CS-1”。

該系統(tǒng)只有15個標準機架高度,也就是大約66厘米,需要三套才能填滿一個機架,但性能方面十分恐怖,一套就相當于一個擁有1000顆GPU的集群,而后者需要占據(jù)15個機架空間,功耗也要500千瓦,同時相當于Google TPU v3系統(tǒng)的三倍還多,但功耗只有其1/5,體積則只有1/30。

一套CS-1系統(tǒng)的功耗為20千瓦,其中處理器本身15千瓦,另外4千瓦專門用于散熱子系統(tǒng),包括風扇、水泵、導熱排等等,還有1千瓦損失在供電轉換效率上。系統(tǒng)還配備多達12個100GbE十萬兆網(wǎng)口,并且可以擴展組成海量計算節(jié)點,而且測試過超大集群,能夠以單個異構系統(tǒng)的方式進行管理,并行處理數(shù)據(jù)。

那么,這樣一套系統(tǒng)能干什么呢?它主要會用來和傳統(tǒng)大型超級計算機配合,后者處理完數(shù)據(jù)后,就會交給CS-1進行更深入的AI處理。

(責任編輯:fqj)

-

芯片

+關注

關注

463文章

54012瀏覽量

466189 -

半導體

+關注

關注

339文章

30735瀏覽量

264236

發(fā)布評論請先 登錄

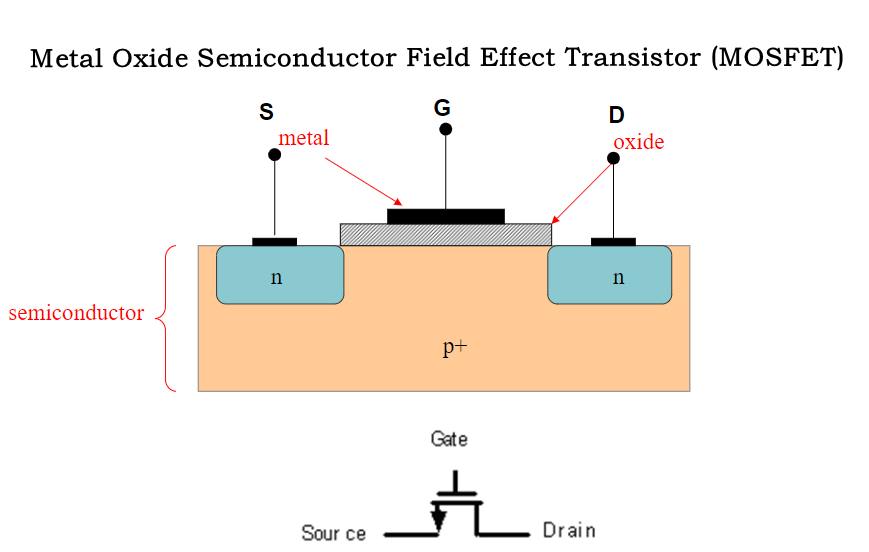

深度解讀晶體管的轉移特性曲線

電壓選擇晶體管應用電路第二期

晶體管的定義,晶體管測量參數(shù)和參數(shù)測量儀器

多值電場型電壓選擇晶體管結構

晶體管架構的演變過程

英偉達一夜大漲1.2萬億元,市值重回全球第一!

下一代高速芯片晶體管解制造問題解決了!

CMOS第一層互聯(lián)的結構與作用

無結場效應晶體管詳解

世界第一的強大芯片,擁有40萬核心1.2萬億晶體管

世界第一的強大芯片,擁有40萬核心1.2萬億晶體管

評論