到底什么是傳統(tǒng)的串行工程,什么又是并行工程呢?

這就類似電路中的串聯(lián)與并聯(lián),若用電器逐個(gè)依次首尾相連,屬于串聯(lián),若首首并連,屬于并聯(lián)。舉個(gè)簡(jiǎn)單的例子,Layout工程師在設(shè)計(jì)一款產(chǎn)品時(shí)時(shí),所有工作由一個(gè)人完成,先布局電源部分,再布局功能部分,最后布局功能小板,這就是串行工程;而同一款產(chǎn)品設(shè)計(jì),由3個(gè)不同的工程師分別布局電源,功能,功能小板,最后整合,這就是并行工程。

串行與并行開發(fā)流程,以PCB設(shè)計(jì)為例,如下圖:

傳統(tǒng)的串行開發(fā)模式有一個(gè)糟糕的開局,也就必然會(huì)有后續(xù)不斷的設(shè)計(jì)更改、設(shè)計(jì)優(yōu)化等。在很多批量生產(chǎn)的設(shè)計(jì)實(shí)踐中,一開始參與的人數(shù)非常少,沒有考慮制造、測(cè)試、裝配、成本、質(zhì)量等因素,在臨近發(fā)布日期的時(shí)候人數(shù)增長(zhǎng)到了峰值,很多人參與到了解決問題的過程中。然而,這些問題本應(yīng)該在一開始就要被清理干凈。

如果一個(gè)項(xiàng)目沒有早期被納入DFX,那么在后期想要使產(chǎn)品具有可制造性、可裝配性,可測(cè)試性,可維護(hù)性,成本優(yōu)化,可維護(hù)性等等,那將變得異常困難,即產(chǎn)品開發(fā)的墨菲定律。在緊張的時(shí)間壓力下,面對(duì)著通過更改訂單實(shí)施DFX的艱巨難題,團(tuán)隊(duì)只會(huì)進(jìn)行簡(jiǎn)單的修改,導(dǎo)致產(chǎn)品的可制造性、產(chǎn)品質(zhì)量等更為不可靠。

簡(jiǎn)單歸納:

- 并行工程要求:產(chǎn)品在一開始就考慮產(chǎn)品整個(gè)生命周期中從概念形成到產(chǎn)品生命周期結(jié)束的所有因素,包括制造、裝配、測(cè)試、質(zhì)量、成本、進(jìn)度計(jì)劃和用戶要求等

- 目標(biāo):并行工程的目標(biāo)為提高質(zhì)量、降低成本、縮短產(chǎn)品開發(fā)周期和產(chǎn)品上市時(shí)間。

- 具體做法:在產(chǎn)品開發(fā)階段,組織多種職能協(xié)同工作的項(xiàng)目組,并使用并行工具,使有關(guān)人員從一開始就獲得對(duì)新產(chǎn)品需求的要求和信息,積極研究涉及本部門的工作業(yè)務(wù),并將所需要求提供給設(shè)計(jì)人員,使許多問題在開發(fā)早期就得到解決,從而保證了設(shè)計(jì)的質(zhì)量,避免了大量的返工浪費(fèi).

然而,決定并行工程成敗的關(guān)鍵因素是資源的可獲得性,充足的資源能夠讓多功能型團(tuán)隊(duì)的各領(lǐng)域?qū)<以谠缙诩Y(jié)并開始工作。

發(fā)布評(píng)論請(qǐng)先 登錄

并行sram芯片介紹,并行sram芯片應(yīng)用場(chǎng)景

探索PCA9665/PCA9665A:Fm+并行總線到I2C總線控制器的深度解析

請(qǐng)問我的for循環(huán)并行結(jié)構(gòu)使用的對(duì)嗎,網(wǎng)上我沒找到太多的介紹并行結(jié)構(gòu)的資料。

串行通訊與并行通訊介紹

一文看懂AI大模型的并行訓(xùn)練方式(DP、PP、TP、EP)

并行與串行的基本通信方式

串行通信和并行通信的區(qū)別是什么

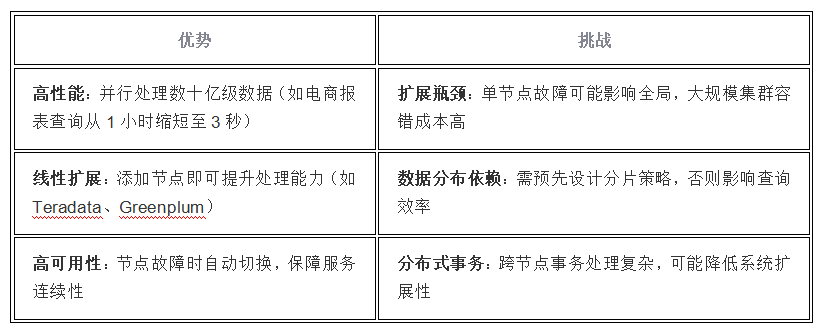

多節(jié)點(diǎn)并行處理架構(gòu)

300 kHz 至 2.0 GHz 5 位數(shù)字衰減器,帶串轉(zhuǎn)并行驅(qū)動(dòng)器 skyworksinc

0.01 – 4.0 GHz 7 位數(shù)字衰減器,帶串行和并行驅(qū)動(dòng)器 skyworksinc

讀懂極易并行計(jì)算:定義、挑戰(zhàn)與解決方案

用FPGA并行通信讀取位置角度AD2S1210的最快角度更新速率是多少,是1/t16 HZ嗎?

如何使用S32DS在MPC5775B中并行運(yùn)行兩個(gè)內(nèi)核(core0 和 core2)?

如何使用FPGA驅(qū)動(dòng)并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時(shí)的注意事項(xiàng)

DFX——并行工程2

DFX——并行工程2

評(píng)論