臺積電近日宣布,已經開始了7nm+ EUV工藝的大規模量產,這是該公司乃至整個半導體產業首個商用EUV極紫外光刻技術的工藝。作為EUV設備唯一提供商,市場預估荷蘭ASML公司籍此EUV設備年增長率將超過66%。這個目標是否能實現?EUV工藝在發展過程中面臨哪些挑戰?產業化進程中需要突破哪些瓶頸?

EUV設備讓摩爾定律再延伸三代工藝

光刻是集成電路生產過程中最復雜、難度最大也是最為關鍵的工藝,它對芯片的工藝制程起著決定性作用。193nm浸沒式光刻技術自2004年年底由臺積電和IBM公司應用以來,從90nm節點一直延伸到10nm節點,經歷了12年時間,是目前主流的光刻工藝。但是進入7nm工藝后,它的制約也越來越明顯,因此EUV工藝堂而皇之走上舞臺。

全球EUV光刻技術的研發始于20世紀80年代,經過近40年的發展,EUV技術從原理到零部件再到原材料等已經足夠成熟,并且在現階段的產業應用中體現了較明顯優勢。

研究院王珺在接受《中國電子報》記者采訪時表示,極紫外光(EUV)短于深紫外光(DUV)的波長,這讓EUV光刻技術的應用顯著提升了光刻機曝光分辨率,進而帶動晶體管特征尺寸的縮減。制造企業在28nm及以下工藝的解決方案使用浸沒式和多重曝光技術。但是進入7nm工藝,DUV的多重曝光次數增長太多,讓制造成本、難度、良率、交付期限均顯著惡化。在關鍵層應用EUV光刻技術,從而減少曝光次數,進而帶來制造成本與難度的降低,這讓EUV光刻技術具備了足夠的生產價值。

“EUV光刻機在5nm及以下工藝具有不可替代性,在未來較長時間內應用EUV技術都將成為實現摩爾定律發展的重要方向。”王珺說。因此,從工藝技術和制造成本綜合因素考量,EUV設備被普遍認為是7nm以下工藝節點最佳選擇,它可以繼續往下延伸三代工藝,讓摩爾定律再至少延長10年時間。

DRAM存儲器將帶動EUV光刻機增長

在臺積電、三星、英特爾繼續延續摩爾定律進行工藝發展的帶動下,EUV光刻機的應用數量將持續提升。

王珺表示,從目前看,對EUV光刻技術具有明顯應用需求的芯片包括應用處理器、CPU、DRAM存儲器、基帶芯片。

半導體專家莫大康認為,ASML公司EUV設備產量若要進一步擴大,希望就落在存儲器廠商身上。他向《中國電子報》記者表示,目前看,EUV光刻機主要賣給三家公司:英特爾、三星和臺積電,其中臺積電訂得最多。他介紹說,存儲器主要分為兩種:一種是DRAM,另一種是3D NAND。3D NAND目前的競爭主要集中在層數上,雖然也需要工藝的先進性,但需求不那么迫切。而DRAM存儲器則不同,一方面其產量比較大,另一方面若做到1Z(12~14nm)以下,就可能需要用到EUV光刻機了,屆時,存儲器廠商訂的EUV設備將有大的爆發。“但具體時間,還要看市場需求以及廠商導入情況。目前,ASML公司EUV設備一年的出貨量只有40多臺,遠遠未達到業界預期。”

EUV還需克服諸多挑戰

現階段EUV光刻技術已經成熟,且進入產業化階段,但是在光刻機的光源效率、光刻膠的靈敏度等方面依然存在較大的進步空間。

有關人士指出,EUV光刻機除了價格昂貴之外(超過1億美元),最大的問題是電能消耗,電能利用率低,是傳統193nm光刻機的10倍,因為極紫外光的波長僅有 13.5nm,投射到晶圓表面曝光的強度只有光進入EUV設備光路系統前的2%。在7nm成本比較中,7nm的EUV生產效率在80片/小時的耗電成本是14nm的傳統光刻生產效率在240片/小時耗電成本的1倍,這還不算設備購置成本和掩膜版設計制造成本比較。

莫大康認為EUV工藝面臨三大挑戰:首先是光源效率,即每小時刻多少片,按照工藝要求,要達到每小時250片,而現在EUV光源效率達不到這個標準,因此還需進一步提高,且技術難度相當大。其次是光刻膠,光刻膠的問題主要體現在:EUV光刻機和普通光刻機原理不同,普通光刻機采用投影進行光刻,而EUV光刻機則利用反射光,要通過反光鏡,因此,光子和光刻膠的化學反應變得不可控,有時候會出差錯,這也是迫切需要解決的難題。最后是光刻機保護層的透光材料,隨著光刻機精度越來越高,上面需要一層保護層,現在的材料還不夠好,透光率比較差。

在以上三個挑戰中,光源效率是最主要的。此外,EUV光刻工藝的良率也是阻礙其發展的“絆腳石”。目前,采用一般光刻機生產的良率在95%,EUV光刻機的良率則比它低不少,在70%~80%之間。莫大康表示,解決上述問題,關鍵是訂單數量,只有訂單多了,廠商用的多了,才能吸引更多光源、材料等上下游企業共同參與,完善EUV產業鏈的發展。

王珺表示,EUV技術的研發與應用難度極高,未來實現進一步發展在全球范圍內將遵循競爭優勢理論,各國和地區的供應商依靠自身優勢進行國際化產業整合。

-

臺積電

+關注

關注

44文章

5803瀏覽量

176322 -

摩爾定律

+關注

關注

4文章

640瀏覽量

80908 -

EUV

+關注

關注

8文章

615瀏覽量

88807

發布評論請先 登錄

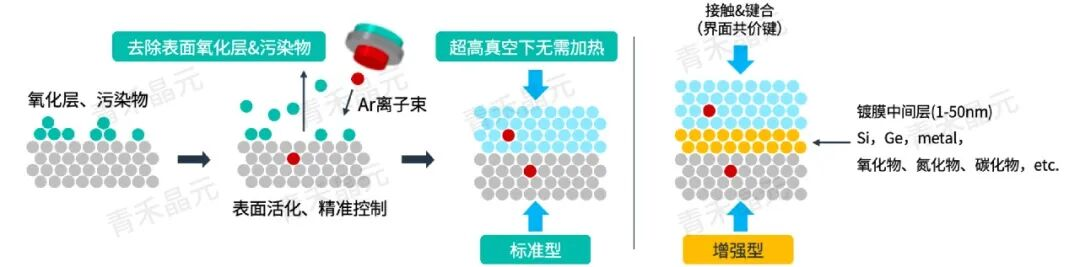

青禾晶元常溫鍵合方案,破解第三代半導體異質集成熱損傷難題

Neway第三代GaN系列模塊的生產成本

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

借助AMD無頂蓋封裝技術應對散熱挑戰

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數據測量的設備

第三代半導體的優勢和應用領域

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

EUV設備讓摩爾定律再延伸三代工藝 但需克服諸多挑戰

EUV設備讓摩爾定律再延伸三代工藝 但需克服諸多挑戰

評論