N年的寶貴經驗告訴我們,遇到過孔stub時,最好辦法就是器件在表層走線靠下層,器件在底層走線就靠上層,這樣能把stub降到最低。但是,有沒有這樣一種情況,你們覺得無論走哪一層都覺得不能把stub降得很低的情況呢?

恩,還真有這么一種操作,而且其實我們還見得不少。在比較理想的器件布局下,我們喜歡把高速信號的收發芯片都放在同一面,要么都是表層,要么都是底層。原因很簡單,這樣的話我們從表層的pin打孔到內層走線時,只要我們走到了靠下的層(以器件放表層說明,如果是放底層則相反哈),這樣兩個過孔就都會是比較短的過孔stub,有利于提高信號傳輸質量。而且不要老是動不動就提要背鉆這事嘛,能保證質量的同時又可以簡單快捷的省成本和加工流程這種好事,相信誰都不會拒絕吧?

但是,有的高速信號卻不能做到兩個器件都放在正面,看起來好像顯得我們不重視這些高速走線似的。大家是不是覺得只要我們想優先保證它們的傳輸的話,就肯定輕松的做到先把它們都放在表層是吧?有的東西連臣妾都不能保證啊,更何況PCB工程師呢?例如,其中一個器件是雙面都有高速走線的pin……

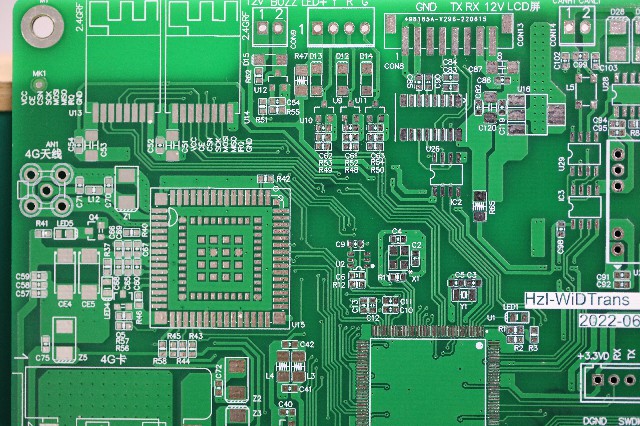

其實這樣的器件是有的,而且應用很廣泛,其中一種就是我們今天的主人公,PCIE金手指。在我們很多PCIE子卡設計中,都會遇到它。它的封裝就是雙面的焊盤結構。這樣的PCIE信號我們最近接觸非常多,主要就是應用在現在很火的人工智能領域上。

像上圖高亮的TX鏈路(怎么分的TX還是RX?看看電容唄)是在底層,而我們的主芯片放在表層,那我們的內線走線好像走到哪一層就是不能達到放同一面時的效果,無論是放在靠上層還是靠下層,都會有其中一個過孔有很長的stub。這時能夠想象PCB工程師的心情就好像下圖的情況一樣矛盾……

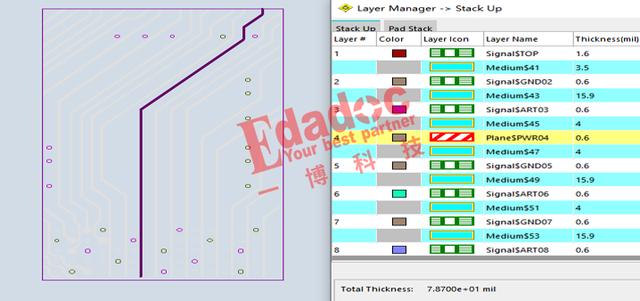

在說完了前面的鋪墊之后,再說說本文想描述的案例。該信號走的是PCIE3.0的協議(8Gbps),板厚是2.0mm。在第一版中,客戶為了省成本,問我們能不能不背鉆處理,然后我們高速先生也不是動不動就叫客戶背鉆的,因為經過驗證之后,認為把走線走到靠下層時,長過孔的stub大概在60mil左右,對于8Gbps的信號仍在可以接受的范圍。客戶也懷著將信將疑的心態投了板,不過還好沒等多久,回板之后客戶進行了PCIE的測試(子卡插到base進行測試),發現真的是OK的哦,傳輸沒有問題。

一切都沒什么問題之后,后面客戶又開始了第二版,其他走線有一些改動,PCIE這部分原理圖沒有改動。本來按說PCIE直接copy就好了,但是由于靠下面的走線需要讓給更高速的信號,因此無法繼續按照上一版靠底層走線。這時PCB工程師想到反正都會有一個長的過孔stub,影響應該是一樣的,因此就把走線放在和下層對稱的上層去走,于是就第二版的鏈路變成了這樣(由于后面要對比兩者的區別,因此我們用同一條鏈路不同走線層來對比會更有說服力)。

這就是前面說到,無論靠上還是靠下都會有一個長的過孔stub無法避免。其實乍一看,感覺應該是一樣的,因為還是有一個長的和一個短的過孔stub的影響。事實上是這樣嗎?

我們把兩種情況進行仿真對比一下,他們的傳輸損耗有非常驚人的結論,那就是真的就是一樣的。如下所示:高速先生們再三確認后。確定真的是有兩根曲線,真的一模一樣哈。紅的曲線被綠的覆蓋了……

后面想了一下,其實一樣也是對的。對于這種線性時不變系統而言。事實上他們就應該是一樣的。理論不想過多解釋哈,對于這種名詞大家感興趣再去搜搜哈。簡單來說就是從最后接收來看,首先時間是一樣的,然后stub一樣的情況下是不care長stub和短stub的順序,能量經過振蕩傳輸到接收端的時候就是一樣的。那看起來這種case下走靠上還是靠下層真沒有影響?

很多時候當你有一個認為正確的結論時,往往需要經得住很多人的敲打。例如有同事就提出,要不給他們賦了收發模型看看眼圖是不是也一樣?好,這個主意非常好,因為對于很多人來說,S參數遠沒有時域的波形或者眼圖直觀,于是我們加入收發模型進行仿真后,就立馬把這個結論推翻了……

突然發現原有差距會那么大,眼高居然差了50多mV。兩者看起來波形都不錯,但是在PCIE鏈路中,這個只是子卡部分,插上base板后接收裕量就肯定很小了,所以這個已經是一個很大的差距了。

在驚訝之余我們再回頭看看這兩條鏈路的回波損耗,終于發現了不一樣的地方。

從回波損耗來看,版本一的結果的確會比版本二要好。這就是導致眼圖有差異的原因了。所以對于這種始終會存在過孔stub的情況下,我們走線層的選擇其實會影響很大,不能再按照傳統的單純靠下層或者靠上層來走了,這時候必須具體問題具體分析哈。

責任編輯:ct

-

pcb

+關注

關注

4405文章

23882瀏覽量

424420 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44643

發布評論請先 登錄

PCB板上你是普通油墨,我是低損耗油墨,能一樣嗎?

PCB板雙面布局的DDR表底走線居然不一樣

到底DDR走線能不能參考電源層啊?

不一樣的展會,不一樣的精彩 2025灣芯展圓滿收官

不一樣的展會,不一樣的精彩:2025灣芯展順利收官

不同的走線層,一樣的STUB

不同的走線層,一樣的STUB

評論