FPGA在目前應(yīng)用領(lǐng)域非常,在目前的單板設(shè)計(jì)里面,幾乎都可以看到它的身影。從簡(jiǎn)單的邏輯組合,到高端的圖像、通信協(xié)議處理,從單片邏輯到復(fù)雜的ASIC原型驗(yàn)證,從小家電到航天器,都可以看到FPGA應(yīng)用,它的優(yōu)點(diǎn)在這里無(wú)庸贅述。從個(gè)人實(shí)用角度看,對(duì)于學(xué)生,掌握FPGA可以找到一份很好的工作,對(duì)于有經(jīng)驗(yàn)的工作人員,使用fgpa可以讓設(shè)計(jì)變得非常有靈活性。掌握了fpga的設(shè)計(jì),單板硬件設(shè)計(jì)就非常容易(不是系統(tǒng)設(shè)計(jì)),特別是上大學(xué)時(shí)如同天書(shū)的邏輯時(shí)序圖,看起來(lái)就非常親切。但fpga的入門(mén)卻有一定難度,因?yàn)樗幌褴浖O(shè)計(jì),只要有一臺(tái)計(jì)算機(jī),幾乎就可以完成所有的設(shè)計(jì)。fpga的設(shè)計(jì)與硬件直接相關(guān),需要實(shí)實(shí)在在的調(diào)試儀器,譬如示波器等。這些硬件設(shè)備一般比較昂貴,這就造成一定的入門(mén)門(mén)檻,新人在入門(mén)時(shí)遇到一點(diǎn)問(wèn)題或者困難,由于沒(méi)有調(diào)試設(shè)備,無(wú)法定位問(wèn)題,最后可能就會(huì)放棄。其實(shí)這時(shí)如果有人稍微指點(diǎn)一下,這個(gè)門(mén)檻很容易就過(guò)去。

我用FPGA做設(shè)計(jì)很多年了,遠(yuǎn)達(dá)不到精通的境界,只是熟悉使用,在這里把我對(duì)fpga的學(xué)習(xí)步驟理解寫(xiě)出來(lái),僅是作為一個(gè)參考,不對(duì)的地方,歡迎大家討論和指正。

1、工欲善其事,必先利其器。

計(jì)算機(jī)必不可少。目前FPGA應(yīng)用較多的是Altera和xilinx這兩個(gè)公司,可以選擇安裝quartusII或者ISE軟件。這是必備的軟件環(huán)境。

硬件環(huán)境還需要下載器、目標(biāo)板。雖然有人說(shuō)沒(méi)有下載器和目標(biāo)板也可學(xué)習(xí)fpga,但那總是紙上談兵。這就像談女朋友, 總是嘴上說(shuō)說(shuō),通個(gè)電話,連個(gè)手都沒(méi)牽,能說(shuō)人家是你朋友?雖說(shuō)搭建硬件環(huán)境需要花費(fèi),但想想,硬件環(huán)境至多幾百元錢(qián), 你要真的掌握FPGA的設(shè)計(jì),起薪比別人都不止高出這么多。這點(diǎn)花費(fèi)算什么?

2、熟悉verilog語(yǔ)言或者vhdl語(yǔ)言 ,熟練使用quartusII或者ISE軟件。

VHDL和verilog各有優(yōu)點(diǎn),選擇一個(gè),建議選擇verilog。熟練使用設(shè)計(jì)軟件,知道怎樣編譯、仿真、下載等過(guò)程。

3、設(shè)計(jì)一個(gè)小代碼,下載到目標(biāo)板看看結(jié)果

此時(shí)可以設(shè)計(jì)一個(gè)最簡(jiǎn)答的程序,譬如點(diǎn)燈。如果燈在閃爍了,表示基本入門(mén)了。如果此時(shí)能夠下載到fpga外掛的flash,fpga程序能夠從flash啟動(dòng),表明fpga的最簡(jiǎn)單設(shè)計(jì)你已經(jīng)成功,可以到下一步。

4、設(shè)計(jì)稍微復(fù)雜的代碼,下載到目標(biāo)板看看結(jié)果。

可以設(shè)計(jì)一個(gè)UART程序,網(wǎng)上有參考,你要懂RS232協(xié)議和fpga內(nèi)置的邏輯分析儀。網(wǎng)上下載一個(gè)串口調(diào)試助手,調(diào)試一番,如果通信成功了, 恭喜,水平有提高。進(jìn)入下一步。

5、設(shè)計(jì)復(fù)雜的代碼,下載到目標(biāo)板看看結(jié)果。

譬如sdram的程序,網(wǎng)上也有參考,這個(gè)設(shè)計(jì)難度有點(diǎn)大。可用串口來(lái)調(diào)試sdram,把串口的數(shù)據(jù)存儲(chǔ)到sdram,然后讀回,如果成功,那你就比較熟悉fpga的設(shè)計(jì)餓了

6、設(shè)計(jì)高速接口,譬如ddr2或者高速串行接口

這要對(duì)fpga的物理特性非常了解,而且要懂得是時(shí)序約束等設(shè)計(jì)方法,要看大量的原廠文檔,這部分成功了,那就對(duì)fpga的物理接口掌握很深,你就是設(shè)計(jì)高手了

7、設(shè)計(jì)一個(gè)復(fù)雜的協(xié)議

譬如USB、PCIexpress、圖像編解碼等,鍛煉對(duì)系統(tǒng)的整體把握和邏輯劃分。完成這些,你就是一個(gè)一流的高手、

8、學(xué)習(xí)再學(xué)習(xí)

學(xué)習(xí)什么,我也不知道,我只知道“學(xué)無(wú)止境,山外有山”。

最近也面試了很多FPGA工程師,沒(méi)找到合適,我覺(jué)得很多人從開(kāi)始的時(shí)候就誤入歧途了,對(duì)新手學(xué)習(xí)FPGA設(shè)計(jì)我也說(shuō)一點(diǎn)看法吧。我認(rèn)為要從基礎(chǔ)開(kāi)始做,基礎(chǔ)牢,才有成為高手的可能。

我覺(jué)得有以下幾步必須要走:

第一步:學(xué)習(xí)了解FPGA結(jié)構(gòu),F(xiàn)PGA到底是什么東西,芯片里面有什么,不要開(kāi)始就拿個(gè)開(kāi)發(fā)板照著別人的東西去編程。很多開(kāi)發(fā)板的程序?qū)懙暮軤€,我也做過(guò)一段時(shí)間的開(kāi)發(fā)板設(shè)計(jì),我覺(jué)得很大程度上,開(kāi)發(fā)板在誤人子弟。不過(guò)原廠提供的正品開(kāi)發(fā)板,代碼很優(yōu)秀的,可以借鑒。只有了解了FPGA內(nèi)部的結(jié)構(gòu)才能明白為什么寫(xiě)Verilog和寫(xiě)C整體思路是不一樣的。

第二步:掌握FPGA設(shè)計(jì)的流程。了解每一步在做什么,為什么要那么做。很多人都是不就是那幾步嗎,有什么奇怪的?呵呵,我想至少有一半以上的人不知道synthesize和traslate的區(qū)別吧。

了解了FPGA的結(jié)構(gòu)和設(shè)計(jì)流程才有可能知道怎么去優(yōu)化設(shè)計(jì),提高速度,減少資源,不要急躁,不要去在為選擇什么語(yǔ)言和選擇哪個(gè)公司的芯片上下功夫。語(yǔ)言只是一個(gè)表達(dá)的方式,重要的是你的思維,沒(méi)有一個(gè)好的指導(dǎo)思想,語(yǔ)言用得再好,不過(guò)是個(gè)懂語(yǔ)言的人。

第三步:開(kāi)始學(xué)習(xí)代碼了。我建議要學(xué)代碼的人都去Altera或Xilinx的網(wǎng)站上下原廠工程師的代碼學(xué)習(xí)。不要一開(kāi)始就走入誤區(qū)。

第四步:template很重要。能不能高效利用fpga資源,一是了解fpga結(jié)構(gòu),二是了解欲實(shí)現(xiàn)的邏輯功能和基本機(jī)構(gòu),三是使用正確的模板。FPGA內(nèi)部器件種類(lèi)相對(duì)較單一,用好模板,你的邏輯才能被高效的綜合成FPGA擅長(zhǎng)表達(dá)的結(jié)構(gòu):)

做fpga主要是要有電路的思想,作為初學(xué)者,往往對(duì)器件可能不是熟悉,那么應(yīng)該對(duì)于數(shù)字電路的知識(shí)很熟悉吧,fpga中是由觸發(fā)器和查找表以及互聯(lián)線等基本結(jié)構(gòu)組成的,其實(shí)在我們?cè)诖a里面能夠看到的就是與非門(mén)以及觸發(fā)器,不要把verilog和c語(yǔ)言等同起來(lái),根本就是不同的東西,沒(méi)有什么可比性,在寫(xiě)一句程序的時(shí)候應(yīng)該想到出來(lái)的是一個(gè)什么樣的電路,計(jì)數(shù)器 選擇器 三態(tài)門(mén)等等,理解時(shí)序,邏輯是一拍一拍的東西,在設(shè)計(jì)初期想的不是很清楚的時(shí)候可以畫(huà)畫(huà)時(shí)序圖,這樣思路會(huì)更加的清晰,還有就是仿真很重要,不要寫(xiě)完程序就去往fpga中去加載,首先要仿真,尤其是對(duì)比較大型一點(diǎn)的程序,想像自己是在做asic,是沒(méi)有二次機(jī)會(huì)的,所以一定要把仿真做好,還有很多新手對(duì)于語(yǔ)言的學(xué)習(xí)不知道選vhdl好還是verilog好,個(gè)人偏好verilog,當(dāng)然不是說(shuō)vhdl不好,反正寫(xiě)出來(lái)的都是電路,那當(dāng)然就不要在語(yǔ)言的語(yǔ)法上面花太多的功夫了,verilog 言簡(jiǎn)意賅assign always case if else 掌握這些幾乎可以寫(xiě)出90%的電路了

責(zé)任編輯:ct

-

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424243 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44637

發(fā)布評(píng)論請(qǐng)先 登錄

學(xué)習(xí)單片機(jī)快速方法

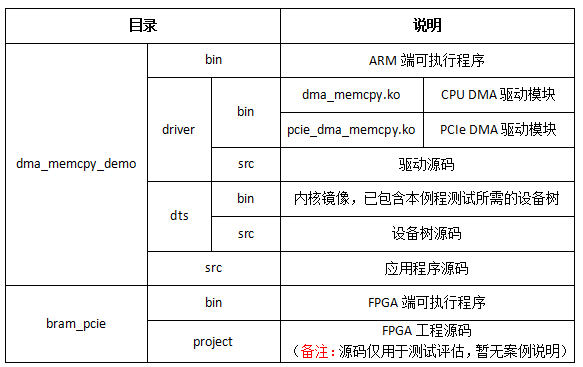

基于瑞芯微 RK3588 的 ARM 與 FPGA 交互通信實(shí)戰(zhàn)指南

開(kāi)源RISC-V處理器(蜂鳥(niǎo)E203)學(xué)習(xí)(二)修改FPGA綜合環(huán)境(移植到自己的Xilinx FPGA板卡)

學(xué)習(xí)物聯(lián)網(wǎng)怎么入門(mén)?

數(shù)據(jù)濾波算法的具體實(shí)現(xiàn)步驟是怎樣的?

如何在FPGA部署AI模型

無(wú)鉛焊接工藝有哪些步驟?

FPGA在機(jī)器學(xué)習(xí)中的具體應(yīng)用

智多晶FPGA設(shè)計(jì)工具HqFpga接入DeepSeek大模型

FPGA從0到1學(xué)習(xí)資料集錦

【干貨】基于串口的FPGA遠(yuǎn)程升級(jí)

FPGA學(xué)習(xí)步驟是怎樣的

FPGA學(xué)習(xí)步驟是怎樣的

評(píng)論