在線(xiàn)仿真領(lǐng)域最近一項(xiàng)重要的創(chuàng)新是開(kāi)發(fā)行為仿真方法。這些方法將仿真和仿真加速引擎連接到高速總線(xiàn)上,以便在設(shè)計(jì)驗(yàn)證速度下提供100倍到10,000倍的增益。

實(shí)現(xiàn)了這種卓越的性能通過(guò)在可重構(gòu)邏輯中創(chuàng)建事件精確的IEEE 1364兼容(Verilog)仿真模型:FPGA。行為仿真器自動(dòng)對(duì)仿真和通過(guò)高速總線(xiàn)連接的仿真引擎之間的混合級(jí)設(shè)計(jì)進(jìn)行分區(qū),并消除網(wǎng)絡(luò)解決方案中固有的延遲。在100萬(wàn)門(mén)級(jí)別,典型的門(mén)級(jí)模擬器在10Hz以下工作,行為模擬器在低于100Hz時(shí),新的行為仿真器提供優(yōu)于10KHz的驗(yàn)證性能 - 驗(yàn)證性能提高了三個(gè)數(shù)量級(jí)。在更具挑戰(zhàn)性的1000萬(wàn)門(mén)設(shè)計(jì)中,門(mén)級(jí)仿真器低至0.1Hz,行為仿真器的工作頻率低于10Hz,而行為仿真器仍可提供10KHz,性能提升10,000倍。

在行為仿真之前,運(yùn)行具有寄存器傳輸級(jí)(RTL)設(shè)計(jì)的行為級(jí)測(cè)試平臺(tái)的最先進(jìn)技術(shù)是編譯設(shè)計(jì)以在仿真器中運(yùn)行,而測(cè)試臺(tái)在通過(guò)網(wǎng)絡(luò)連接與仿真器連接的工作站上運(yùn)行。這種方法運(yùn)行良好,但由于網(wǎng)絡(luò)協(xié)議在工作站和仿真系統(tǒng)之間來(lái)回傳遞數(shù)據(jù)所引入的瓶頸,因此速度不夠快。這些新的行為仿真器使得可以在雙引擎仿真器上運(yùn)行整個(gè)驗(yàn)證過(guò)程,并在嵌入式處理器上運(yùn)行測(cè)試平臺(tái)。由于測(cè)試平臺(tái)和仿真器之間的通信是在高速總線(xiàn)上進(jìn)行的,因此這種方法速度更快,延遲更低。支持PLI例程可以輕松地將仿真使用融入現(xiàn)有的驗(yàn)證方法中。

與仿真不同,行為仿真可以在線(xiàn)運(yùn)行,提供更高級(jí)別的驗(yàn)證,通常很多更快的運(yùn)行。考慮一個(gè)混合級(jí)別的片上系統(tǒng),其中大部分設(shè)計(jì)以門(mén)級(jí)描述的形式提供。另一方面,兩個(gè)所需的模型,CAM(內(nèi)容可尋址存儲(chǔ)器)和PCI總線(xiàn)模型,是不可合成的。通過(guò)使用行為仿真器,可以將整個(gè)設(shè)計(jì)映射到一個(gè)集成系統(tǒng)上,其中包含F(xiàn)PGA上的門(mén)級(jí)描述和處理器上的行為代碼。然后,仿真器本身可以插入PCB插座。測(cè)試激勵(lì)來(lái)自PCB及其外部連接,在事件級(jí)仿真上提供了四到五個(gè)數(shù)量級(jí)的速度提升。

網(wǎng)絡(luò)設(shè)備的主要供應(yīng)商使用那些驗(yàn)證具有服務(wù)質(zhì)量功能的千兆以太網(wǎng)交換機(jī)的方法。該芯片設(shè)計(jì)具有400萬(wàn)個(gè)ASIC門(mén),驗(yàn)證計(jì)劃要求建模和模擬真實(shí)的網(wǎng)絡(luò)流量,以準(zhǔn)確地對(duì)芯片進(jìn)行壓力測(cè)試。該公司考慮使用模擬,但估計(jì)的性能太慢,無(wú)法模擬足夠的隨機(jī)事件和超時(shí),以提供真實(shí)的壓力測(cè)試。此外,事件模擬無(wú)法提供所需的準(zhǔn)確性,因?yàn)樗鼰o(wú)法模擬真實(shí)的外部流量。最重要的是,他們項(xiàng)目的預(yù)算不允許購(gòu)買(mǎi)仿真系統(tǒng)。

該解決方案是一個(gè)基于時(shí)間的遠(yuǎn)程訪(fǎng)問(wèn)驗(yàn)證環(huán)境。無(wú)論他們居住在哪里,該公司的設(shè)計(jì)團(tuán)隊(duì)成員都登錄到主機(jī)PC運(yùn)行目標(biāo)操作系統(tǒng)的系統(tǒng)。 PC與一個(gè)在線(xiàn)仿真系統(tǒng)相連,而該仿真系統(tǒng)又與一個(gè)網(wǎng)絡(luò)流量發(fā)生器相連。使用這種遠(yuǎn)程訪(fǎng)問(wèn)驗(yàn)證服務(wù),該公司能夠使用真正的外圍組件互連(PCI)流量進(jìn)行軟件和測(cè)試平臺(tái)開(kāi)發(fā),硬件/軟件協(xié)同驗(yàn)證以及硬件上的軟件調(diào)試,而無(wú)需購(gòu)買(mǎi)仿真硬件。

設(shè)計(jì)團(tuán)隊(duì)使用這些基于時(shí)間的驗(yàn)證服務(wù)來(lái)模擬ASIC交換機(jī),速度比事件模擬器的性能快780倍。仿真以500包/秒進(jìn)行。吞吐量,從RTL到400萬(wàn)ASIC門(mén)的仿真僅需一個(gè)半小時(shí)。為了確保設(shè)計(jì)的準(zhǔn)確性,團(tuán)隊(duì)使用真實(shí)的數(shù)據(jù)包將實(shí)際網(wǎng)絡(luò)流量應(yīng)用于模擬設(shè)計(jì),以模擬隨機(jī)事件,刺激響應(yīng)和分析以及完整調(diào)試。

遠(yuǎn)程驗(yàn)證過(guò)程成功,找到了六個(gè)“硅殺手錯(cuò)誤”。使用實(shí)際流量發(fā)現(xiàn)了兩個(gè)漏洞;如果該公司單獨(dú)使用模擬,則不會(huì)發(fā)現(xiàn)其他四個(gè)。該團(tuán)隊(duì)在12個(gè)月內(nèi)開(kāi)發(fā)了該芯片,在磁帶輸出前四個(gè)月完成了硬件和軟件集成。

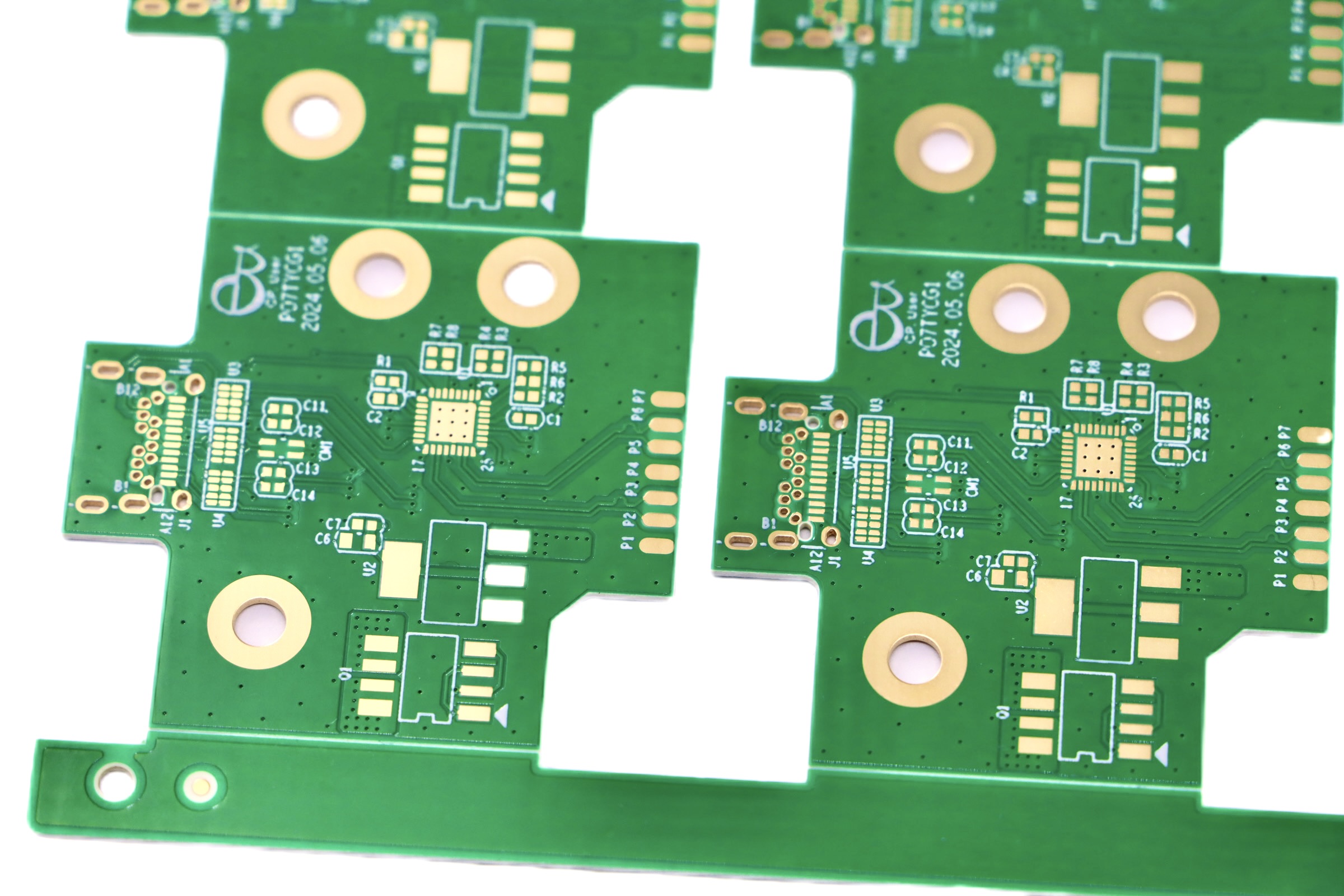

隨著芯片尺寸和復(fù)雜性的增加,設(shè)計(jì)團(tuán)隊(duì)需要高性能用于在整個(gè)系統(tǒng)環(huán)境中驗(yàn)證新設(shè)計(jì)邏輯的工具。仿真提供了開(kāi)發(fā)中硅的物理模型以及用于識(shí)別設(shè)計(jì)缺陷的全面,集成的邏輯調(diào)試環(huán)境。最重要的是,仿真使用戶(hù)能夠?qū)⒎抡婀璨迦胝鎸?shí)的PCB,并在設(shè)計(jì)周期的早期使用真實(shí)的外部激勵(lì)調(diào)試系統(tǒng)環(huán)境中的硬件和軟件。真正的系統(tǒng)級(jí)驗(yàn)證可以在收到第一塊芯片之前很久就可以驗(yàn)證PCB,芯片和軟件,從而大大縮短產(chǎn)品上市時(shí)間并提高質(zhì)量。

-

pcb

+關(guān)注

關(guān)注

4407文章

23883瀏覽量

424458 -

華強(qiáng)pcb線(xiàn)路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44647

發(fā)布評(píng)論請(qǐng)先 登錄

7個(gè)常見(jiàn)的DFM問(wèn)題,及其對(duì)PCB制造的影響

縮短啟動(dòng)時(shí)間的定制支持成為采用關(guān)鍵——持續(xù)選用Silex希來(lái)科無(wú)線(xiàn)模塊逾十年

如何縮短電能質(zhì)量在線(xiàn)監(jiān)測(cè)裝置的抗干擾能力驗(yàn)證時(shí)間?

EMC電路怎么整改:如何縮短整改周期的實(shí)戰(zhàn)案例

高頻PCB的制造工藝是怎樣的?

怎樣選擇適合的數(shù)據(jù)校驗(yàn)系統(tǒng)時(shí)間同步硬件?

亞馬遜:調(diào)用訂單退款A(yù)PI自動(dòng)化處理售后請(qǐng)求,縮短用戶(hù)等待時(shí)間

Cadence攜手NVIDIA革新功耗分析技術(shù)

PCB制造商能否用盲孔顯微鏡大幅縮短NPI周期?

從火場(chǎng)到指揮部:云翎智能如何用無(wú)線(xiàn)自組網(wǎng)縮短森林救援響應(yīng)時(shí)間

借助Cadence工具簡(jiǎn)化PCB設(shè)計(jì)流程

9160 gps 定位需要多長(zhǎng)時(shí)間呢?

Altium Designer AD 24 軟件安裝包下載

【Simcenter FLOEFD】利用完全嵌入CAD的CFD軟件,幫助設(shè)計(jì)師盡早評(píng)估流體流動(dòng)和傳熱,從而縮短開(kāi)發(fā)時(shí)間

Pcb怎樣縮短上市時(shí)間

Pcb怎樣縮短上市時(shí)間

評(píng)論