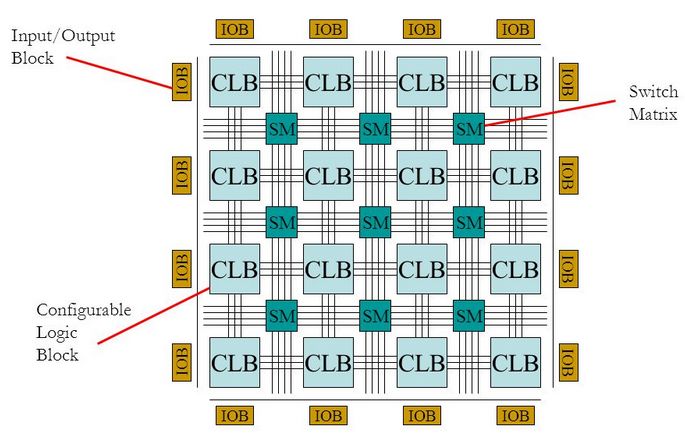

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它作為專用集成電路(ASIC)領域中的一種半定制電路而出現,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。主要用于信號處理及各類高速模擬仿真。

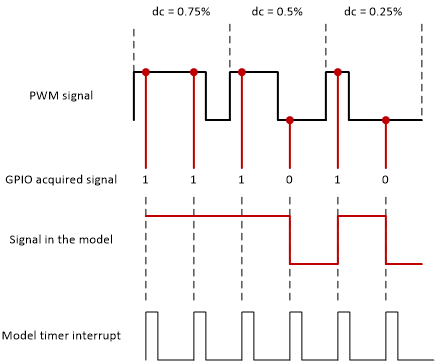

以PWM信號的捕獲為例,說明FPGA與CPU(不考慮芯片專用外設)在處理上的差異。當CPU通過GPIO對PWM信號采樣時,受限于CPU的運算周期,無法做到高速的采集,獲得的信號與原始信號有較大偏差,并計算出錯誤的占空比:

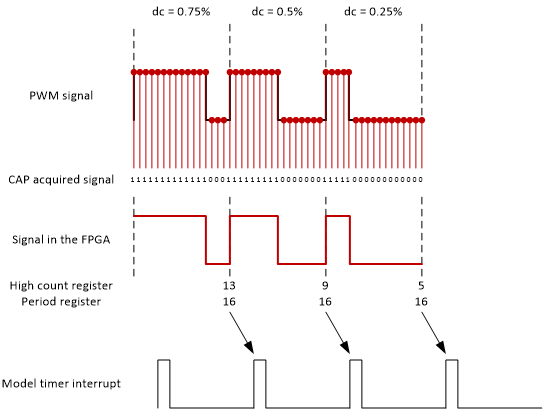

采用FPGA這種“硬電路”的方式采集信號,可以有效獲得信號的信息,誤差取決于采樣周期(如100MHz下約為10ns):

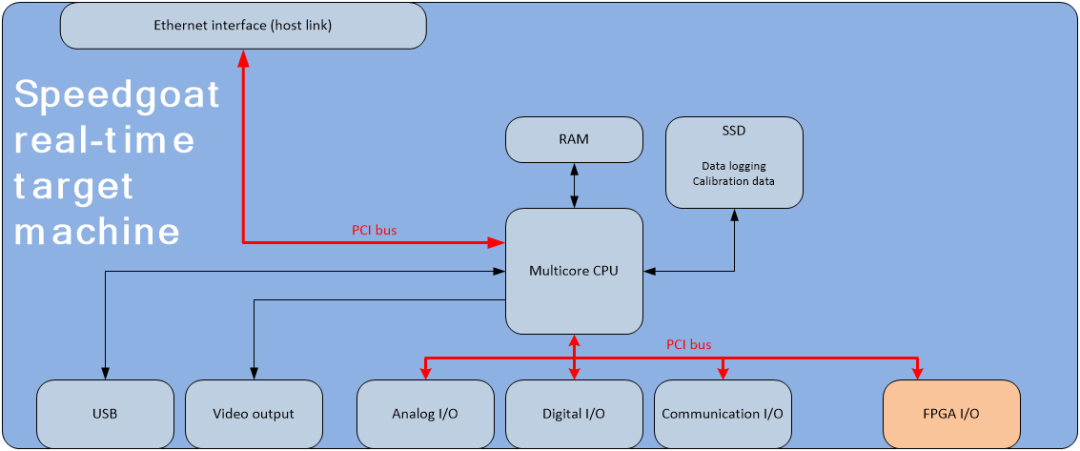

對于實時仿真而言,模型的計算只需要占空比信息即可,因此FPGA可以作為系統的“協處理器”存在,負責信號處理或高動態性部分模型運算,并將結果與CPU交互:

FPGA算法開發

FPGA的開發與傳統CPU、DSP的開發有很大不同。FPGA以并行運算為主,以硬件描述語言HDL來實現。開發者需具備較強的數字電路知識及邏輯思維能力。

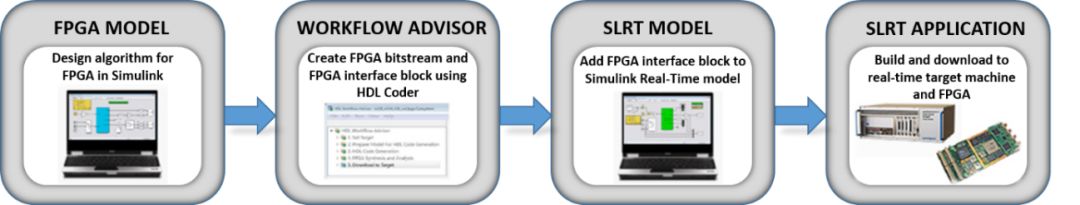

MATLAB/Simulink平臺的HDL Coder工具箱,有效的降低FPGA算法開發的難度;使工程師只需具備基礎知識即可在Simulink環境中搭建FPGA算法,并最終部署在Speedgoat或自己的FPGA平臺上。以Speedgoat平臺為例,基本步驟如下:

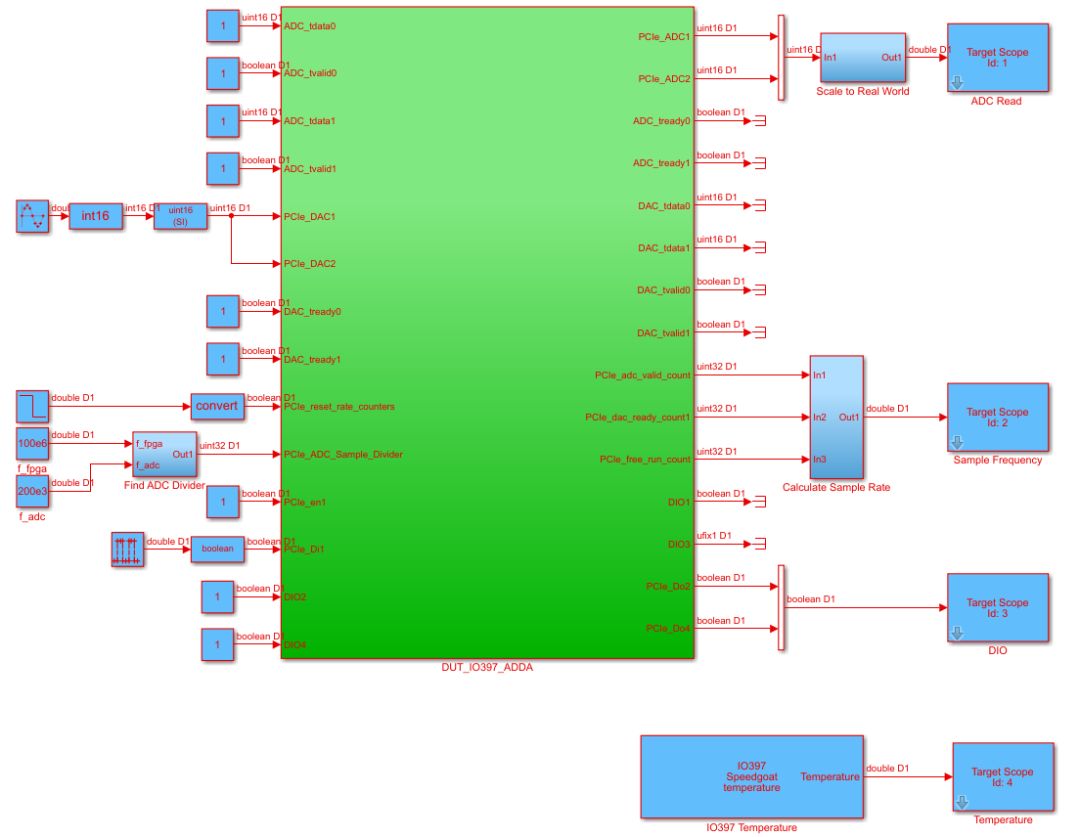

1. Simulink環境中搭建算法模型

開發者可以使用Simulink環境中的HDL Coder/DSP System Toolbox/Communication System Toolbox/ Vision HDL Toolbox等工具箱開發算法,并將算法放置在Subsystem內,仿真調試。Simulink環境支持以單精度浮點的方式開發FPGA算法,大大降低開發難度。

2. HDL Workflow Advisor

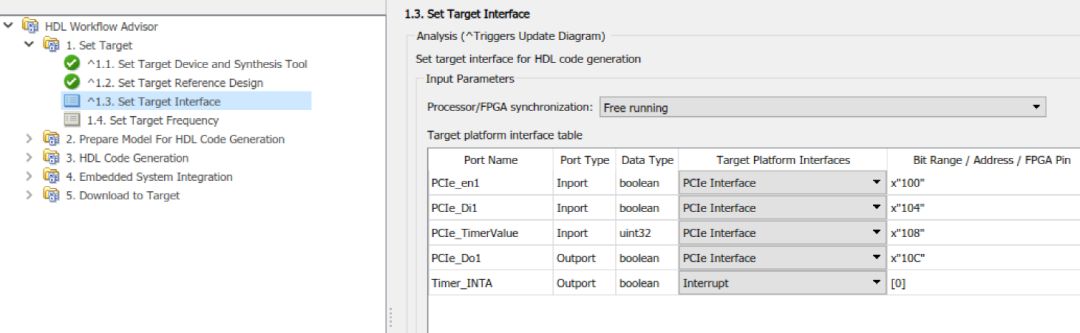

在Subsystem上右鍵選擇HDL Workflow Advisor,并在彈出的界面中依次設置FPGA板卡、芯片主頻,以及Subsystem inport和outport與硬件板卡IO通道的映射關系:

依次完成Workflow Advisor后續的task。HDL Workflow Advisor會完成模型檢查、HDL代碼生成、綜合、分析、映射等工作(需要Xilinx相關軟件,僅在后臺調用)。在此過程中,依據設置,HDL Coder可以完成Delay Balance,關鍵路徑尋找、代碼模型鏈接等功能。

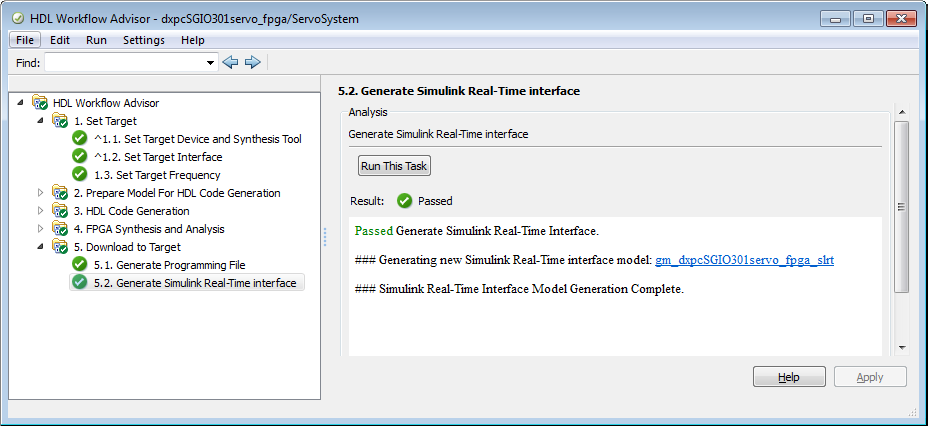

最終HDL Workflow Advisor可以生成一個接口模型,取代原先的算法Subsystem:

3. 編譯下載運行

FPGA模型部分編譯完,進一步完成整個模型的編譯,生成可執行程序下載到Speedgoat硬件上,系統會自動區分CPU和FPGA,并配置兩者間的通訊。

完整的流程如下:

詳細流程可參見HDL Coder工具箱的幫助文檔及Speedgoat相應幫助文檔。

在不遠的將來,MATLAB將完善物理模型對HDL代碼生成的支持。屆時物理模型在完成離線仿真后,可直接遷移到Speedgoat實時仿真平臺,無縫過渡到基于FPGA的半實物仿真測試階段,這對于電氣、電力電子領域有重要的意義。

Speedgoat FPGA解決方案

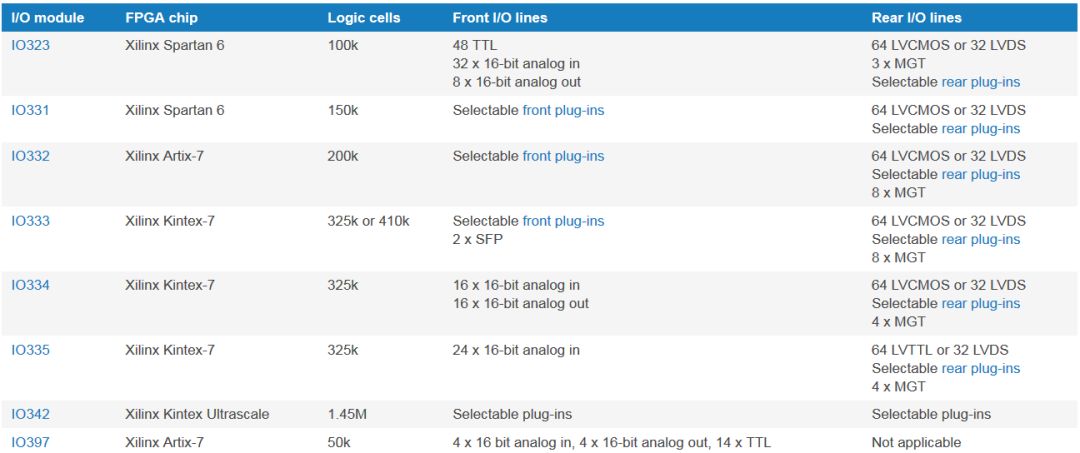

基于HDL Coder的模型化算法開發基礎上,Speedgoat針對不同的應用領域,提供了大量的可編程FPGA硬件模塊:

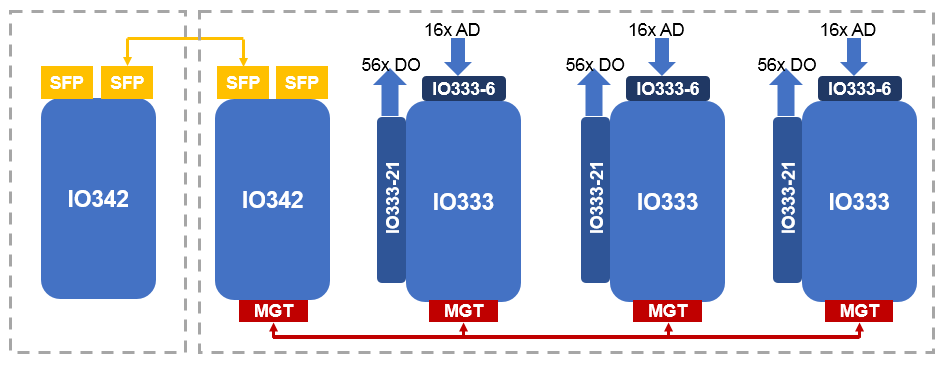

各模塊具備不同的IO通道和芯片資源,完全支持HDL Coder的模型化算法開發。當單FPGA模塊資源不夠時,可通過Xilinx Aurora協議,將彼此直接連接,組成更大規模的FPGA“計算集群”:

-

處理器

+關注

關注

68文章

20255瀏覽量

252344 -

FPGA

+關注

關注

1660文章

22412瀏覽量

636402 -

芯片

+關注

關注

463文章

54010瀏覽量

466173

發布評論請先 登錄

Aumovio案例研究 | 軟件即產品(SWaap)背景下的模型系統工程與閉環系統驗證

思爾芯原型驗證系統助力昆明湖V2成功啟動GUI OpenEuler

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

25年11月上海FPGA算法實現與應用技術高級研修分享

西門子 Veloce CS 助力 Arm Neoverse 計算子系統驗證與確認

基于FPGA實現FOC算法之PWM模塊設計

基于FPGA的壓縮算法加速實現

綠氫系統 PEM 電解槽直流接入仿真驗證深度解析

西門子桌面級原型驗證系統Veloce proFPGA介紹

新思科技硬件加速驗證技術日即將來襲

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

技術分享 | AVM合成數據仿真驗證方案

如何利用Speedgoat 系統驗證 FPGA 算法的方法介紹

如何利用Speedgoat 系統驗證 FPGA 算法的方法介紹

評論