11月20日消息,華爾街日報發布文章稱,科技產品下一個重大突破將在芯片堆疊領域出現。

Apple Watch采用了先進的的3D芯片堆疊封裝技術

作為幾乎所有日常電子產品最基礎的一個組件,微芯片正出現一種很有意思的現象。通常又薄又平的微芯片,如今卻堆疊得像薄煎餅那樣,由二維變成三維——給電子設備帶來重大的影響。

芯片設計師們發現這種堆疊方式可在性能、能耗和功能上帶來各種意想不到的好處。

沒有這種技術,蘋果智能手表Apple Watch也就無法做出來,三星最先進的固態存儲器、來自英偉達和谷歌的人工智能系統和索尼超級快速的新型相機也不例外。

這種3D堆疊類似于城市規劃。沒有它的話,隨著產品需要內置更多的零部件,電路板上的微芯片會不斷延伸,微芯片之間的距離會越隔越遠。然而,一旦開始對芯片進行堆疊,你就能形成一個硅制“城市”,里面的一切會變得更加鄰近。

從物理學角度來看,這種設計的優勢顯而易見:當電子需要通過銅線行進更長的距離的時候,會消耗更多的能量,產生熱量,同時也減少頻寬。ARM旗下微芯片設計公司ARM Research未來硅技術主管格雷格·耶里克(Greg Yeric)指出,堆疊式芯片更加高效,產生較少的熱量,能夠以光速在短得多的互連通道里進行通信。

Apple Watch Series 1的Apple S1芯片X光圖

雖然3D堆疊芯片背后的原理簡單明了,但要制造起來可不容易。耶里克說道,該技術概念于1960年代被首次提出,此后零星地出現在一些高端應用當中,比如軍用硬件。

然而,TechInsights微芯片研究公司分析師辛金·迪克森-沃倫(Sinjin Dixon-Warren)指出,來自大多數大型芯片廠商(AMD、英特爾、蘋果、三星和英偉達)以及Xilinx等小型的專業公司的堆疊式芯片產品,才出現了五年左右。為什么大家要這樣做呢?因為工程師們開始找不到其它的辦法來讓芯片有更好的表現。

堆疊式芯片通常是其它蜷縮起來的芯片的“封裝”的一部分。除了節省空間以外,這讓廠商們能夠(通過不同的制造工藝)打造許多不同的芯片,然后多多少少將它們粘合在一起。“3D堆疊式封裝”的做法不同于頻繁用于手機的“系統級芯片”做法,后者是將所有不同的手機部件蝕刻在單一的硅片上。

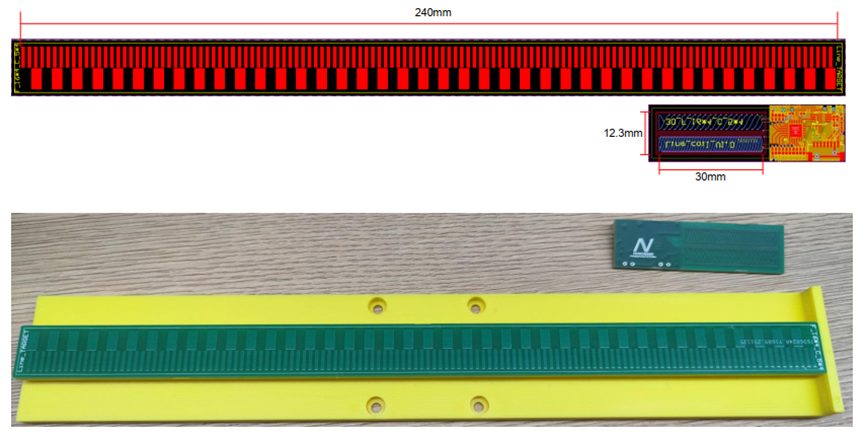

迪克森-沃倫稱,從第一代開始,Apple Watch就由最先進的3D堆疊式芯片封裝之一驅動。在該智能手表中,30種不同的芯片密封在一個塑料包層里面。他說,為了節省空間,存儲芯片堆疊在邏輯電路上面。要是沒有芯片堆疊技術,該手表的設計就無法做得如此緊湊。

蘋果的芯片只是堆疊成兩層高,而三星卻做出了名副其實的硅制“高樓大廈”。三星用于手機、相機和筆記本數據存儲的V-NAND閃存足足堆疊了64層芯片。三星也剛剛宣布,未來的版本將會有96層。

英偉達針對人工智能打造的Volta微處理器,GPU上堆疊了八層的高頻寬存儲器

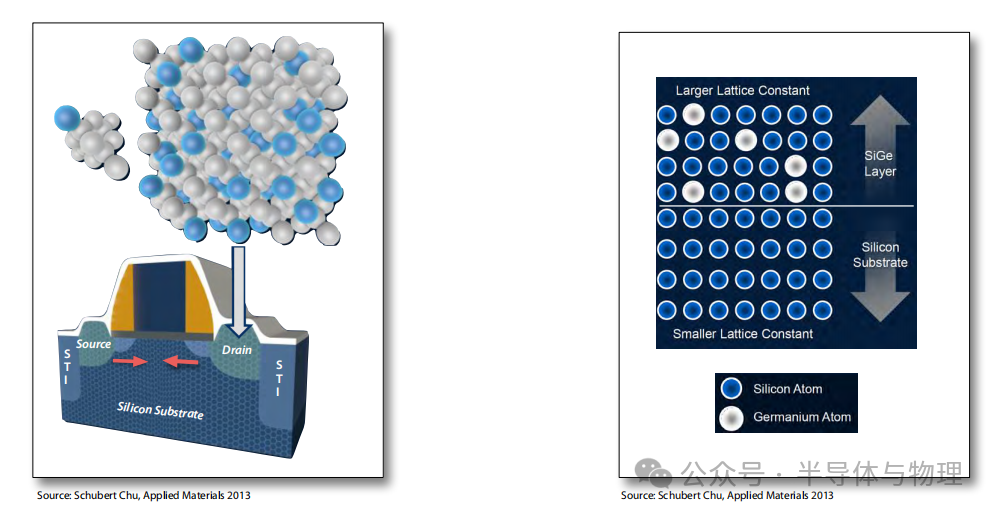

存儲是芯片堆疊技術的一項自然而然的應用,因為它解決了長久以來一直困擾芯片設計師的一個問題:給從iPad到超級計算機的任何設備增加更多的核心,并不能換來所期望的速度提升,因為邏輯電路之間的通信延遲和所需要的存儲能力。而將存儲組件直接堆疊在芯片上,則可以讓二者之間的連接路徑縮短。

英偉達硬件工程高級副總裁布萊恩·凱萊赫(Brian Kelleher)表示,那正是公司針對AI打造的Volta微處理器的運作原理。通過直接在GPU上面堆疊八層的高頻寬存儲器,這些芯片在處理效率上創造了新的紀錄。

“我們在電力上是受限的,”凱赫勒說,“我們能夠從存儲系統騰出的任何電力,都可以用在計算上。”

芯片堆疊也帶來了一些全新的功能。有的手機攝像頭將圖像傳感器直接疊加在處理圖像的芯片上面。額外的速度意味著,它們能夠對照片進行多次曝光,并將其融合在一起,在昏暗的場景里捕捉到更多的光線。

三星的64層V-NAND垂直芯片,擁有更大的數據存儲容量和更快的處理速度

來自索尼的原型攝像頭通過使用三層而非兩層芯片更進一步——包括圖像傳感器、存儲器和邏輯電路,實現每秒最高1000幀的效果。這種做法的作用是,光觸達圖像傳感器,數據直接進入存儲器,接著進行實時處理。除了在低光照條件下取得更高的能見度以外,這還可以用于拍攝超慢動作的視頻,單幀凝固快速移動的物體。

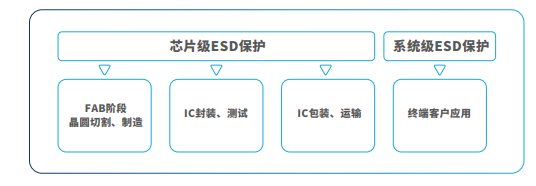

目前,要將3D微芯片推向更多的電子設備,還需要耗費巨大的資源去解決一些障礙。

耶里克表示,首先,3D芯片誕生不久,用于堆疊的設計工具進化還不充分。在簡單的設計工具——類似于用于平整芯片的那些工具——變得廣為普及以前,堆疊式芯片仍將只有擁有頂尖工程人才的企業能夠制造出來。

另一個問題在于,制造商們仍在學習如何可靠地在物理上相互堆疊和連接芯片。這意味著有的制造工藝成品率會相對較低。

不過,迪克森-沃倫指出,3D堆疊式芯片的普及非常快速,它們也必然會成為行業主流。10年前,該技術幾乎僅僅存在于高校實驗室;五六年前,還難以找到它的商業化案例。但它如今如雨后春筍般涌現,出現在各類的應用上,如網絡化、高性能計算和Apple Watch等高端可穿戴設備。據知名電子產品拆解網站iFixit的CEO凱爾·韋恩斯(Kyle Wiens)稱,它也出現在iPhone X的“大腦”當中。

在ARM的耶里克看來,最終3D芯片應該會讓我們的可穿戴產品變得跟體積更大的設備那么強大,會讓它們能夠連續運行數天時間,即便它們布滿了傳感器。“舉例來說,如果有朝一日你的手表變得能夠檢查你的血糖水平,我不會感到驚訝。”他說道。

讓芯片從二維變成三維,只是個開始。不久以后,芯片層將會通過光而非電流來通信。在更遙遠的未來,隨著我們用擁有前所未見的處理性能的閃亮晶體替換電路板,它們將會完全擺脫硅——可能轉向人造鉆石。

-

芯片

+關注

關注

463文章

54017瀏覽量

466301 -

圖像傳感器

+關注

關注

68文章

2076瀏覽量

132217

發布評論請先 登錄

不同于HBM垂直堆疊,英特爾新型內存ZAM技術采用交錯互連拓撲結構

從3D堆疊到二維材料:2026年芯片技術全面突破物理極限

真空共晶爐/真空焊接爐——堆疊封裝

東芝硬盤率先完成 12 盤片堆疊技術驗證

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

【「算力芯片 | 高性能 CPU/GPU/NPU 微架構分析」閱讀體驗】+NVlink技術從應用到原理

從焊錫膏到3D堆疊:材料創新如何重塑芯片性能規則?

關于芯片堆疊技術的分析介紹和應用

關于芯片堆疊技術的分析介紹和應用

評論