Altium designer PCB設計當中相同網絡的鋪銅無法連接的解決辦法 在我們進行pcb設計鋪銅的時候我們經常會發現,相同的網絡居然沒辦法鋪銅在一起,這個是啥原因呢,不同網絡避開可以理解,為啥相同網絡也避開呢?那么今天我們來分析分下出現這種現象的原因吧!

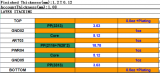

(1)確認是否為同一網絡; (2)敷銅屬性框中選擇“Pour Over All Same Net Objects”; 意思是相同的網絡一起鋪銅(絕大多數的原因在這里) (3)查看規則管理器,銅皮間距規則是否設置過大; (4)查看規則管理器中銅皮連接方式是否選擇“No Connect”,如果是請一一的更改,如圖1所示。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4415文章

23933瀏覽量

425699 -

altium

+關注

關注

48文章

1012瀏覽量

122292 -

可制造性設計

+關注

關注

10文章

2066瀏覽量

16492 -

華秋DFM

+關注

關注

20文章

3515瀏覽量

6511 -

可制造性設計分析

+關注

關注

4文章

866瀏覽量

6400

發布評論請先 登錄

相關推薦

熱點推薦

07. 如何在Allegro中設置可以走線但不能鋪的銅區域?| 芯巧Allegro PCB 設計小訣竅

背景介紹:我們在進行PCB設計時,經常需要繪制一些禁止鋪銅但是允許走線的區域,如果我們直接使用Route Keepout繪制的話,雖然可以實現在此區域內禁止鋪

發表于 04-09 17:23

01. 如何在 Allegro 中快速區別不同網絡?| 芯巧Allegro PCB 設計小訣竅

Allegro PCB設計小訣竅系列--如何在Allegro中快速區別不同網絡背景介紹:Allegro PCB設計工具可以通過高亮操作將選中的網絡點亮,但是當我們的布線非常密集時,是不

發表于 04-03 15:51

射頻PCB的“隱形殺手”:90%的工程師都忽視的鋪銅細節!

23年PCBA一站式行業經驗PCBA加工廠家今天為大家講講針對高頻(射頻)電路,鋪銅時需要特別注意哪些特殊規則和屏蔽措施。針對高頻/射頻(RF)電路,鋪銅的核心思路是:優先保證“參考地

高速PCB工程師必看:用仿真三步法,讓鋪銅從“隱患”變“保障”

23年PCBA一站式行業經驗PCBA加工廠家今天為大家講講在高速PCB設計中,如何通過仿真工具驗證鋪銅對信號完整性的影響。在高速PCB設計中,鋪

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+設計實現之路

設計,Altium Designer提供了原理圖庫和PCB庫,從而可以快速展開設計。

對于任何先進的設計工具來說,它們都會給設計者提供極大的便利,然而用戶的需求是千差萬別的,也是毫無止境的。為此,在各類

發表于 02-23 23:52

從設計階段排查預防PCB短路

溯源:PCB設計階段埋下的雷

案例一:不同網絡銅皮導通

案例解釋:左側孔在第二層與電源(-) 網絡連接,而右側孔網絡屬性是電源(+) ,并采用了手動

發表于 01-23 13:55

[Fortior Tech] [FU6832S 演示板 Gerber 文件] [Altium Designer]幫助

我從Fortior Tech獲得了FU6832S的電路圖和PCB文件。我使用Altium Designer打開這些文件并生成Gerber文件。但在3D模型中無法看到元件(電阻、電容),

發表于 06-04 17:07

Allegro Skill布線功能之切線、切銅、連接布線介紹

FanySkill的“切線/截銅”功能為PCB設計提供了高效的線路調整方案,可截斷走線或鋪銅和恢復走線連接。當需要微調已完成布線的器件位置時

Altium Designer 23 軟件下載

AD 22 到AD 23之間各個子版本更新的細節,有興趣的小伙伴可以訪問嗷疼家的官網專題頁面了解:https://www.altium.com/altium-designer/whats-new通過

發表于 05-22 16:46

?6次下載

Altium Designer PCB設計高級進階

對PCB設計的高級進階的內容進行相關的介紹

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

發表于 04-27 16:40

建議收藏,這31條PCB設計布線技巧

直接相連,需要先連接出焊盤之后再進行連接,直接連接容易在手工焊接時連錫。 6、對于小CHIP器件,要注意布線的對稱性,保持2端布線線寬一致,如一個管腳鋪

發表于 04-19 10:46

Altium Designer中PCB設計規則設置

在使用 Altium Designer 進行PCB設計時,除了電氣間距(Clearance)等基礎規則外, 導線寬度、阻焊層、內電層連接、銅皮敷設等規則也同樣重要 。這些設置不僅影響布

Altium designer PCB設計當中相同網絡的鋪銅無法連接的解決辦法

Altium designer PCB設計當中相同網絡的鋪銅無法連接的解決辦法

評論