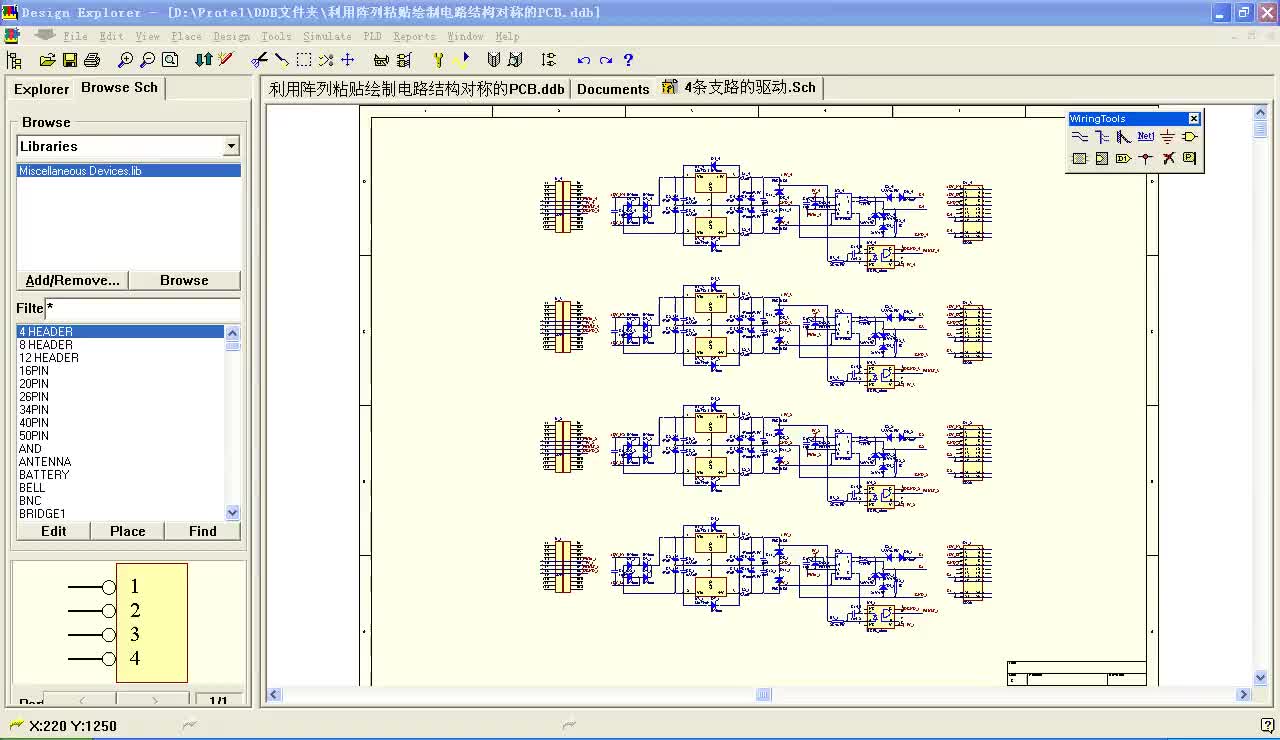

Mentor的autoactive RE由收購得來的veribest發展而來,是業界第一個無網格,任意角度布線器。

眾所周知,對于球柵陣列,COB器件,無網格,任意角度布線器是解決布通率的關鍵。

在最新的autoactive RE中,新增添了推擠過孔,銅箔,REROUTE等功能,使它應用更方便。另外,他支持高速布線,包括有時延要求信號布線和差分對布線。

61、Mentor的PCB設計軟件對差分線隊的處理又如何?

Mentor軟件在定義好差分對屬性后,兩根差分對可以一起走線,嚴格保證差分對線寬,間距和長度差,遇到障礙可以自動分開,在換層時可以選擇過孔方式。

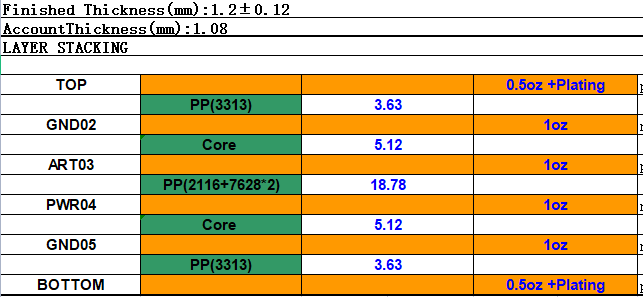

62、在一塊12層PCb板上,有三個電源層2.2v,3.3v,5v,將三個電源各作在一層,地線該如何處理?

一般說來,三個電源分別做在三層,對信號質量比較好。因為不大可能出現信號跨平面層分割現象。跨分割是影響信號質量很關鍵的一個因素,而仿真軟件一般都忽略了它。

對于電源層和地層,對高頻信號來說都是等效的。在實際中,除了考慮信號質量外,電源平面耦合(利用相鄰地平面降低電源平面交流阻抗),層疊對稱,都是需要考慮的因素。

63、PCB在出廠時如何檢查是否達到了設計工藝要求?

很多PCB廠家在PCB加工完成出廠前,都要經過加電的網絡通斷測試,以確保所有聯線正確。同時,越來越多的廠家也采用x光測試,檢查蝕刻或層壓時的一些故障。

對于貼片加工后的成品板,一般采用ICT測試檢查,這需要在PCB設計時添加ICT測試點。如果出現問題,也可以通過一種特殊的X光檢查設備排除是否加工原因造成故障。

64、“機構的防護”是不是機殼的防護?

是的。機殼要盡量嚴密,少用或不用導電材料,盡可能接地。

65、在芯片選擇的時候是否也需要考慮芯片本身的esd問題?

不論是雙層板還是多層板,都應盡量增大地的面積。在選擇芯片時要考慮芯片本身的ESD特性,這些在芯片說明中一般都有提到,而且即使不同廠家的同一種芯片性能也會有所不同。設計時多加注意,考慮的全面一點,做出電路板的性能也會得到一定的保證。但ESD的問題仍然可能出現,因此機構的防護對ESD的防護也是相當重要的。

66、在做pcb板的時候,為了減小干擾,地線是否應該構成閉和形式?

在做PCB板的時候,一般來講都要減小回路面積,以便減少干擾,布地線的時候,也不 應布成閉合形式,而是布成樹枝狀較好,還有就是要盡可能增大地的面積。

67、如果仿真器用一個電源,pcb板用一個電源,這兩個電源的地是否應該連在一起?

如果可以采用分離電源當然較好,因為如此電源間不易產生干擾,但大部分設備是有具體要求的。既然仿真器和PCB板用的是兩個電源,按我的想法是不該將其共地的。

68、一個電路由幾塊pcb板構成,他們是否應該共地?

一個電路由幾塊PCB構成,多半是要求共地的,因為在一個電路中用幾個電源畢竟是不太實際的。但如果你有具體的條件,可以用不同電源當然干擾會小些。

69、設計一個手持產品,帶LCD,外殼為金屬。測試ESD時,無法通過ICE-1000-4-2的測試,CONTACT只能通過1100V,AIR可以通過6000V。ESD耦合測試時,水平只能可以通過3000V,垂直可以通過4000V測試。CPU主頻為33MHZ。有什么方法可以通過ESD測試?

手持產品又是金屬外殼,ESD的問題一定比較明顯,LCD也恐怕會出現較多的不良現象。如果沒辦法改變現有的金屬材質,則建議在機構內部加上防電材料,加強PCB的地,同時想辦法讓LCD接地。當然,如何操作要看具體情況。

70、設計一個含有DSP,PLD的系統,該從那些方面考慮ESD?

就一般的系統來講,主要應考慮人體直接接觸的部分,在電路上以及機構上進行適當的保護。至于ESD會對系統造成多大的影響,那還要依不同情況而定。干燥的環境下,ESD現象會比較嚴重,較敏感精細的系統,ESD的影響也會相對明顯。雖然大的系統有時ESD影響并不明顯,但設計時還是要多加注意,盡量防患于未然。71、PCB設計中,如何避免串擾?

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號沿的變化(轉換率)越快,產生的串擾也就越大。空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。耦合電感電容產生的前向串擾和反向串擾同時存在,并且大小幾乎相等,這樣,在受害網絡上的前向串擾信號由于極性相反,相互抵消,反向串擾極性相同,疊加增強。

串擾分析的模式通常包括默認模式,三態模式和最壞情況模式分析。默認模式類似我們實際對串擾測試的方式,即侵害網絡驅動器由翻轉信號驅動,受害網絡驅動器保持初始狀態(高電平或低電平),然后計算串擾值。這種方式對于單向信號的串擾分析比較有效。三態模式是指侵害網絡驅動器由翻轉信號驅動,受害的網絡的三態終端置為高阻狀態,來檢測串擾大小。這種方式對雙向或復雜拓樸網絡比較有效。最壞情況分析是指將受害網絡的驅動器保持初始狀態,仿真器計算所有默認侵害網絡對每一個受害網絡的串擾的總和。這種方式一般只對個別關鍵網絡進行分析,因為要計算的組合太多,仿真速度比較慢。

72、導帶,即微帶線的地平面的鋪銅面積有規定嗎?

對于微波電路設計,地平面的面積對傳輸線的參數有影響。具體算法比較復雜(請參閱安杰倫的EESOFT有關資料)。而一般PCB數字電路的傳輸線仿真計算而言,地平面面積對傳輸線參數沒有影響,或者說忽略影響。

73、在EMC測試中發現時鐘信號的諧波超標十分嚴重,只是在電源引腳上連接去耦電容。在PCB設計中需要注意哪些方面以抑止電磁輻射呢?

EMC的三要素為輻射源,傳播途徑和受害體。傳播途徑分為空間輻射傳播和電纜傳導。所以要抑制諧波,首先看看它傳播的途徑。電源去耦是解決傳導方式傳播,此外,必要的匹配和屏蔽也是需要的。

74、采用4層板設計的產品中,為什么有些是雙面鋪地的,有些不是?

鋪地的作用有幾個方面的考慮:1,屏蔽;2,散熱;3,加固;4,PCB工藝加工需要。所以不管幾層板鋪地,首先要看它的主要原因。

這里我們主要討論高速問題,所以主要說屏蔽作用。表面鋪地對EMC有好處,但是鋪銅要盡量完整,避免出現孤島。一般如果表層器件布線較多,

很難保證銅箔完整,還會帶來內層信號跨分割問題。所以建議表層器件或走線多的板子,不鋪銅。

75、對于一組總線(地址,數據,命令)驅動多個(多達4,5個)設備(FLASH,SDRAM,其他外設...)的情況,在PCB布線時,采用那種方式?

布線拓撲對信號完整性的影響,主要反映在各個節點上信號到達時刻不一致,反射信號同樣到達某節點的時刻不一致,所以造成信號質量惡化。一般來講,星型拓撲結構,可以通過控制同樣長的幾個stub,使信號傳輸和反射時延一致,達到比較好的信號質量。

在使用拓撲之間,要考慮到信號拓撲節點情況、實際工作原理和布線難度。不同的buffer,對于信號的反射影響也不一致,所以星型拓撲并不能很好解決上述數據地址總線連接到flash和sdram的時延,進而無法確保信號的質量;另一方面,高速的信號一般在dsp和sdram之間通信,flash加載時的速率并不高,所以在高速仿真時只要確保實際高速信號有效工作的節點處的波形,而無需關注flash處波形;星型拓撲比較菊花鏈等拓撲來講,布線難度較大,尤其大量數據地址信號都采用星型拓撲時。

附圖是使用Hyperlynx仿真數據信號在DDR——DSP——FLASH拓撲連接,和DDR——FLASH——DSP連接時在150MHz時的仿真波形。

可以看到,第二種情形,DSP處信號質量更好,而FLASH處波形較差,而實際工作信號時DSP和DDR處的波形

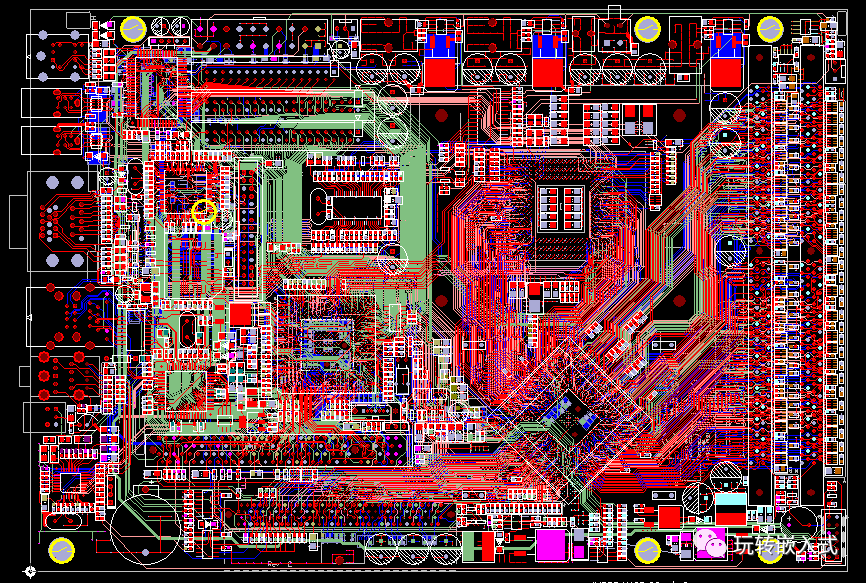

此主題相關圖片如下:

- 組圖PC(6397)

相關推薦

高速電路pcb設計方法與技巧 PCB布線技巧升級 高速信號篇

1432

1432

音頻接口電路的PCB設計方法與PCB設計注意事項

2051

2051

Mentor Graphics的PCB設計復用方法

1770

1770

電磁干擾的PCB設計方法

842

842選擇PCB元件的六大技巧

1373

1373PCB設計高速模擬輸入信號走線方法及規則

8394

8394

不同領域的高速PCB設計方法不同,工程師們你們真的掌握了嗎?

2841

2841PCB技術中的高速PCB設計中的屏蔽方法

789

789

PCB layout軟件該如何學習和PCB設計需要注意的問題

PCB設計

PCB設計培訓

PCB設計大賽——科技創造未來,PCB互連世界

PCB設計技巧

PCB設計軟件操作之兩種建立Match Group的方法

PCB設計軟件操作之兩種建立Match Group的方法

Cadence Concept HDL & Allegro原理圖與PCB設計

Cadence Concept HDL & Allegro原理圖與PCB設計

《Cadence Allegro實戰攻略與高速PCB設計》

【下載】Cadence Concept HDL & Allegro原理圖與PCB設計

【獲獎公示】PCB設計大賽獲獎名單出爐

【轉】PCB設計基礎知識 | PCB設計流程詳解

以藍牙音箱為案例的PCB設計軟件實操

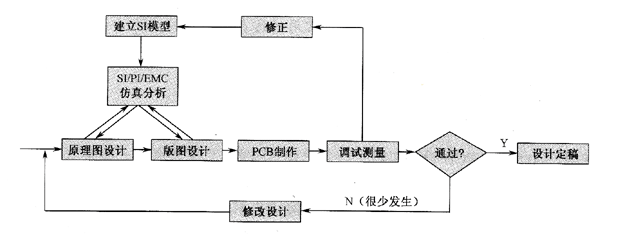

傳統的PCB設計方法

并行PCB設計的關鍵準則

電池充電器電路PCB設計方案

系列直播課,全新上線—— 基于STM32的4層車牌識別主板的PCB設計

資料下載-PCB設計技術方案專題

進行高頻PCB設計的技巧和方法有哪些?

高速PCB設計allegro軟件操作導入網表的兩種方法

高速pcb設計指南。

高速PCB設計方法

0

0PCB設計中20H規則的驗證方法

0

0PCB設計基礎教程手冊

0

0編寫PCB設計規則檢查器技巧

1019

1019PCB設計軟件坐標數據導出方法

1325

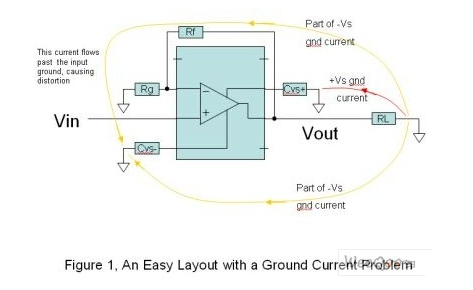

1325減少諧波失真的PCB設計方法

1041

1041

穩壓電源電路的PCB設計

498

498Cadence高速PCB設計

0

0抑制△I噪聲的PCB設計方法

0

0汽車音響導航系統中DDR高速信號的PCB設計

2975

2975

PCB設計方法和技巧

0

0教你學會減少諧波失真的PCB設計方法

0

0基于PROTEUS的電路及單片機設計與仿真(第二版)5-7章

0

0基于PROTEUS的電路及單片機設計與仿真(第二版)1-4章

0

0EAGLE電路原理圖與PCB設計方法及應用4-6章

0

0EAGLE電路原理圖與PCB設計方法及應用6-9章

0

0EAGLE電路原理圖與PCB設計方法及應用9-10章

0

0EAGLE電路原理圖與PCB設計方法及應用1-4章

0

0高速PCB電路板的信號完整性設計

0

0這些pcb設計方法能提升效率

5100

5100PCB設計中如何設置格點_pcb設計中格點的設置方法

11802

11802PCB設計方法與技巧,PCB Design Methods and Techniques

455

455常用的三種PCB板級信號完整性分析模型介紹

4447

4447LED開關電源的PCB設計方法解析

661

661制作PCB設計分孔圖的方法分享

3891

3891射頻電路的PCB設計技巧和方法解析

3714

3714

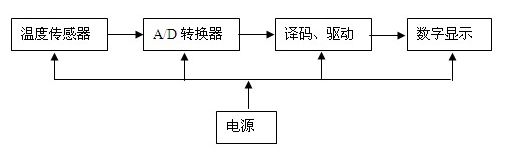

數顯溫度計的PCB設計方法解析

2086

2086

EMI和安全性:危害、風險以及避免的PCB設計方法

2547

2547開關電源的噪聲來源

3

3PCB設計問題的改善方法和技巧

1177

1177RF電路設計的常見問題 高頻PCB設計技巧和方法

469

469通過PCB設計降低PCBA成本的方法

1093

1093一個低阻抗的電源分配系統實現方法

273

273如何減少PCB雜散電容的影響

332

332基于信號完整性分析的PCB設計方法

191

191

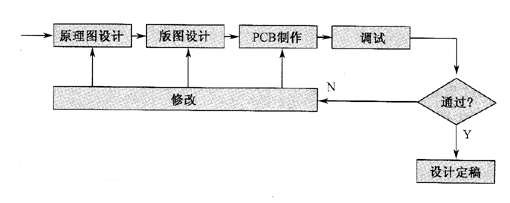

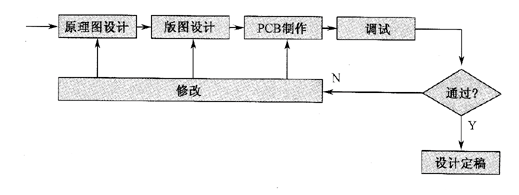

傳統的PCB設計方法

151

151

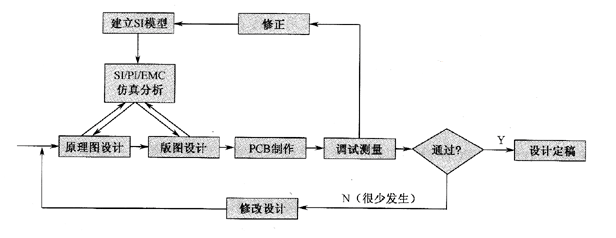

基于信號完整性分析的PCB設計方法

325

325

傳統的PCB設計方法

345

345

減少諧波失真的PCB設計方法

117

117

PCB設計阻抗不連續的原因及解決方法

86

86 電子發燒友App

電子發燒友App

評論