完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

每個(gè)模塊開始要注明文件名、功能描述、引用模塊、設(shè)計(jì)者、設(shè)計(jì)時(shí)間及版權(quán)信息等。...

首先說一下xapp1052模塊的組成結(jié)構(gòu):頂層模塊是xilinx_pci_exp_ep,在頂層模塊中包含pci_exp_64b_app和bmd_design兩個(gè)模塊,其中pci_exp_64b_app就是我們要介紹的重點(diǎn),而bmd_design則是實(shí)現(xiàn)PCIE協(xié)議的底層模塊。...

頻譜分析儀是一種測(cè)試測(cè)量設(shè)備,主要用于射頻和微波信號(hào)的頻域分析,包括測(cè)量信號(hào)的功率,頻率,失真等。它的性能主要是從實(shí)時(shí)帶寬,動(dòng)態(tài)范圍,靈敏度和功率測(cè)量準(zhǔn)確度等四個(gè)方面來評(píng)價(jià)。那么這么高的性能需要什么樣的電路才能完成呢?我們已經(jīng)迫不及待的想要拆開一臺(tái)頻譜分析儀來一探究竟啦! ...

在現(xiàn)實(shí)生活中或許有很多硬件愛好者會(huì)對(duì)支持高速金融服務(wù)器這種高端大氣上檔次的服務(wù)器十分好奇,也好奇實(shí)現(xiàn)這樣的一個(gè)金融交互池除了是只需要強(qiáng)大的軟件架構(gòu)以及軟件實(shí)現(xiàn)嗎?我們FPGA這樣的硬件是否可以為搭建這樣的服務(wù)器作出一些貢獻(xiàn)呢?SmartNIC fb4CGg3@VU PCIe 開發(fā)板告訴我們可以的,并...

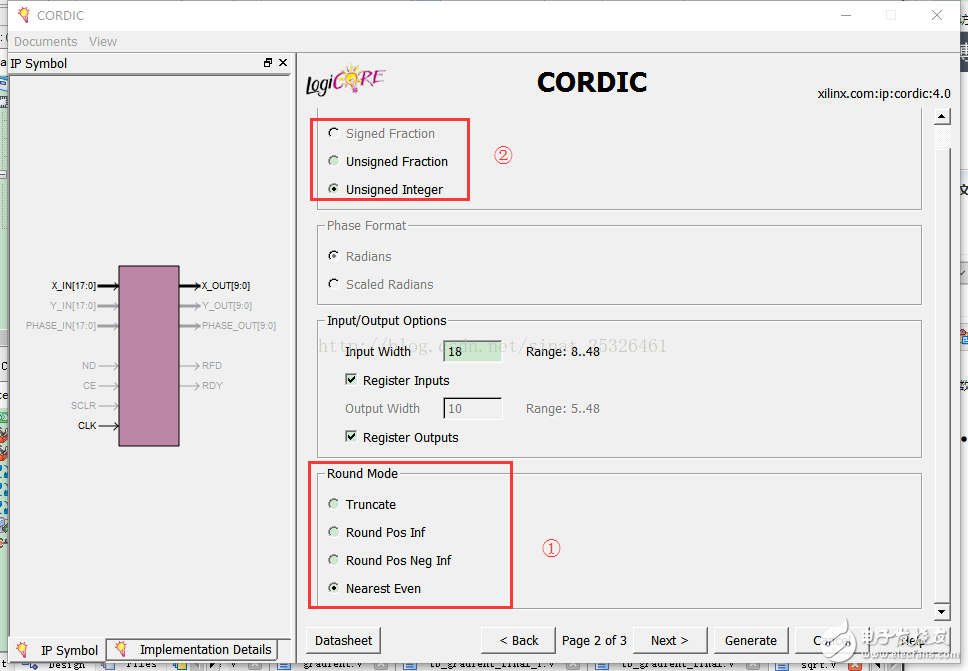

Round Pos Inf:四舍五入,+0.5之后四舍五入,在負(fù)數(shù)時(shí)和第三種有區(qū)別。...

FPGA 有一個(gè)響亮的別名——“萬能芯片”,它是一種能夠通過軟件更改、配置器件內(nèi)部連接結(jié)構(gòu)和邏輯單元,完成既定設(shè)計(jì)功能的數(shù)字集成電路。雖然FPGA問世的時(shí)間不長(zhǎng),但發(fā)展非常迅猛,遠(yuǎn)超出了業(yè)界的預(yù)想。...

代碼設(shè)計(jì)完成后,最好先使用開發(fā)工具進(jìn)行語法檢測(cè),之后進(jìn)行功能仿真,此處仿真不涉及時(shí)序上的延時(shí)。仿真工具首推ModelTech公司的ModelSim,也可以用ISE的Quartus 2進(jìn)行簡(jiǎn)單仿真。...

proc文件系統(tǒng)是用來提供內(nèi)核和進(jìn)程信息的虛擬文件系統(tǒng),使用內(nèi)核自動(dòng)生成的文件,加載完成一定要能查到很多信息才對(duì)。...

對(duì)于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復(fù)/置位和同步復(fù)位/置位。對(duì)普通邏輯設(shè)計(jì),同步復(fù)位和異步復(fù)位沒有區(qū)別,當(dāng)然由于器件內(nèi)部信號(hào)均為高有效,因此推薦使用高有效的控制信號(hào),最好使用高有效的同步復(fù)位。輸入復(fù)位信號(hào)的低有效在頂層放置反相器可以被吸收到IOB中。...

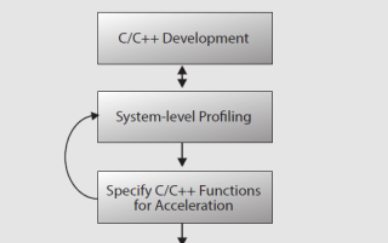

FPGA具有豐富的硬件計(jì)算單元以及分布式并行內(nèi)存,其他芯片只有非常有限的計(jì)算資源,比如CPU只有幾個(gè)高性能ALU,另外其他芯片一般使用一個(gè)共享內(nèi)存,在任何是有只能進(jìn)行一次的讀或者寫操作。...

物聯(lián)網(wǎng)(IoT)的規(guī)模和復(fù)雜性不斷上升,對(duì)主動(dòng)的強(qiáng)化安全措施的需求日益增加。僅利用軟件安全功能已經(jīng)不足以應(yīng)對(duì)已知的網(wǎng)絡(luò)威脅,更有效的方法是采用分層技術(shù)戰(zhàn)略,這種戰(zhàn)略以采用能夠提供IC級(jí)硬件可信根的新一代系統(tǒng)級(jí)芯片(SoC) FPGA開始。在此堅(jiān)實(shí)的基礎(chǔ)之上,應(yīng)采用可擴(kuò)展的解決方案,包括根據(jù)風(fēng)險(xiǎn)合適的...

該系統(tǒng)的監(jiān)控端采用了基于CortexA8系列的ARM處理器,該處理器同時(shí)兼顧了成本與性能的要求,可設(shè)計(jì)美觀的圖形化操作界面。該系統(tǒng)工作于BD2-B1和GPS-L1兩個(gè)頻點(diǎn),便攜性好,界面直觀,可通過按鍵或觸摸屏兩種方式操作,同時(shí)可隨時(shí)采集戶外復(fù)雜環(huán)境下的導(dǎo)航衛(wèi)星信號(hào),極大地提高了導(dǎo)航接收機(jī)的開發(fā)效率...

Xilinx 7系列FPGA的HP bank都支持DCI,目的是在高速單板信號(hào)傳輸中保持信號(hào)完整性,減少反射等因素影響,那么DCI是什么?digitally controlled impedance是DCI的縮寫,應(yīng)該也算上xilinx 在IO feature上的一項(xiàng)技術(shù)(這不是7系列才有的新技術(shù))...

項(xiàng)目設(shè)計(jì)初期會(huì)選型,工程師根據(jù)資源、IO、硬核、IP等選擇對(duì)應(yīng)型號(hào)的FPGA。功耗部分xilinx提供了XPE表格(Xilinx PowerEstimator),這個(gè)XPE支持zynq、目前也有各個(gè)系列的器件列表,包括最新的ultrascale + 。...

UFDM建議正確的HDL coding風(fēng)格來滿足目標(biāo)器件,討論時(shí)序約束和時(shí)序收斂。正確的IO約束,IO管腳分配和布局,物理約束,并提供了滿足時(shí)序收斂的技巧和讓FPGA工作快速穩(wěn)定的方法。...

在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time)不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時(shí)觸發(fā)器輸出端Q在有效時(shí)鐘沿之后比較長(zhǎng)的一段時(shí)間處于不確定的狀態(tài),在這段時(shí)間里Q端在0和1之間處于振蕩狀態(tài),而不是等于數(shù)據(jù)...

開發(fā)機(jī)器視覺系統(tǒng)通常需要大量的時(shí)間來設(shè)計(jì)能執(zhí)行所有重要圖像采集及處理功能的電子產(chǎn)品。通常需要兩年多的時(shí)間,這會(huì)給攝像機(jī)及系統(tǒng)制造商的上市進(jìn)程與產(chǎn)品規(guī)劃帶來不利影響。...

有限狀態(tài)機(jī)(Finite State Machine, FSM),根據(jù)狀態(tài)機(jī)的輸出是否與輸入有關(guān),可分為Moore型狀態(tài)機(jī)和Mealy型狀態(tài)機(jī)。Moore型狀態(tài)機(jī)輸出僅僅與現(xiàn)態(tài)有關(guān)和Mealy型狀態(tài)機(jī)不僅與現(xiàn)態(tài)有關(guān),也與輸入有關(guān),所以會(huì)受到輸入的干擾,可能會(huì)產(chǎn)生毛刺(Glith)的現(xiàn)象,所以我們通常...

介紹FPGA約束原理,理解約束的目的為設(shè)計(jì)服務(wù),是為了保證設(shè)計(jì)滿足時(shí)序要求,指導(dǎo)FPGA工具進(jìn)行綜合和實(shí)現(xiàn),約束是Vivado等工具努力實(shí)現(xiàn)的目標(biāo)。所以首先要設(shè)計(jì)合理,才可能滿足約束,約束反過來檢查設(shè)計(jì)能否滿足時(shí)序。主要涉及到xilinx vivado xdc約束語法,給出對(duì)應(yīng)的ISE ucf 語法...

隨著HEVC、AV1等更復(fù)雜算法的Codec份額逐步增長(zhǎng),實(shí)現(xiàn)高質(zhì)量視頻編解碼需要硬件支持,軟件的方式無論在服務(wù)器端和移動(dòng)端都非最佳的方案。FPGA專用芯片能夠降低延遲和成本。在NAB 2018大會(huì)上,資深多媒體技術(shù)咨詢師Jan Ozer對(duì)Ngcodec的CEO Oliver Gunasekara進(jìn)...