資料介紹

描述

什么是仲裁員?

仲裁器是硬件設計中非常常用的塊。

我想我可以在家里找到仲裁者的最好例子。當我的兩個孩子十幾歲時,我只有一輛車。在周五和周六晚上,通常會因為誰可以使用汽車而發生沖突。通常,由我來決定(仲裁者)誰得到了這輛車。這不是一件容易的事。(我仍然只有一輛車,正好我的孩子都不是十幾歲了,贊美主,他們有自己的車)。

硬件板沒有什么不同。至少在兩種情況下,多個用戶“需要”共享(且有價值且昂貴)的資源:

- 公共內存:在處理器和 FPGA 之間共享快速內存(即 DDR)的電路板是很常見的。顯然,記憶不能同時回答兩個高手。處理器和 FPGA 向仲裁器請求訪問內存的權限。即使它以非常高的速度同時完成,對于我們的感知,實際上,FPGA 和處理器必須輪流擁有內存。注意:這只是一個簡單的示例,因為還有許多其他應用程序甚至超過兩個“智能”設備(處理器、DSP、GPU、FPGA、ASIC)輪流訪問公共內存。

- 公共總線:很多時候多個主機(和從機)通過公共總線進行通信。從電氣角度來說,總線非常簡單。它只不過是一組銅連接或電線(有時帶有總線驅動器)。但是總線所有權很重要,因為兩個主機不可能同時擁有總線(多主機總線的示例:I2C、PCI)。如果兩個主機試圖同時“交談”,就會發生沖突,總線上的數據就會被破壞。

仲裁者是硬件的一部分,它決定誰可以在任何給定時間使用公共的、有價值的資源。然而,與足球仲裁器不同的是,VHDL 仲裁器永遠不會將其中一個設備從“游戲”中移除(好吧......幾乎永遠不會。在某些情況下,硬件仲裁器會決定一個設備表現不佳并決定將其從“游戲”中移除一個例子是可插拔卡訪問公共總線,可以在關鍵時刻拔掉,如果仲裁器沒有識別出故障,總線可能會卡在 - 現在丟失的 - 設備上)。

仲裁器從其客戶端接收兩種類型的信號:

- 請求:由想要擁有公共資源的每個設備聲明。可以同時斷言許多請求信號,就像許多設備請求擁有公共資源的許可一樣。另一方面,可以只有一個,甚至沒有斷言的請求信號。后者是在特定時刻沒有人需要共享資源的情況。

- Grant:由仲裁器斷言,每個master有一個grant信號。通常,在任何給定時間都只會斷言一個授權信號。

第一次實現 - 固定大小,固定優先級

我們將分析的第一個仲裁器具有三個請求輸入和三個授權輸出。它也有一個固定的主人優先權。master 編號越低,其優先級越高。該塊也有忙信號。總線仲裁僅在其處于非活動狀態時進行。如果總線已經被授權給代理,即使更高優先級的主機請求總線,當前事務也必須在仲裁器將總線授權給另一個主機之前完成。

生成授權信號的邏輯(在進程arbiter_pr上)非常簡單。如果第一個主控(主控 0)斷言請求,則它被授予授權。只有當主控 1 請求總線而主控 0 不請求總線時,它才會獲得授權。只有當主控 2 請求總線并且主控 0 和主控 1 都沒有請求總線時,它才會被授予授權。

gnt信號只有在總線不忙時才會改變。進程busy_pr和相關邏輯檢測忙信號的下降沿。在 busy 變為低電平后,所有授權信號都被取消斷言一個時鐘,然后選擇下一個總線主機的邏輯被激活。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector(2 downto 0);

busy : in std_logic;

-- outputs

gnt : out std_logic_vector(2 downto 0)

);

end arbiter;

architecture rtl of arbiter is

signal busy_d : std_logic := '0';

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk, rst)

begin

if (rst = '1') then

gnt <= (others => '0');

elsif (rising_edge(clk)) then

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

gnt(1) <= req(1) and not req(0);

gnt(2) <= req(2) and not (req(0) or req(1));

end if;

end if;

end process arbiter_pr;

end rtl;

gnt信號只有在總線不忙時才會改變。進程busy_pr和相關邏輯檢測忙信號的下降沿。在 busy 變為低電平后,所有授權信號都被取消斷言一個時鐘,然后選擇下一個總線主機的邏輯被激活。

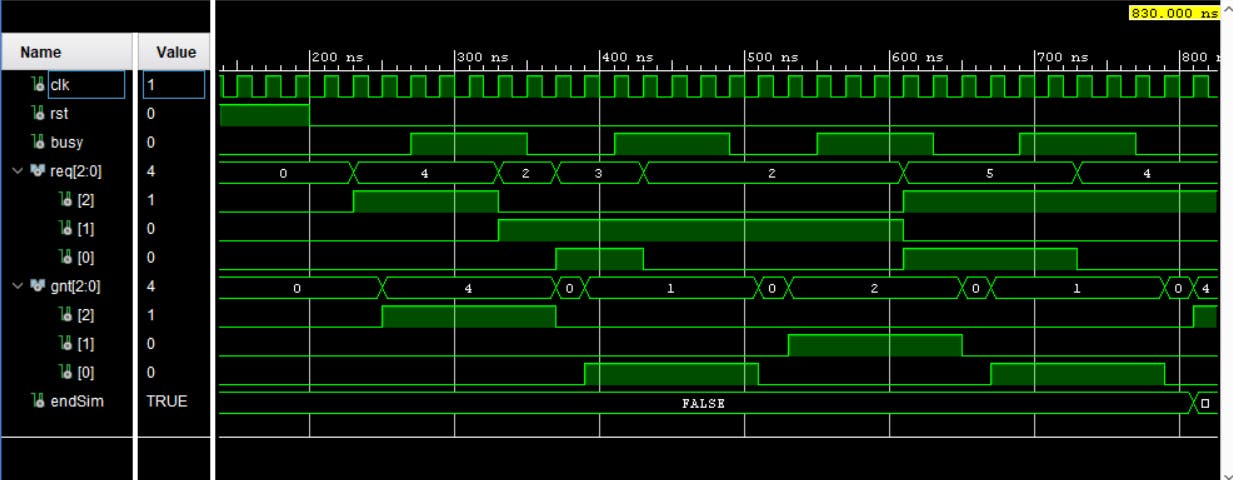

復位釋放后,沒有未完成的請求,因此仲裁器也不會斷言任何授權信號。稍后在模擬中,多個主機請求仲裁器的許可(請求已斷言)并根據其優先級獲得授權。

在 300 到 400ns 之間,主機“1”斷言其請求信號。兩個時鐘周期后,來自主機“0”的請求被置位。因此,即使 master '0' 稍后到達,當仲裁器可以自由分配總線時,它也會將其分配給 master '0'。

請注意,在gnt信號之間始終有一個“休息”時鐘。每個主機使用總線四個時鐘并放棄總線(這可以在忙信號的持續時間內看到)。

稍后,主機“2”和“0”都請求總線,正如預期的那樣,總線被授予主機“0”。

GitHub 上提供了仲裁器“簡單實現”、測試平臺和 Modelsim 文件的 VHDL 源代碼

第二種實現——可變大小,固定優先級

上述仲裁器的邏輯是固定大小的。通過一些更改,并通過使用不受約束的端口(查看req和gnt端口),我們可以制作一個通用仲裁器,其大小可以在實現時決定。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter_unc is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector;

busy : in std_logic;

-- outputs

gnt : out std_logic_vector

);

end arbiter_unc;

architecture rtl of arbiter_unc is

signal busy_d : std_logic;

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk)

variable prio_req : std_logic;

begin

if (rising_edge(clk)) then

if (rst = '1') then

gnt <= (others => '0');

else

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

for I in 1 to req'left - 1 loop

prio_req := '0';

for J in 1 to I loop

prio_req := prio_req or req(J - 1);

end loop;

gnt(I) <= req(I) and not prio_req;

end loop;

end if;

end if;

end if;

end process arbiter_pr;

end rtl;

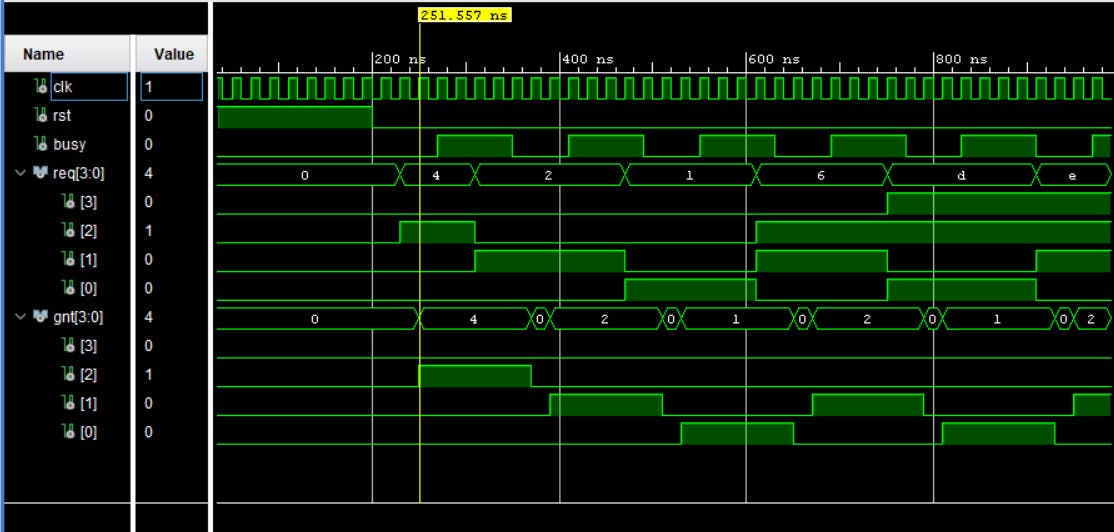

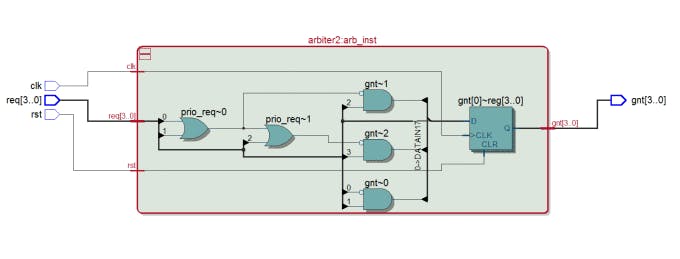

可變大小仲裁器的 Vivado 仿真,實例化為 size = 4

?

?

?

?

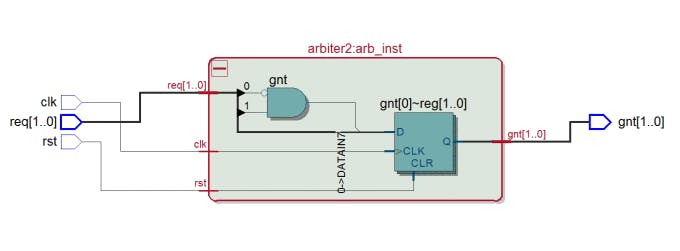

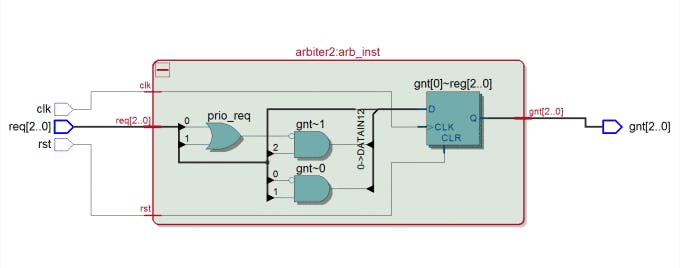

RTL 表示顯示了處理越來越多的端口所需的組合復雜性不斷增加,并且是使用 Quartus Prime 15.1 生成的。請注意,某些塊(如輸出 FF)不是單個而是堆疊的原始實例化。如前所述,如果多個主機請求總線,則編號最小的主機將獲得gnt(回想一下,在任何給定時間只有一個主機應接收gnt)。這個仲裁器有一個固定的優先級。雖然在某些應用程序中可以使用這樣的仲裁器,但最常見的仲裁器類型沒有固定的優先級。我將在以后的文章中討論更復雜的仲裁器(循環法)。

建議練習

- 如前所述,這個簡單的仲裁器具有固定的優先級。如果多個主控斷言它們的請求信號,則編號最小的主控器被賦予gnt。設計一個固定優先級的主機,其中編號最高的主機具有最高優先級。

- 在這個仲裁器中,只要一個主機請求總線,總線就被授予它。添加超時邏輯。如果一個主機斷言req超過 10 個時鐘周期,如果其他請求未完成,則取消斷言對該主機的授權信號。

- 一些仲裁者具有公園功能。Park 的意思是,如果沒有未完成的請求,gnt信號將發送給最后一個接收到它的主機。在另一個版本中,如果沒有主機斷言req,則gnt信號被分配給“默認主機”。為這兩個選項中的每一個選項設計代碼。

GitHub 上提供了仲裁器“無約束實現”、測試平臺和 Modelsim 文件的 VHDL 源代碼

- 開源VHDL驗證方法 (OSVVM) 0次下載

- VHDL測試平臺開源分享

- 開源網絡協議分析器WireShark軟件下載 15次下載

- 基于SaaS的替代性糾紛在線仲裁系統 9次下載

- VHDL最經典的參考指南資料免費下載 36次下載

- VHDL的參考手冊免費下載 34次下載

- VHDL測試平臺編寫綜述 19次下載

- 電梯控制器的VHDL程序與仿真資料合集 11次下載

- 如何進行SOC總線仲裁算法的研究資料說明 5次下載

- 最全面的VHDL例程源碼資料下載 116次下載

- 低功耗應用處理器的特征 3次下載

- PLD Programming Using VHDL 0次下載

- OPB總線仲裁器的RTL設計與FPGA實現

- SOC總線仲裁算法的研究

- PCI總線仲裁器的設計及實現

- Verilog與VHDL的比較 Verilog HDL編程技巧 2.9k次閱讀

- Verilog到VHDL轉換的經驗與技巧總結 4.2k次閱讀

- 例說Verilog HDL和VHDL區別 5.9k次閱讀

- 基于LEON開源微處理器IP軟核實現SoC系統基本平臺的構建 3.5k次閱讀

- 如何在VHDL中解決綜合工具使用轉化問題 3.3k次閱讀

- 基于CPLD器件實現雙主設備PCI總線仲裁器的設計 1.6k次閱讀

- C到VHDL的編譯器設計與實現詳解 5.9k次閱讀

- CAN總線仲裁示意圖_CAN總線位仲裁技術及優缺點 1.8w次閱讀

- vhdl和verilog的區別_vhdl和verilog哪個好? 12.5w次閱讀

- VHDL語言設計四人搶答器(三種設計方案) 3.8w次閱讀

- 基于VHDL的電子計時器的設計方法詳解 2.7w次閱讀

- vhdl按鍵控制數碼管顯示 2.2w次閱讀

- 8位移位寄存器vhdl代碼 1.8w次閱讀

- 我對VHDL的延時理解 4.6k次閱讀

- 基于VHDL的交通燈控制器設計 6.3k次閱讀

下載排行

本周

- 1新一代網絡可視化(NPB 2.0)

- 3.40 MB | 1次下載 | 免費

- 2冷柜-電氣控制系統講解

- 13.68 MB | 1次下載 | 10 積分

- 3MDD品牌三極管MMBT3906數據手冊

- 2.33 MB | 次下載 | 免費

- 4MDD品牌三極管S9012數據手冊

- 2.62 MB | 次下載 | 免費

- 5LAT1218 如何選擇和設置外部晶體適配 BlueNRG-X

- 0.60 MB | 次下載 | 3 積分

- 6LAT1216 Blue NRG-1/2 系列芯片 Flash 操作與 BLE 事件的互斥處理

- 0.89 MB | 次下載 | 3 積分

- 7收音環繞擴音機 AVR-1507手冊

- 2.50 MB | 次下載 | 免費

- 8MS1000TA 超聲波測量模擬前端芯片技術手冊

- 0.60 MB | 次下載 | 免費

本月

- 1愛華AIWA HS-J202維修手冊

- 3.34 MB | 37次下載 | 免費

- 2PC5502負載均流控制電路數據手冊

- 1.63 MB | 23次下載 | 免費

- 3NB-IoT芯片廠商的資料說明

- 0.31 MB | 22次下載 | 1 積分

- 4UWB653Pro USB口測距通信定位模塊規格書

- 838.47 KB | 5次下載 | 免費

- 5蘇泊爾DCL6907(即CHK-S007)單芯片電磁爐原理圖資料

- 0.04 MB | 4次下載 | 1 積分

- 6蘇泊爾DCL6909(即CHK-S009)單芯片電磁爐原理圖資料

- 0.08 MB | 2次下載 | 1 積分

- 7100W準諧振反激式恒流電源電路圖資料

- 0.09 MB | 2次下載 | 1 積分

- 8FS8025B USB的PD和OC快充協議電壓誘騙控制器IC技術手冊

- 1.81 MB | 1次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935137次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關降壓/升壓雙向直流/直流轉換器 PCB layout 設計

- 1.48MB | 420064次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233089次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191439次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183353次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81602次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73822次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65991次下載 | 10 積分

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論