74ls160設(shè)計(jì)數(shù)字秒表方案匯總(一)

現(xiàn)場(chǎng)可編程門陣列(簡(jiǎn)稱 FPGA)是20 世紀(jì) 80 年代中期出現(xiàn)的高密度可編程邏輯器件,采用SRAM開關(guān)元件的 FPGA 是易失性的,每次重新加電,F(xiàn)PGA 都要重新裝入配置數(shù)據(jù)。突出優(yōu)點(diǎn)是可反復(fù)編程,系統(tǒng)上電時(shí),給 FPGA 加載不同的配置數(shù)據(jù),即可令其完成不同的硬件功能。這種配置的改變甚至可以在系統(tǒng)的運(yùn)行中進(jìn)行,實(shí)現(xiàn)系統(tǒng)功能的動(dòng)態(tài)重構(gòu)。

“在系統(tǒng)可編程”(簡(jiǎn)稱 ISP)是指對(duì)器件、電路或整個(gè)電子系統(tǒng)的邏輯功能可隨時(shí)進(jìn)行修改或重構(gòu)的能力,支持 ISP 技術(shù)的可編程邏輯器件稱為在系統(tǒng)可編程邏輯器件,它不需要專門的編程器,利用計(jì)算機(jī)接口和一根下載電纜就可以對(duì)器件編程了。

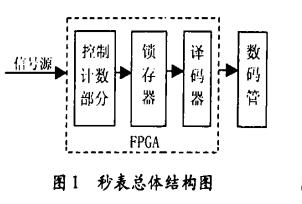

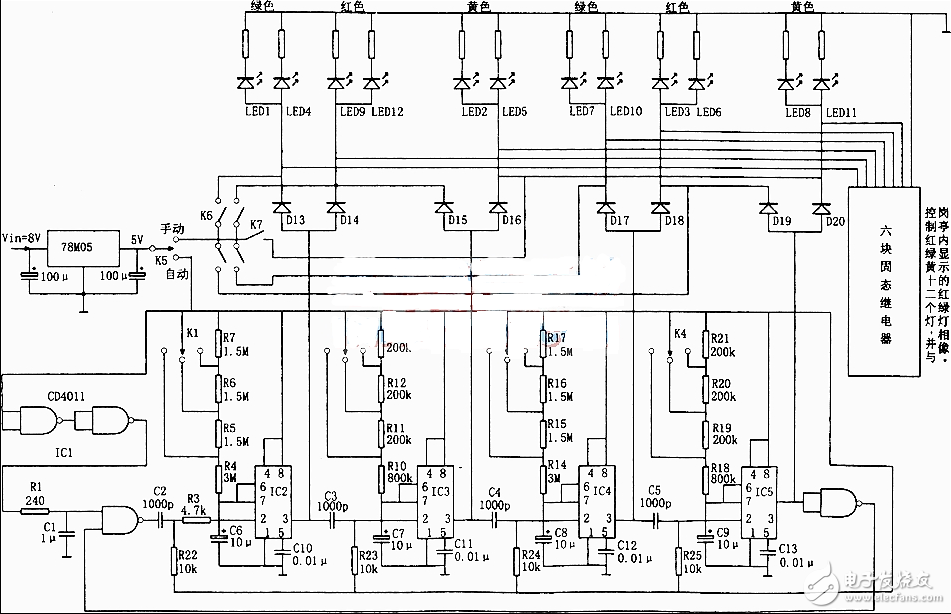

1、總體結(jié)構(gòu)

本文利用 EDA 技術(shù)中的 Max + plus Ⅱ作為開發(fā)工具,設(shè)計(jì)了一款基于 FPGA 的數(shù)字式秒表 ,并下載到在系統(tǒng)可編程實(shí)驗(yàn)板的 EPF10K10LC84 - 4 器件中測(cè)試實(shí)現(xiàn)。其總體結(jié)構(gòu)框架如圖1 所示。圖中的信號(hào)源是由實(shí)驗(yàn)板上的時(shí)鐘信號(hào)經(jīng)分頻而得到的 0. 1 秒信號(hào);控制計(jì)數(shù)部分由一個(gè)計(jì)數(shù)模塊 ctrl 構(gòu)成,用來實(shí)現(xiàn)計(jì)時(shí)功能,鎖存器模塊 latch 用來對(duì)數(shù)據(jù)進(jìn)行鎖存 ;而譯碼器模塊 DISP 用來對(duì)計(jì)數(shù)結(jié)果進(jìn)行掃描譯碼;數(shù)碼管用來顯示秒表的工作結(jié)果。

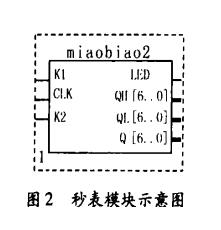

圖2為數(shù)字式秒表的模塊示意圖。輸入信號(hào)有三個(gè),分別是 K1 , K2 和 CLK;輸出信號(hào)有四個(gè),分別是 LED ,QH[ 6. 。 0 ] ,QL[6. 。 0 ] 及 Q[ 6. 。 0 ]。其中 K1 為“開始/ 清零鍵”,接的是控制計(jì)數(shù)部分的整體清零端,該清零信號(hào)低電平有效。要求按下 K1 時(shí)計(jì)時(shí)開始 ,再按一下,停止計(jì)時(shí),恢復(fù)到零狀態(tài)。K2 為“固定顯示鍵”,接的是鎖存器 74373 的允許鎖存端 G,該信號(hào)是高電平有效。在計(jì)時(shí)過程中,按下 K2 時(shí),鎖存數(shù)據(jù) ,顯示固定 ,但計(jì)時(shí)仍繼續(xù) ;按第二下時(shí) ,顯示從新時(shí)間開始。CLK 為時(shí)鐘信號(hào) ,必須是秒表計(jì)時(shí)所需的最小單位 0. 1S。

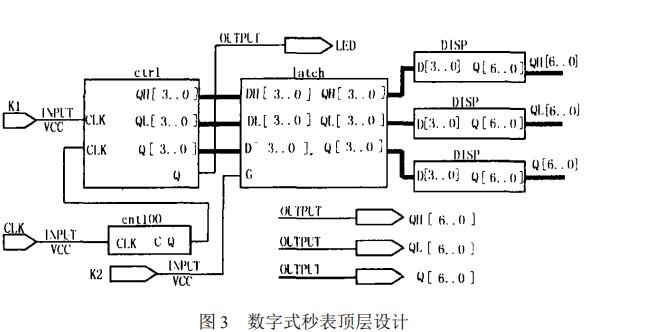

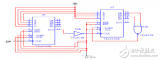

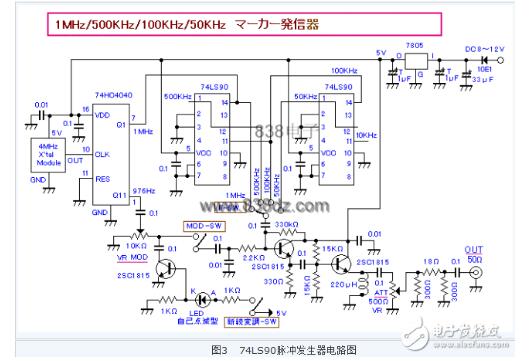

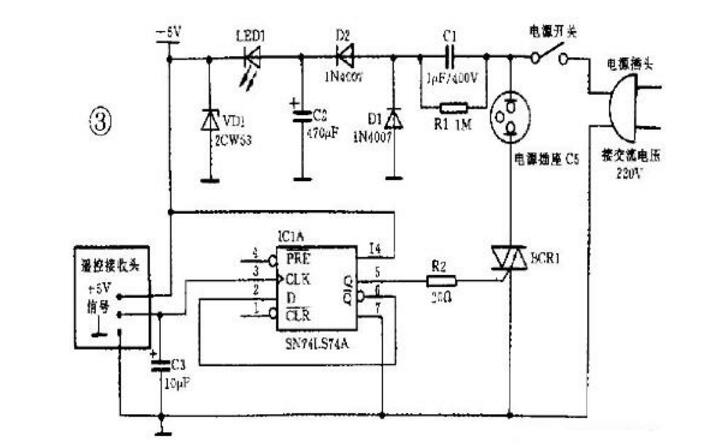

QH[6. 。 0 ] ,QL[6. 。 0 ] 及 Q[6. 。 0 ] 接三個(gè)數(shù)碼管,分別表示秒十位,秒個(gè)位和秒十分位。LED 接發(fā)光二極管用來表示秒表的分位,當(dāng)秒表計(jì)時(shí)超過59. 9 秒時(shí) LED 燈亮,且能持續(xù)表示到 1分 59. 9 秒,然后燈滅,同時(shí)數(shù)碼管重新計(jì)時(shí)顯示,即該數(shù)字式秒表的計(jì)時(shí)范圍從0 到2 分鐘。基于原理圖編輯和VHDL語言,并使用從上到下的設(shè)計(jì)方法設(shè)計(jì)的秒表,其具體的線路構(gòu)成如圖3 所示。

在總體電路圖中,根據(jù)設(shè)計(jì)要求,輸入信號(hào) K1、K2 應(yīng)采用脈沖開關(guān)。由于實(shí)驗(yàn)板上除了撥動(dòng)開關(guān)就是瞬時(shí)的按鍵開關(guān),且按鍵開關(guān)平時(shí)都呈高電平,按一下為低電平。故在實(shí)際測(cè)試時(shí)采用了撥動(dòng)開關(guān)來模擬脈沖開關(guān)。根據(jù)設(shè)計(jì)要求將K1、K2 平時(shí)置于相應(yīng)的高、低電平狀態(tài),需要清零或固定顯示時(shí)再將它們分別置于相應(yīng)的位置上即可。

3、模塊設(shè)計(jì)

在設(shè)計(jì)電路時(shí),要遵循從上到下的設(shè)計(jì)原則。首先從系統(tǒng)設(shè)計(jì)入手,在頂層進(jìn)行功能劃分和結(jié)構(gòu)設(shè)計(jì),頂層模塊中的每個(gè)次層模塊均可完成一個(gè)較為獨(dú)立的功能,次模塊在調(diào)試成功后可生成一個(gè)默認(rèn)符號(hào),以供上一層模塊調(diào)用。

3. 1、時(shí)鐘信號(hào)模塊 cnt100

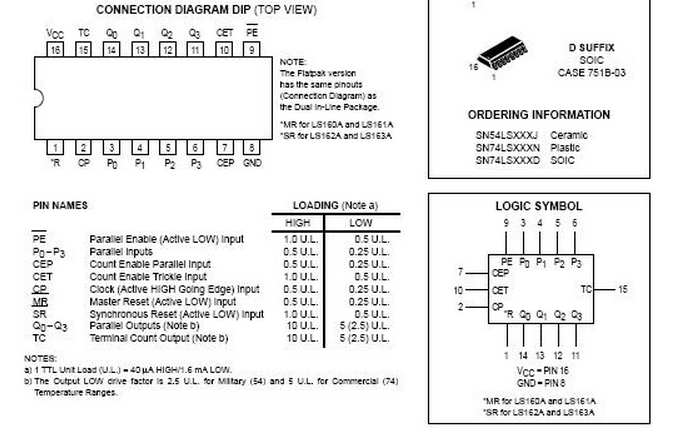

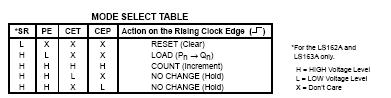

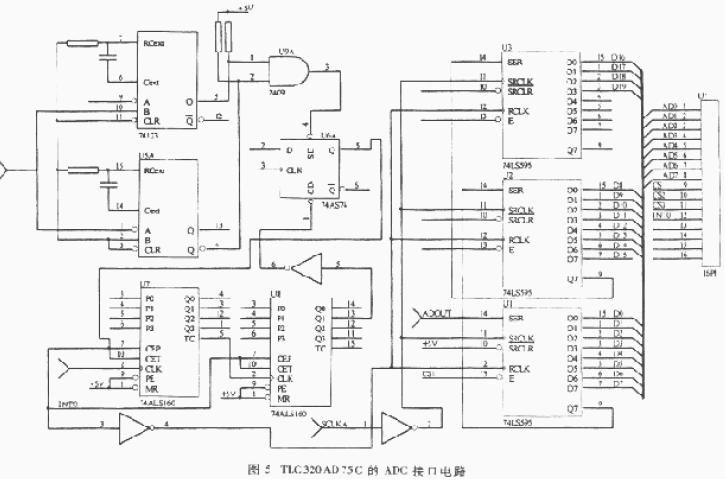

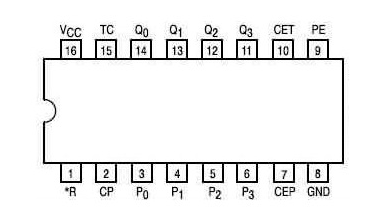

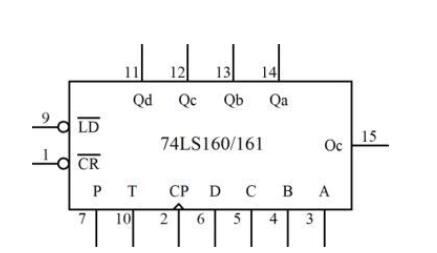

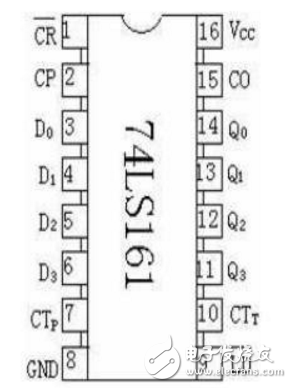

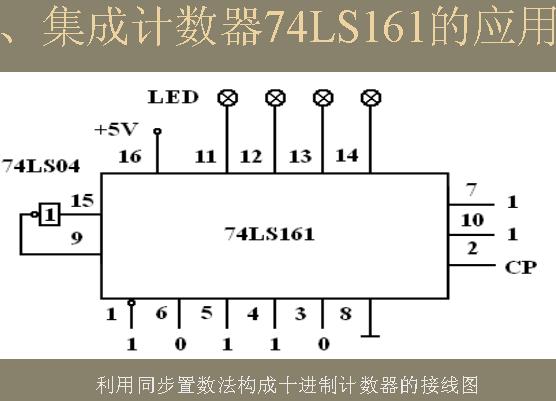

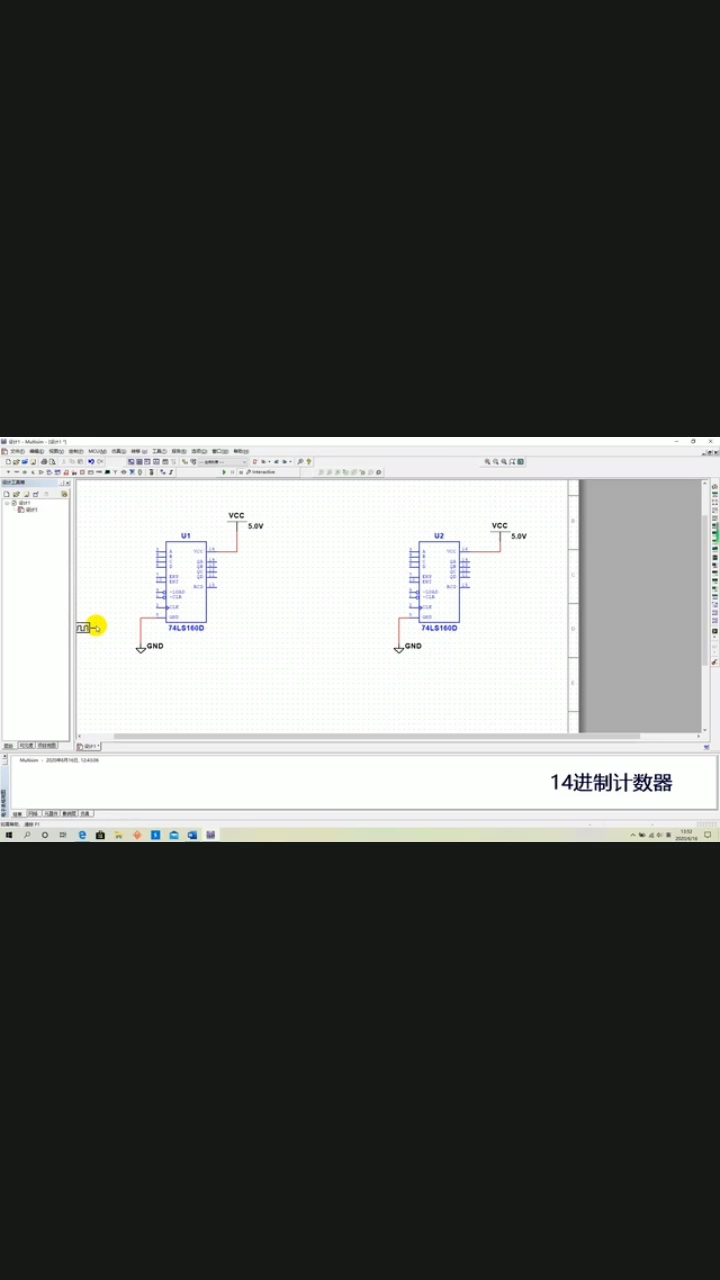

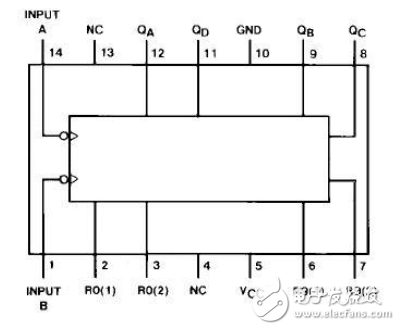

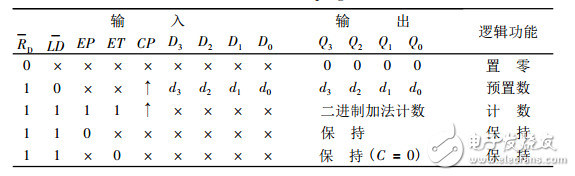

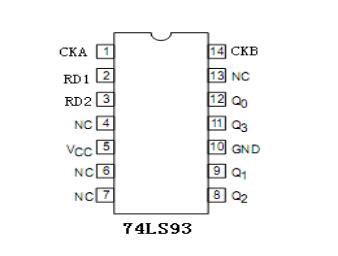

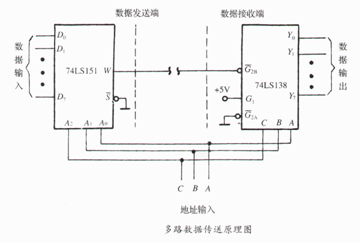

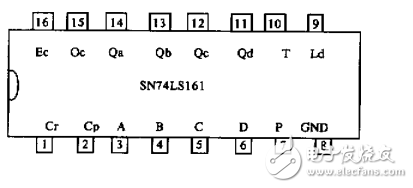

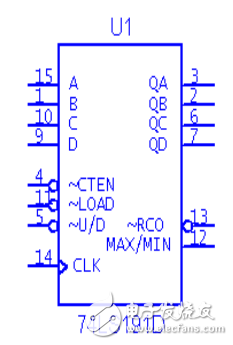

由于最終的設(shè)計(jì)結(jié)果要下載到可編程邏輯器件中測(cè)試,而承載該芯片的“在系統(tǒng)”可編程實(shí)驗(yàn)板上最小也是1 kHz 的時(shí)鐘源,而秒表計(jì)時(shí)所需的最小單位為 0. 1s,故采用 2 片 74160,利用并行輸入方式,接成 100 進(jìn)制計(jì)數(shù)器(00~99),將 1 kHz 信號(hào)變成 10 Hz (即 0. 1 s),從而達(dá)到分頻的目的。編譯通過后創(chuàng)建的默認(rèn)符號(hào)為 cnt100,其輸入信號(hào)為 CLK,輸出信號(hào)為 CQ(即高位的進(jìn)位端 RCO) 。

3. 2、控制計(jì)時(shí)模塊 ctrl

從 Maxplus2 器件庫(kù)中調(diào)用 3 片 74160,采用串行時(shí)鐘方式,連接成六百進(jìn)制計(jì)數(shù)器(即 0~599),用來表示秒位。將 3 片 74160 的清零端 CLR 連接在一起,用來做秒表的整體清零端。再調(diào)用器件庫(kù)中的 J K觸發(fā)器,連接相應(yīng)控制端形成 T′觸發(fā)器,將六百進(jìn)制計(jì)數(shù)器的進(jìn)位信號(hào)接 T′觸發(fā)器的時(shí)鐘端。平時(shí)其輸出端 Q 保持低電平,所接發(fā)光二極管不亮 ;當(dāng)計(jì)時(shí)到 59. 9 秒時(shí),由于有進(jìn)位信號(hào)到來,因此時(shí)鐘端出現(xiàn)脈沖下降沿,觸發(fā)器翻轉(zhuǎn),Q 由低電平變?yōu)楦唠娖剑l(fā)光二極管點(diǎn)亮,表示已計(jì)時(shí)到 1 分鐘。再計(jì)到 1分 59. 9 秒時(shí),過 1 秒,燈滅,同時(shí)數(shù)碼管重新計(jì)時(shí)顯示。該控制模塊為圖 3 中 ctrl 模塊。

3. 3、鎖存器模塊 latch

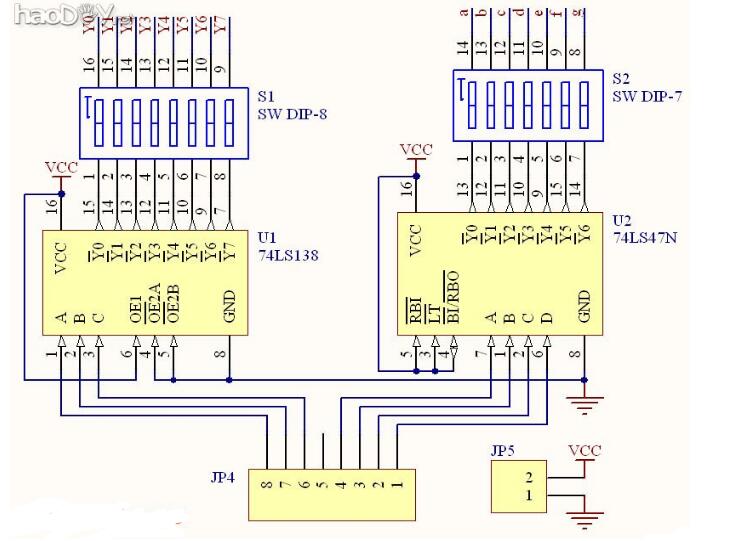

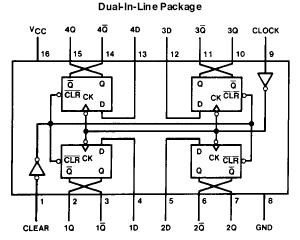

因?yàn)槊氡碓O(shè)計(jì)中要求在計(jì)時(shí)過程中能隨時(shí)固定顯示時(shí)間,而計(jì)時(shí)仍然繼續(xù),所以要用到鎖存器。在本例中適宜采用 CD4511 芯片,因?yàn)樗狭随i存、譯碼和驅(qū)動(dòng)功能。但由于 Maxplus2 器件庫(kù)中沒有此類芯片,故以鎖存器 74373 外加譯碼器 7447 (DISP) 代替。在設(shè)計(jì)時(shí)從器件庫(kù)中調(diào)用 2 片 74373 (8 位鎖存器), 將它們的 OEN 統(tǒng)統(tǒng)接低電平,允許數(shù)據(jù)輸出。G端接一起,作為允許數(shù)據(jù)鎖存端 (高電平有效) 。鎖存器部分編譯通過后創(chuàng)建的默認(rèn)符號(hào)見圖 3 中的 latch 模塊,輸入信號(hào)有四個(gè),分別是 DH[ 3. 。 0 ] 、DL[3. 。 0 ] 、D[3. 。 0 ] 及 G,輸出有三個(gè),分別是 QH[3. 。 0 ] 、QL[3. 。 0 ]及 Q[3. 。 0 ] 。

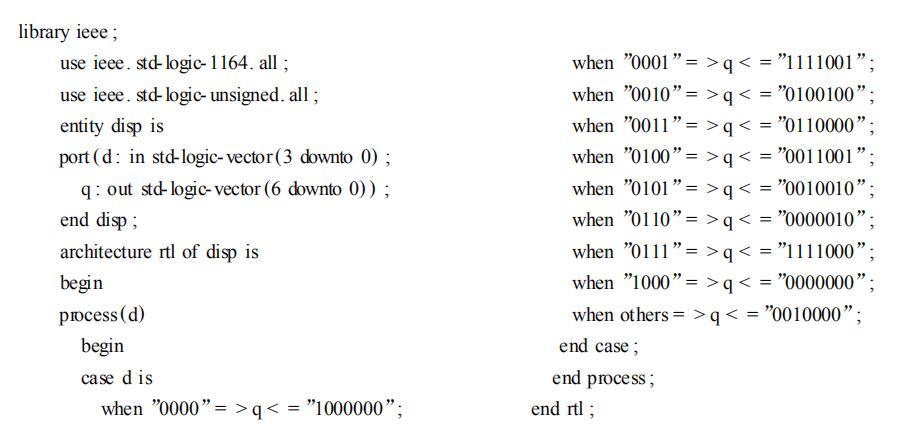

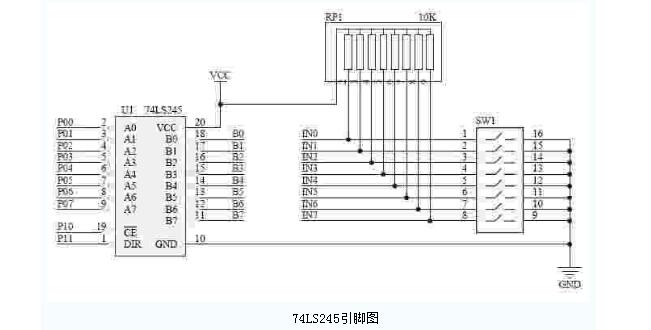

3. 4、譯碼顯示模塊 DISP

譯碼器可直接從器件庫(kù)中調(diào)用 7447 (共陽極譯碼器),將它的控制端按要求接好,形成默認(rèn)符號(hào) ;也可用 VHDL 語言編程,將 4 位 BCD 碼譯成 7 段數(shù)碼管的編碼(0~9),現(xiàn)采用 VHDL 語言編程,編譯無誤后創(chuàng)建默認(rèn)文件符號(hào) DISP 以供上層電路調(diào)用。顯示部分直接采用實(shí)驗(yàn)板上的 3 個(gè)共陽極數(shù)碼管,不用將譯碼器的輸出 a~g 具體連線到實(shí)驗(yàn)板上數(shù)碼管的 7 個(gè)段,只需將其輸出端口定義到可用作數(shù)碼管顯示的器件的 I/ O 引腳上即可。7 段數(shù)碼管譯碼器源程序如下

4、編程及測(cè)試

為設(shè)計(jì)項(xiàng)目選定 FLEX10K系列中的 EPF10K10LC84 - 4 器件,鎖定頂層設(shè)計(jì)中各端口所對(duì)應(yīng)的引腳號(hào),并編譯通過。然后對(duì)器件編程,使用 ByteBlaste 下載電纜把項(xiàng)目以在線配置的方式下載到 ISP 實(shí)驗(yàn)板的 EPF10K10LC84 - 4 器件中,按相應(yīng)的 K1、K2 鍵,觀測(cè)數(shù)碼管及發(fā)光二極管的狀態(tài),發(fā)現(xiàn)顯示結(jié)果正確。該數(shù)字式秒表具有清零功能,能夠在計(jì)時(shí)過程中隨時(shí)停止計(jì)時(shí),恢復(fù)到初始狀態(tài)。且具有鎖存/ 計(jì)時(shí)功能,能在計(jì)時(shí)過程中通過按“固定顯示鍵”,將顯示固定住,而計(jì)時(shí)仍繼續(xù) ;再按下鍵,顯示從新時(shí)間開始。實(shí)驗(yàn)證明該秒表工作正常,基本上已達(dá)到了預(yù)期的設(shè)計(jì)要求。

5、結(jié)束語

在Max + plus Ⅱ開發(fā)環(huán)境下,采用自頂向下的設(shè)計(jì)方法有利于在早期發(fā)現(xiàn)結(jié)構(gòu)設(shè)計(jì)中的錯(cuò)誤,避免不必要的重復(fù)設(shè)計(jì)。再結(jié)合基于 FPGA 的“在系統(tǒng)”可編程實(shí)驗(yàn)板,輕輕松松就能實(shí)現(xiàn)各種電子產(chǎn)品的設(shè)計(jì),現(xiàn)場(chǎng)觀察實(shí)驗(yàn)測(cè)試結(jié)果。大大縮短了產(chǎn)品的設(shè)計(jì)周期和調(diào)試周期,提高了設(shè)計(jì)的可靠性和成功率,充分體現(xiàn)了可編程邏輯器件在數(shù)字電路設(shè)計(jì)中的優(yōu)越性。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論